# TPS659119-Q1 汽车类集成电源管理单元顶层规范

## 1 特性

- 符合汽车应用要求

- 具有符合 AEC-Q100 的下列结果:

- 器件温度 3 级: -40°C 至 85°C 的环境运行温度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级 2

- 器件充电器件模型 (CDM) ESD 分类等级 C4B

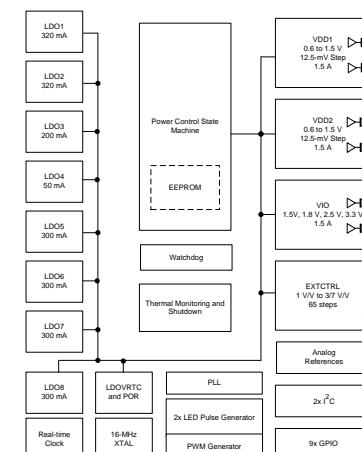

- 支持 EEPROM 可编程性的嵌入式电源控制器 (EPC)

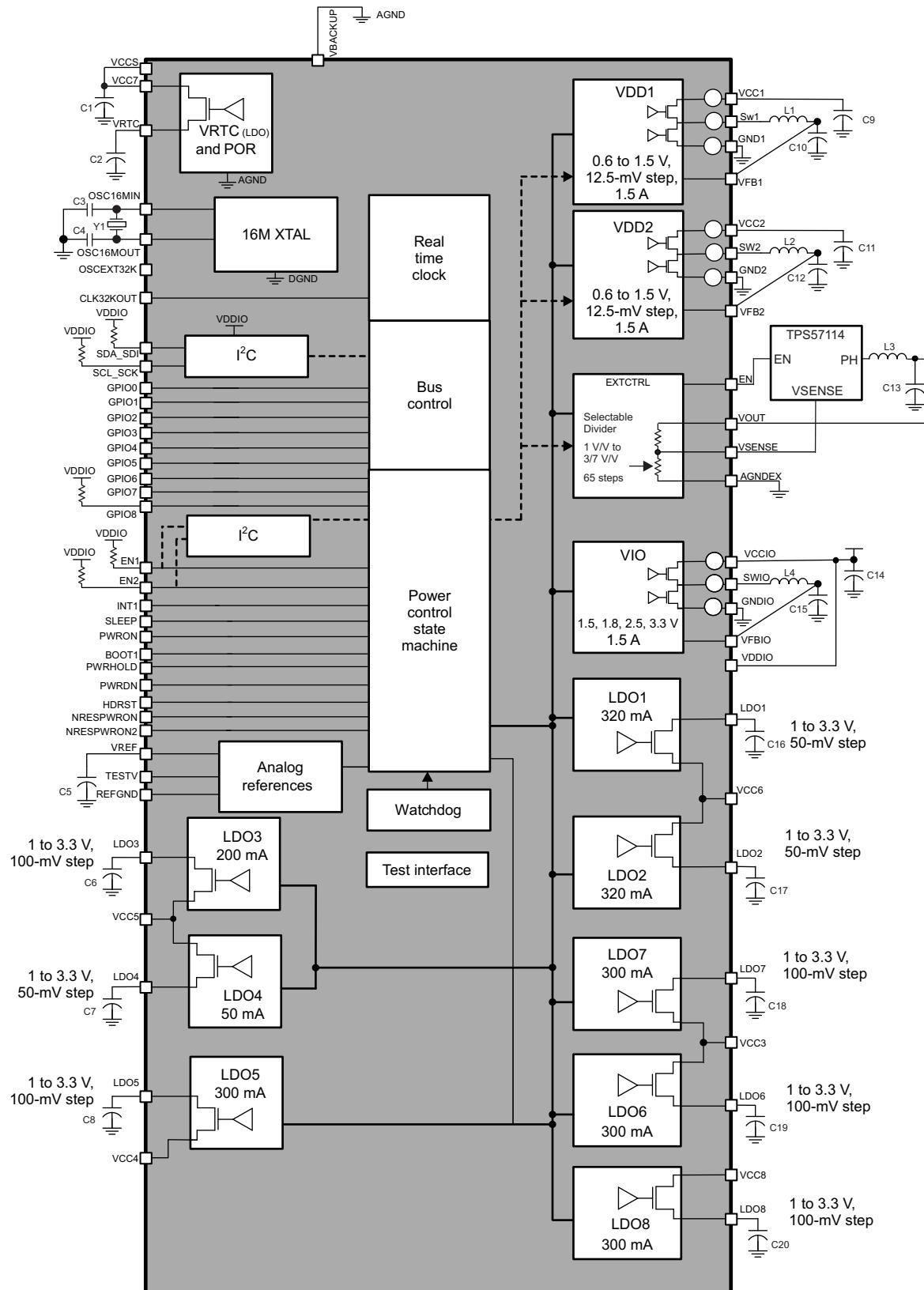

- 两个用于处理器内核 (VDD1, VDD2) 且支持动态电压调节的高效降压直流到直流 (DC-DC) 转换器

- 一个用于 I/O 电源 (VIO) 的高效降压 DC-DC 转换器

- 一个控制外部 DCDC 转换器 (EXTCTRL) 的接口

- 8 个低压降 (LDO) 电压稳压器和 1 个实时时钟 (RTC) LDO (为内部 RTC 供电)

- 一个高速 I<sup>2</sup>C 通用控制命令接口 (CTL-I<sup>2</sup>C)

- 两个用于控制电源的独立使能信号 (EN1, EN2), 此信号可被用作一个高速 I<sup>2</sup>C 接口, 专门用于 VDD1 和 VDD2 电压调节。

- 热关断保护和热模检测

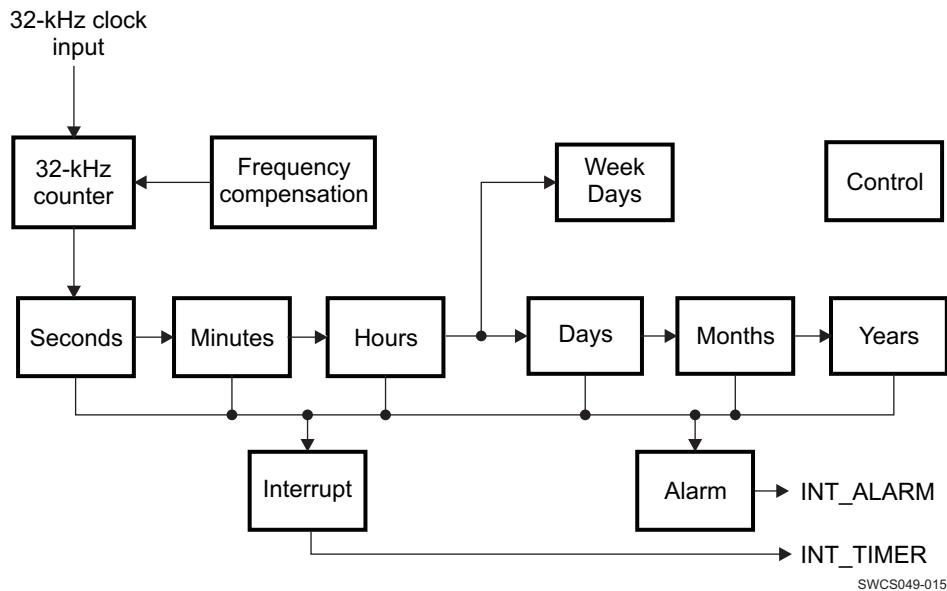

- 一个具有以下资源的实时时钟 (RTC):

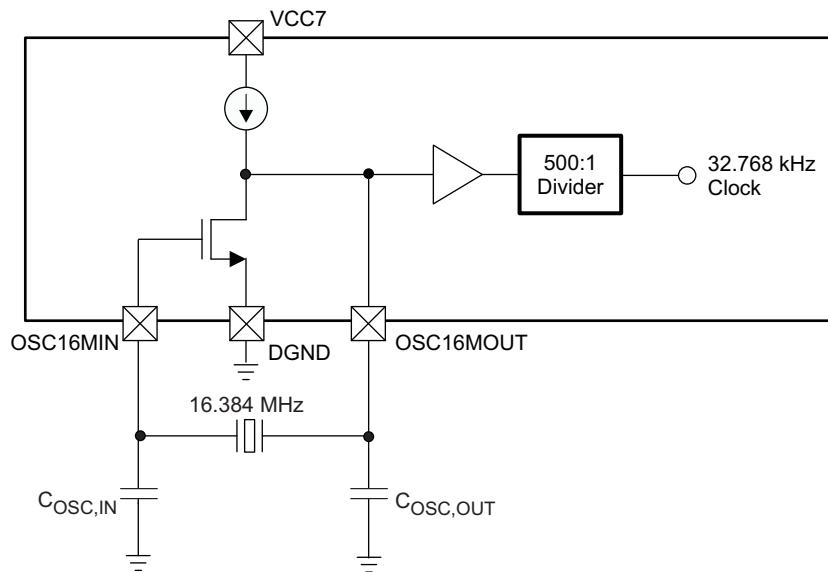

- 快速启动 16.384MHz 晶体振荡器

- 由晶体振荡器、外部 32kHz 时钟或内部 32kHz RC 振荡器供源的可配置时钟源

- 日期、时间和日历

- 闹铃功能

- 9 个支持复用特性的可配置通用输入输出 (GPIO) 接口:

- 其中 4 个可针对外部资源启用, 包括在加电序列之中并由状态机控制

- 作为 GPI, GPIO 支持逻辑电平检测并可针对唤醒生成可屏蔽中断

- 其中的 2 个 GPIO 具有驱动 LED 所需的 10mA 电流吸收能力

- 通过一个外部 3MHz 时钟实现的 DCDC 开关同步

- 两个用于冷复位 (HDRST) 的复位输入和一个用于热复位输入的电源初始化复位 (PWRDN)

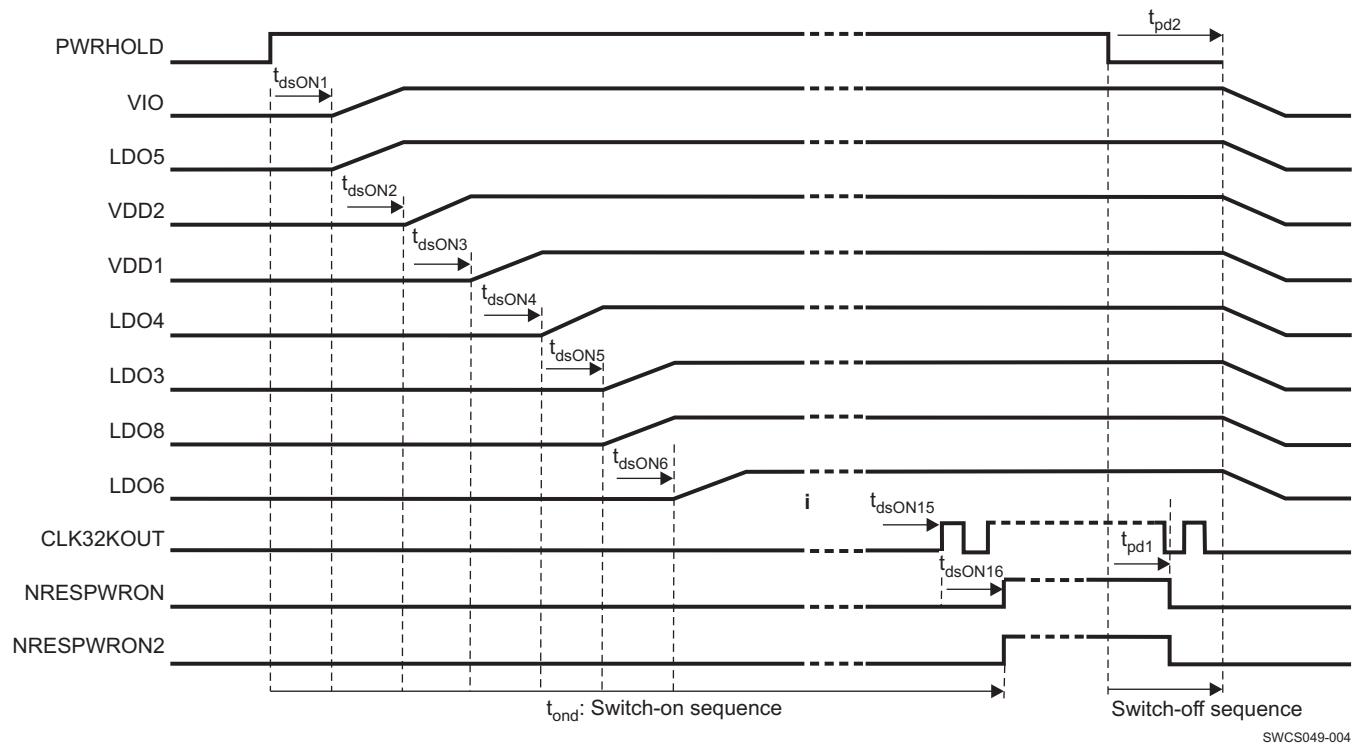

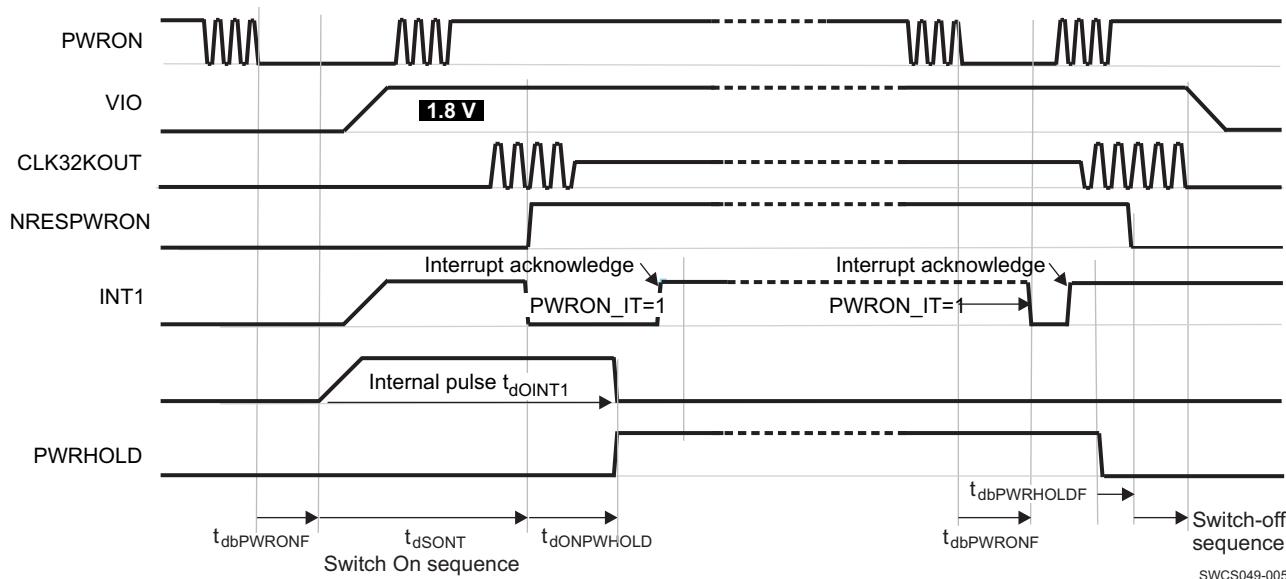

- 包括在电源序列表的 32kHz 时钟输出

(CLK32KOUT) 和系统复位 (NRESPWRON)

- 安全装置

- 两个开关状态 LED 脉冲发生器和一个脉宽调制 (PWM) 发生器

## 2 应用范围

- 汽车

- 信息娱乐

- 自动数据采集 (ADA)

- 组合仪表

## 3 说明

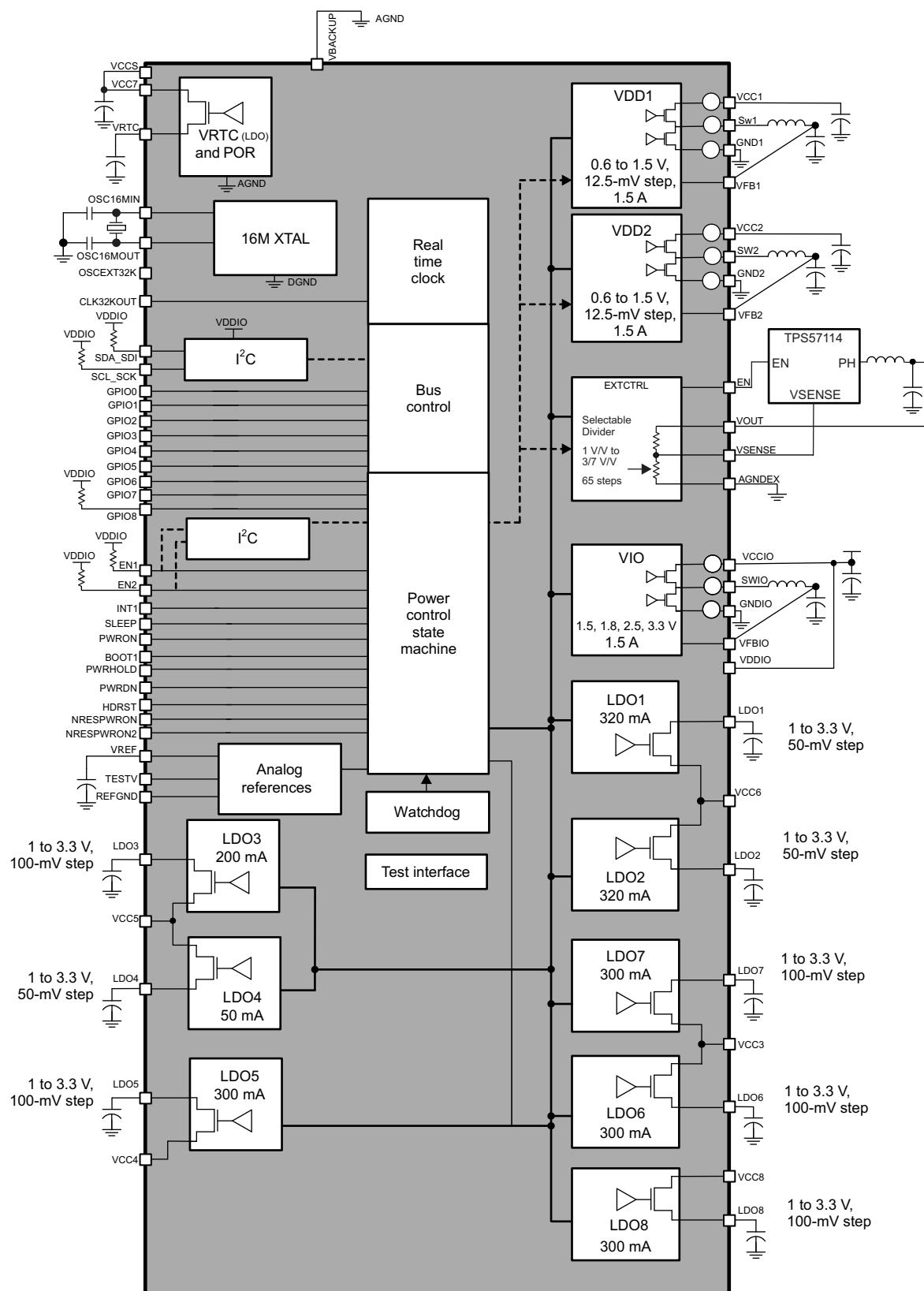

TPS659119-Q1 器件是一款集成型电源管理 IC, 专用于所搭载应用处理器需要多个电源轨的系统。此器件提供三个降压转换器、一个用于控制外部转换器的接口以及 8 个 LDO, 可灵活用于支持不同的处理器和应用。

其中两个降压转换器为双处理器内核供电, 并支持通过专用的 I<sup>2</sup>C 接口动态调节电压, 从而实现最优节能。

第 3 个转换器为系统中的输入和输出 (I/O) 以及存储器供电。通过控制外部转换器可以针对系统中的高电流轨对外部转换器电压进行排序和调节。

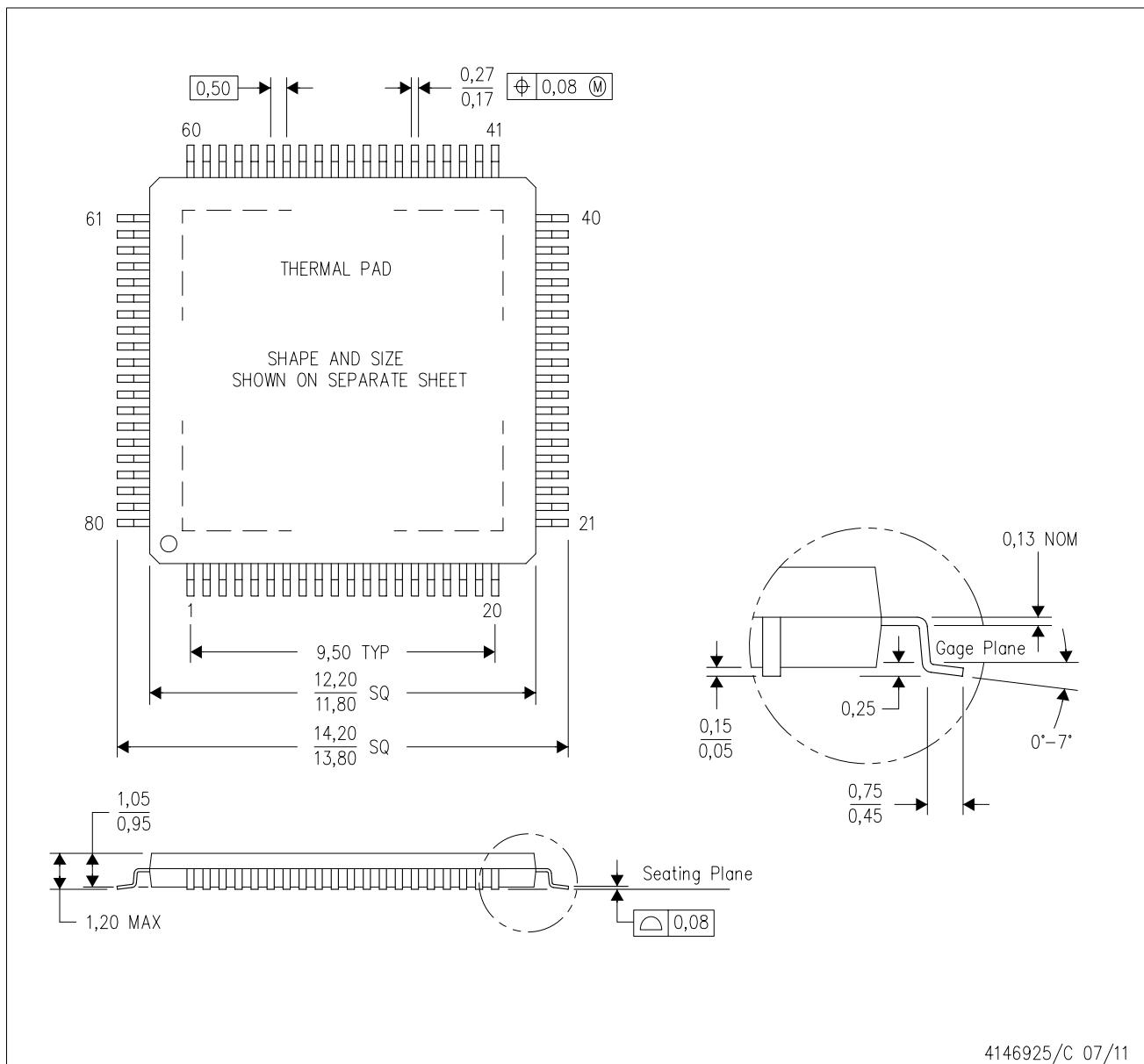

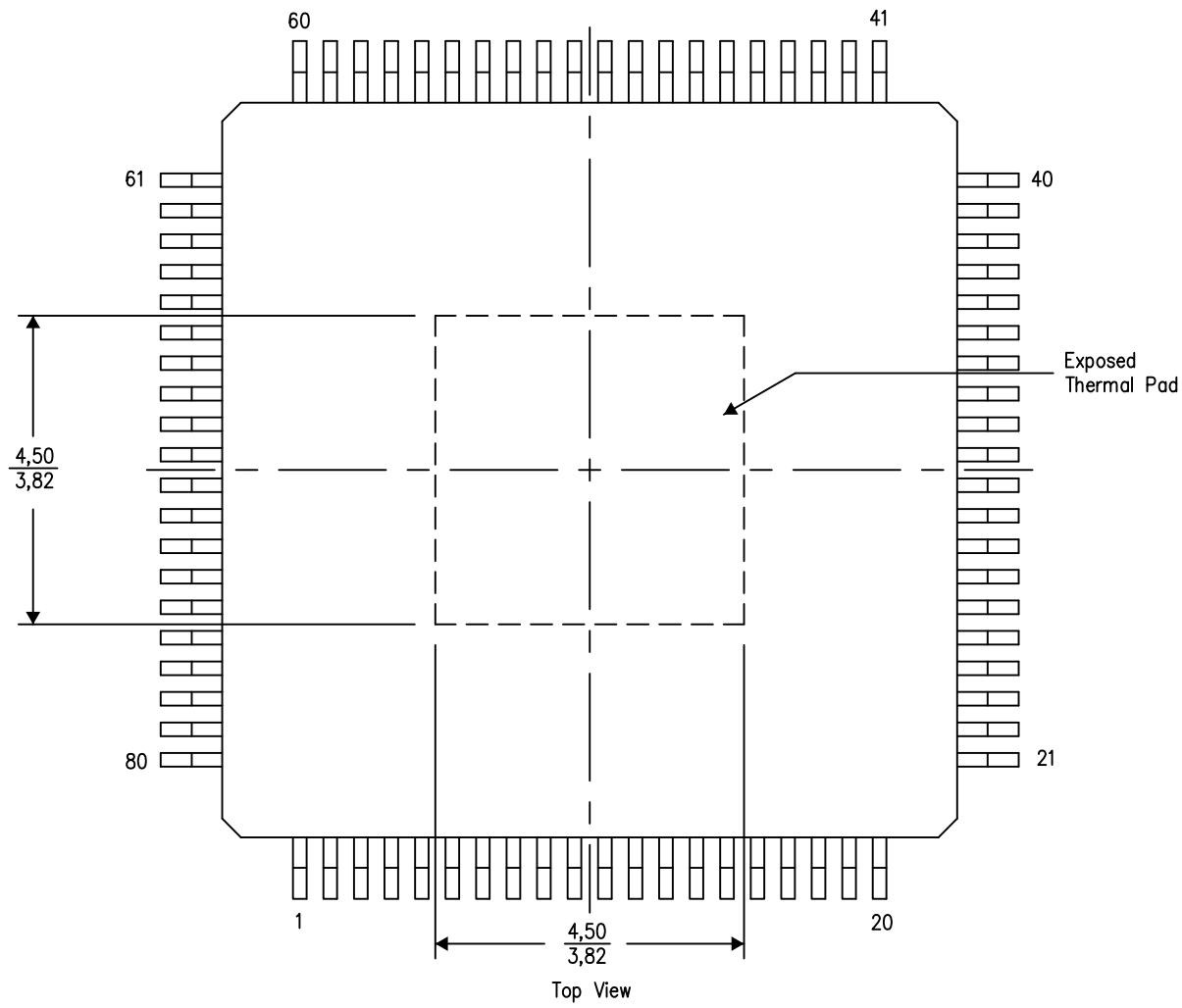

### 器件信息<sup>(1)</sup>

| 部件号          | 封装         | 封装尺寸 (标称值)        |

|--------------|------------|-------------------|

| TPS659119-Q1 | HTQFP (80) | 12.00mm x 12.00mm |

(1) 要了解所有可用封装, 请见数据表末尾的可订购产品附录。

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of the Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

English Data Sheet: SWCS106

## 目 录

|      |                                                                                |     |

|------|--------------------------------------------------------------------------------|-----|

| 1    | 特性 .....                                                                       | 1   |

| 2    | 应用范围 .....                                                                     | 1   |

| 3    | 说明 .....                                                                       | 1   |

| 4    | 修订历史记录 .....                                                                   | 2   |

| 5    | 说明 (继续) .....                                                                  | 4   |

| 6    | Pin Configuration and Functions .....                                          | 4   |

| 7    | Specifications .....                                                           | 7   |

| 7.1  | Absolute Maximum Ratings .....                                                 | 7   |

| 7.2  | Handling Ratings .....                                                         | 7   |

| 7.3  | Recommended Operating Conditions .....                                         | 8   |

| 7.4  | Thermal Characteristics .....                                                  | 8   |

| 7.5  | External Component Recommendation .....                                        | 8   |

| 7.6  | I/O Pullup and Pulldown Characteristics .....                                  | 10  |

| 7.7  | Digital I/O Voltage Electrical Characteristics .....                           | 10  |

| 7.8  | I <sup>2</sup> C Interface and Control Signals .....                           | 12  |

| 7.9  | Switching Characteristics—I <sup>2</sup> C Interface and Control Signals ..... | 12  |

| 7.10 | Power Consumption .....                                                        | 13  |

| 7.11 | Power References and Thresholds .....                                          | 13  |

| 7.12 | Thermal Monitoring and Shutdown .....                                          | 13  |

| 7.13 | 32-kHz RTC Clock .....                                                         | 14  |

| 7.14 | VRTC LDO .....                                                                 | 15  |

| 7.15 | VIO SMPS .....                                                                 | 15  |

| 7.16 | VDD1 SMPS .....                                                                | 16  |

| 7.17 | VDD2 SMPS .....                                                                | 17  |

| 7.18 | EXTCTRL .....                                                                  | 19  |

| 7.19 | LDO1 AND LDO2 .....                                                            | 20  |

| 7.20 | LDO3 and LDO4 .....                                                            | 22  |

| 7.21 | LDO5 .....                                                                     | 24  |

| 7.22 | LDO6 and LDO7 .....                                                            | 25  |

| 7.23 | LDO8 .....                                                                     | 27  |

| 7.24 | Timing Requirements for Boot Sequence Example .....                            | 28  |

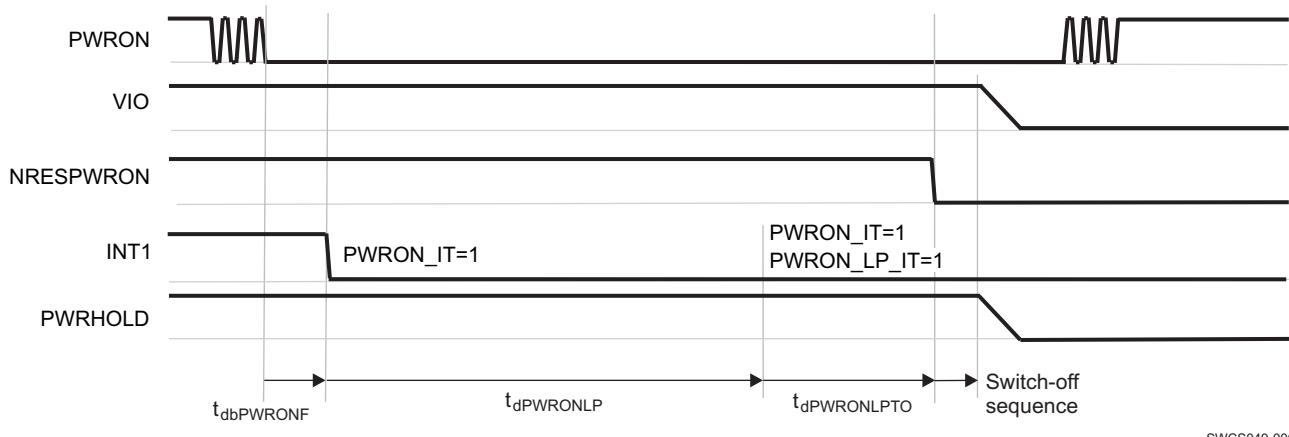

| 7.25 | Power Control Timing Requirements .....                                        | 28  |

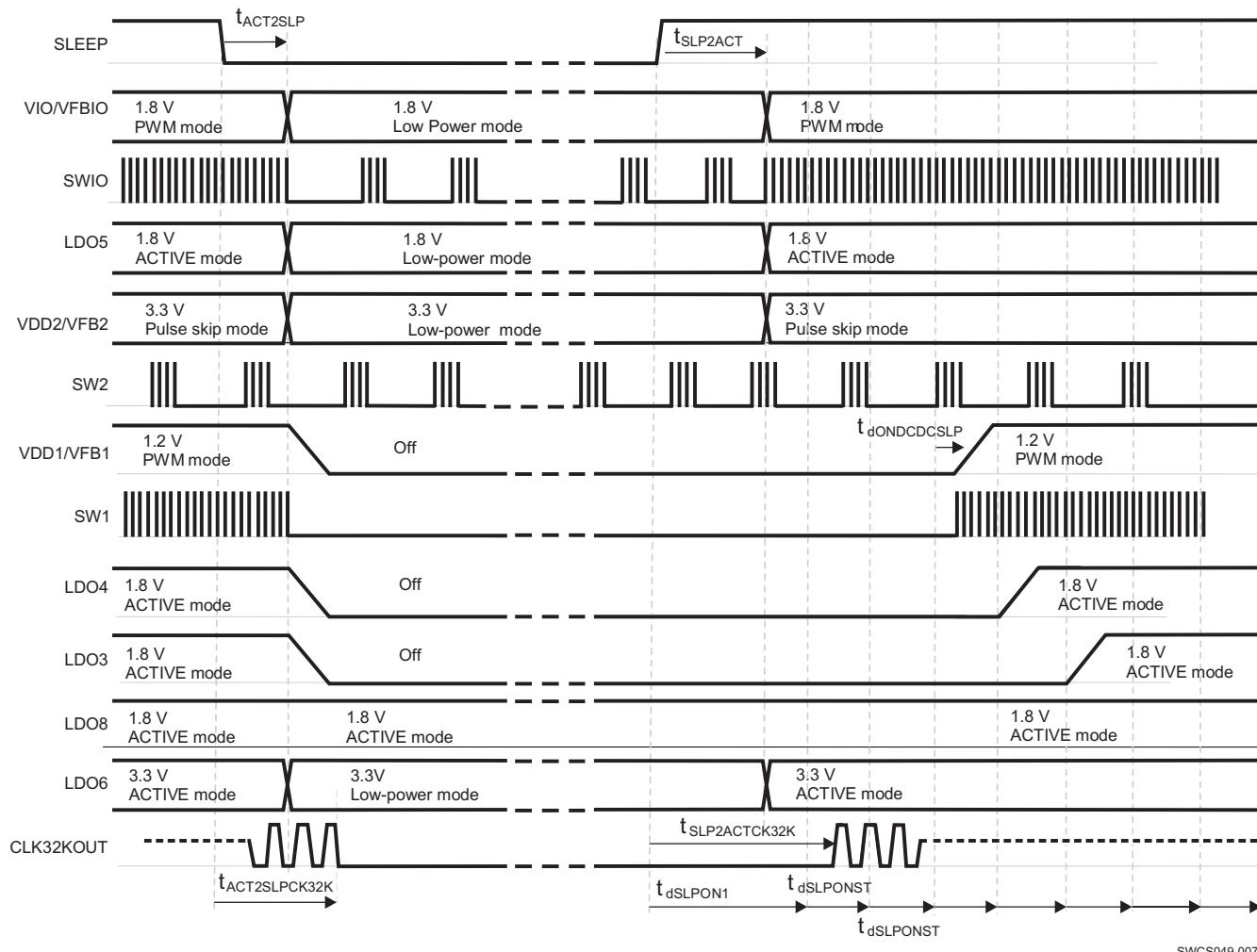

| 7.26 | Device SLEEP State Control Timing Requirements .....                           | 29  |

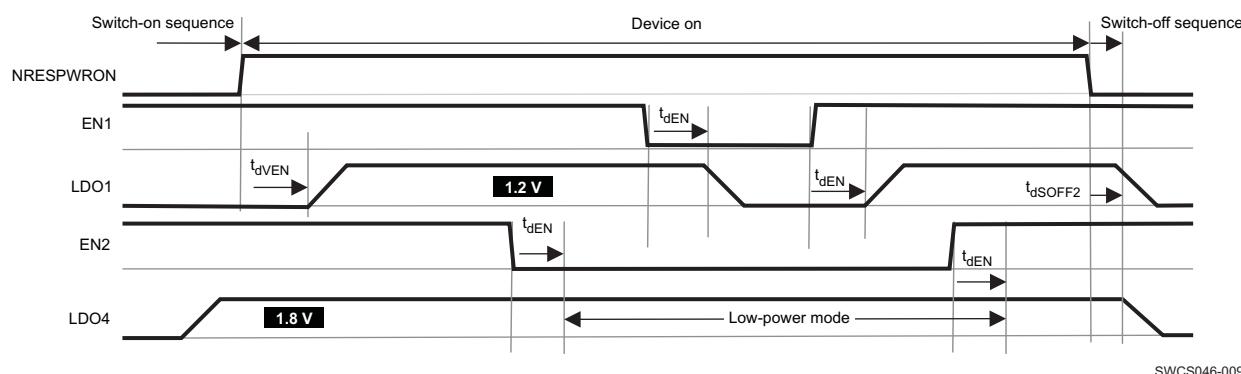

| 7.27 | Supplies State Control Through EN1 and EN2 Timing Characteristics .....        | 29  |

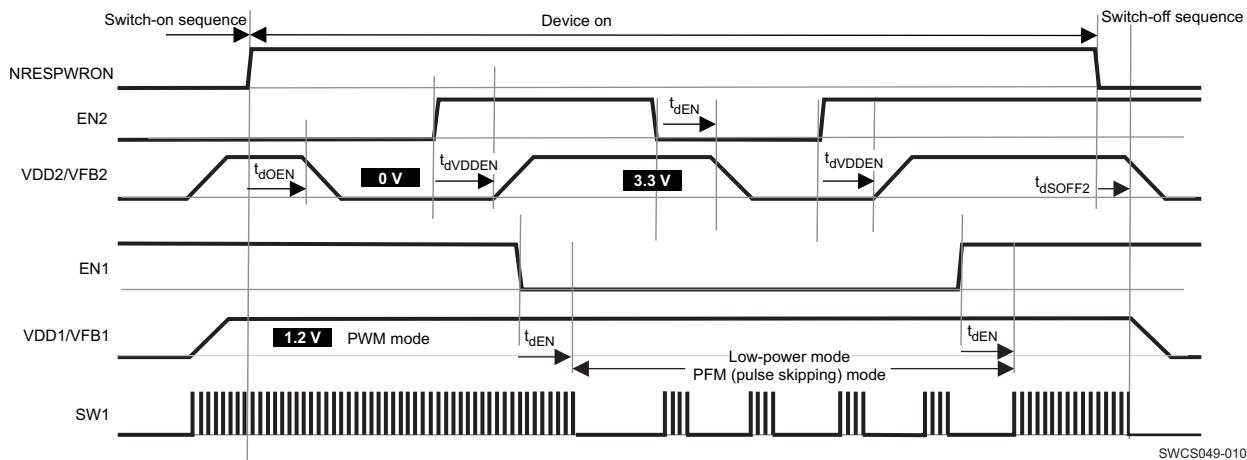

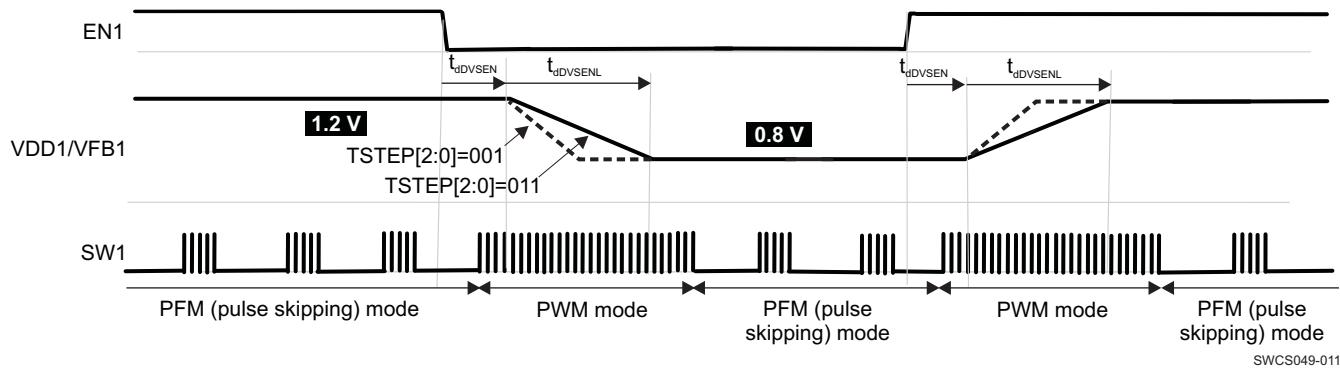

| 7.28 | VDD1 Supply Voltage Control Through EN1 Timing Requirements .....              | 29  |

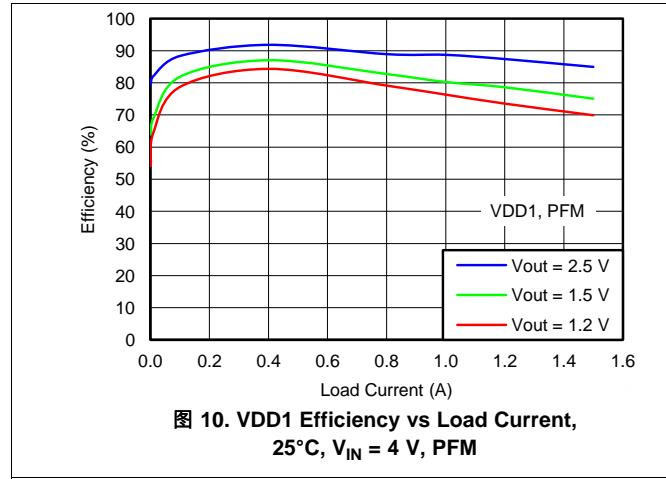

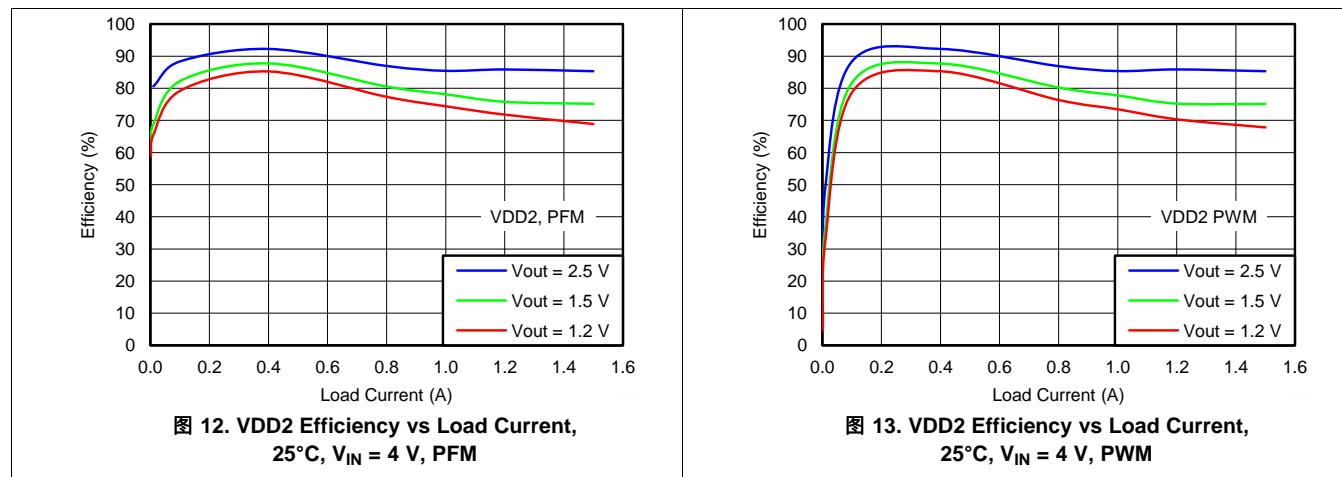

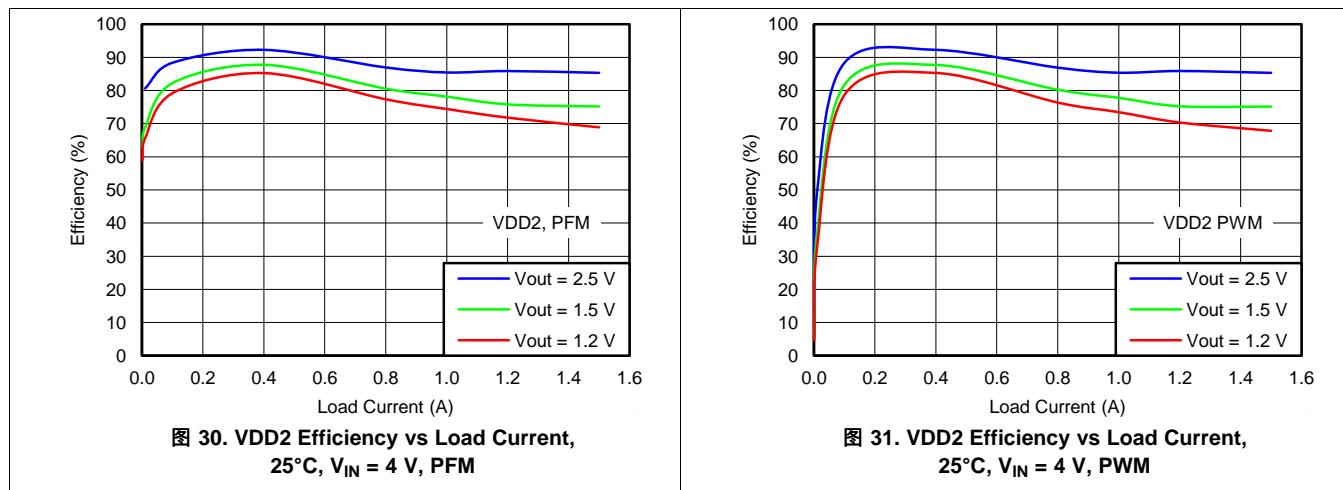

| 7.29 | Typical Characteristics .....                                                  | 34  |

| 8    | Detailed Description .....                                                     | 36  |

| 8.1  | Overview .....                                                                 | 36  |

| 8.2  | Functional Block Diagram .....                                                 | 37  |

| 8.3  | Feature Description .....                                                      | 38  |

| 8.4  | Device Functional Modes .....                                                  | 42  |

| 8.5  | Programming .....                                                              | 54  |

| 8.6  | Register Maps .....                                                            | 58  |

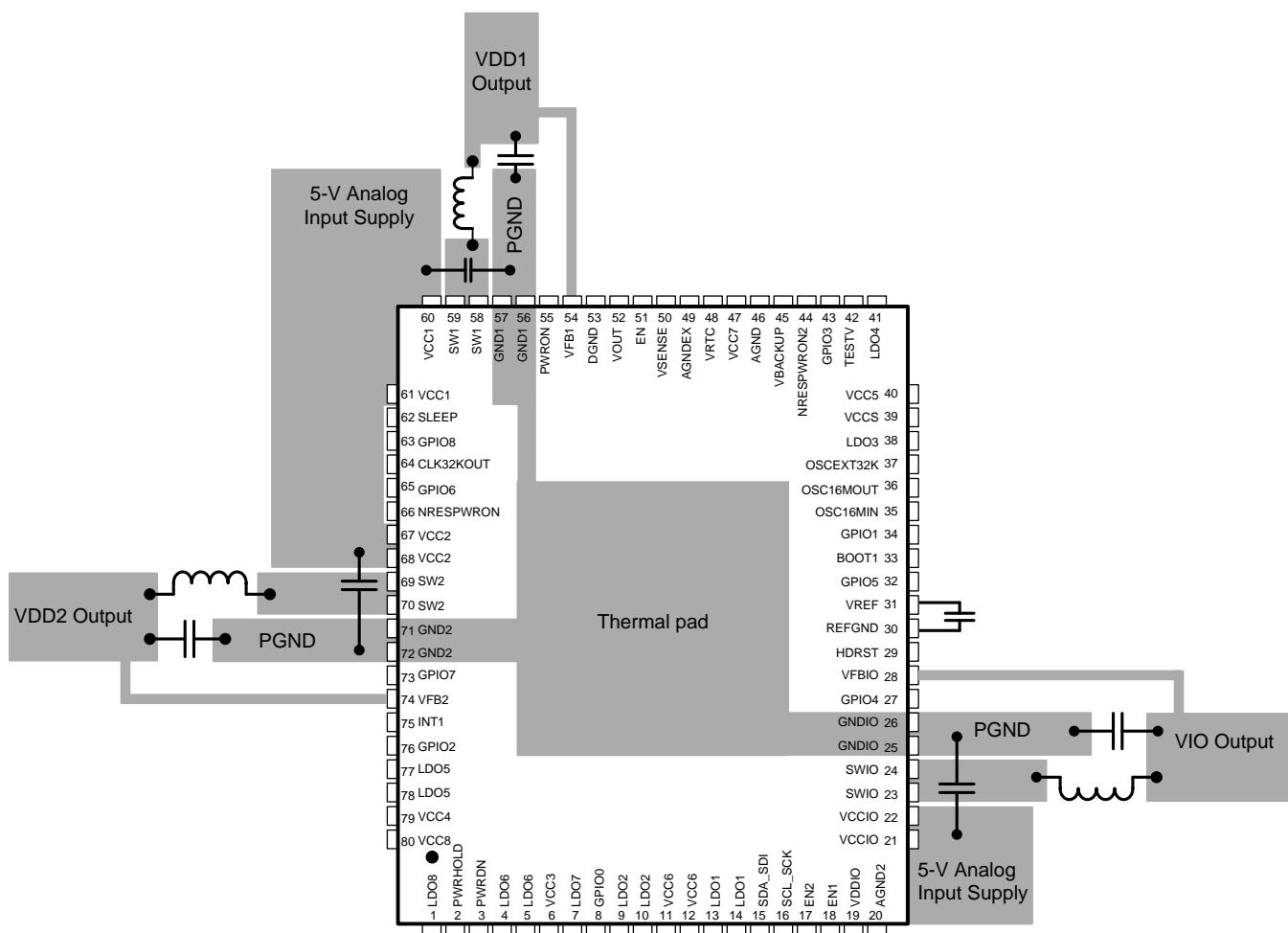

| 9    | Application and Implementation .....                                           | 117 |

| 9.1  | Application Information .....                                                  | 117 |

| 9.2  | Typical Application .....                                                      | 117 |

| 10   | Power Supply Recommendations .....                                             | 121 |

| 11   | Layout .....                                                                   | 121 |

| 11.1 | Layout Guidelines .....                                                        | 121 |

| 11.2 | Layout Example .....                                                           | 122 |

| 12   | 器件和文档支持 .....                                                                  | 123 |

| 12.1 | 器件支持 .....                                                                     | 123 |

| 12.2 | 商标 .....                                                                       | 123 |

| 12.3 | 静电放电警告 .....                                                                   | 123 |

| 12.4 | 术语表 .....                                                                      | 124 |

| 13   | 机械封装和可订购信息 .....                                                               | 124 |

## 4 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision D (July 2014) to Revision E                                                                                                                                           | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • Updated the PSKIP rows for the TPS659119KBIPFPRQ1 in the EEPROM Configuration table .....                                                                                                 | 49   |

| • 已添加 column for TPS659119LBIPFP to and removed the TOP-SIDE MARKING row from the EEPROM CONFIGURATION table in the BOOT CONFIGURATION AND SWITCH-ON AND SWITCH-OFF SEQUENCES section ..... | 49   |

| Changes from Revision C (August 2013) to Revision D                                                                                                                                | Page |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| • 已更改 CDM 分类等级从 C4A 更改为 C4B，且更新了 CDM ESD 额定值以包含边角引脚值以及其它引脚值 .....                                                                                                                  | 1    |

| • 更新了数据表格式以包含新文档流程和以下新增条目：器件信息表、概述部分、应用和实施部分、电源相关建议部分、布局部分、器件和文档支持部分（目前包含词汇表）以及机械、封装和可订购信息部分。另外还删除了附录 A：功能寄存器并将寄存器映射和说明移动到了详细说明部分 .....                                            | 1    |

| • Deleted the PARAMETER and TEST CONDITION column headings from the Absolute Maximum Ratings, Recommended Operating Conditions, and External Component Recommendation tables ..... | 7    |

| • Moved storage temperature range and ESD ratings from the Absolute Maximum Ratings table into the new Handling Ratings table .....                                                | 7    |

| • Changed the TYP column to NOM in the Recommended Operating Conditions table .....                                                                                                | 7    |

| • Replaced Characteristics with Requirements in all timing table titles .....                                                                                                      | 7    |

---

|                                                                                                                                                                                   |     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • Split the DC output parameter for each LDO into output voltage, step size, and output accuracy and removed multiple TYP values .....                                            | 7   |

| • 已添加 column for TPS659119KBIPFP (top-side marking) to the <i>EEPROM CONFIGURATION</i> table in the <i>BOOT CONFIGURATION AND SWITCH-ON AND SWITCH-OFF SEQUENCES</i> section..... | 49  |

| • 已添加 pullup resistors to VDDIO on the I <sup>2</sup> C pins in the <i>Application Schematic</i> image.....                                                                       | 118 |

| • 已添加 在文档末尾的封装选项附录以及封装材料信息页面 .....                                                                                                                                                | 123 |

---

| Changes from Revision B (April 2013) to Revision C                              | Page |

|---------------------------------------------------------------------------------|------|

| • Added Storage Temperature range to <i>ABSOLUTE MAXIMUM RATINGS</i> table..... | 7    |

---

| Changes from Revision A (April 2013) to Revision B                                      | Page |

|-----------------------------------------------------------------------------------------|------|

| • Changed 0x20 to 0x22 for TPS659119HAIPFPRQ1 column in EEPROM Configuration table..... | 49   |

---

## 5 说明 (继续)

此器件还包含 8 个通用 LDO，能够提供大范围的电压和电流能力。其中 5 个 LDO 支持 1 至 3.3V (步长 100mV)，而其它 3 个 LDO 支持 1 至 3.3V (步长 50mV)。所有 LDO 均可由 I<sup>2</sup>C 接口完全控制。

除了电源稳压器，此器件还包含九个具有复用功能的可配置 GPIO，用于支持广泛的功能。此器件中还包含一个嵌入式电源控制器，用于管理系统的上电排序要求。电源排序由 EEPROM 设定。

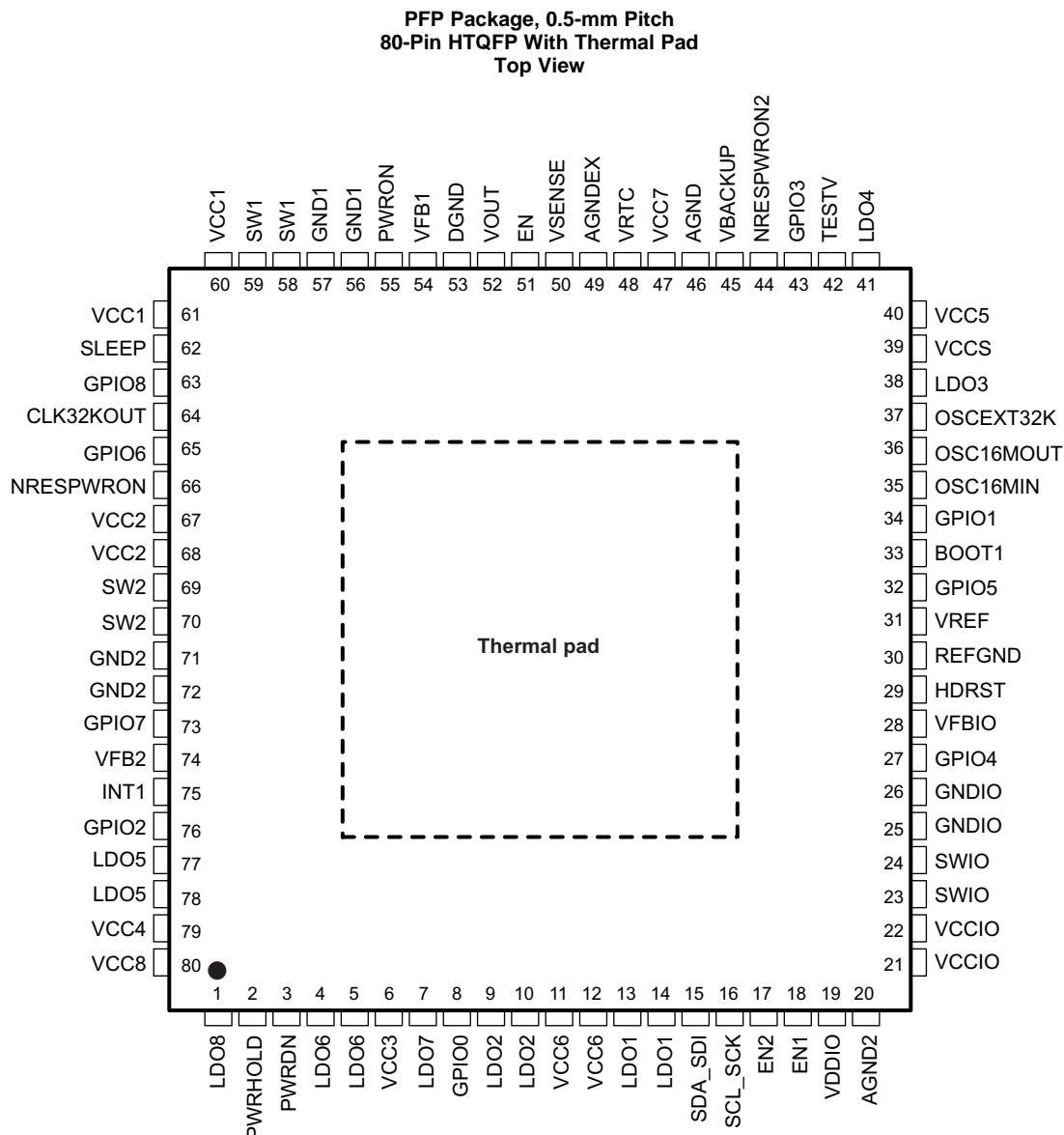

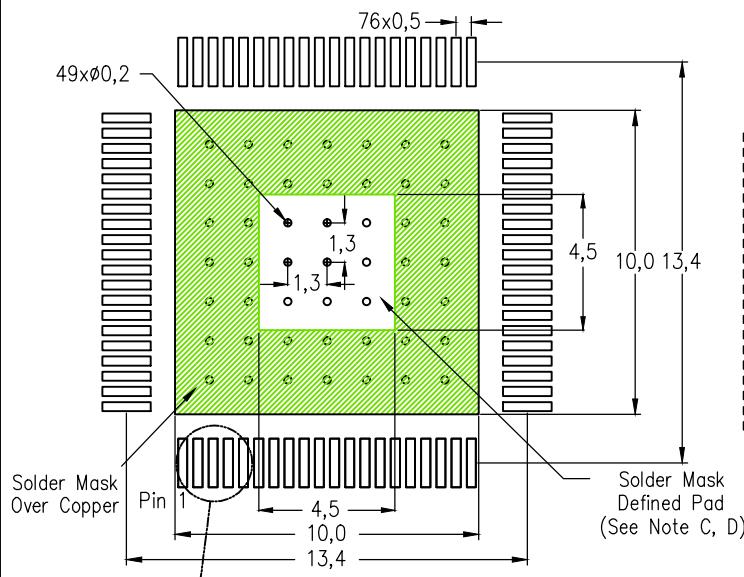

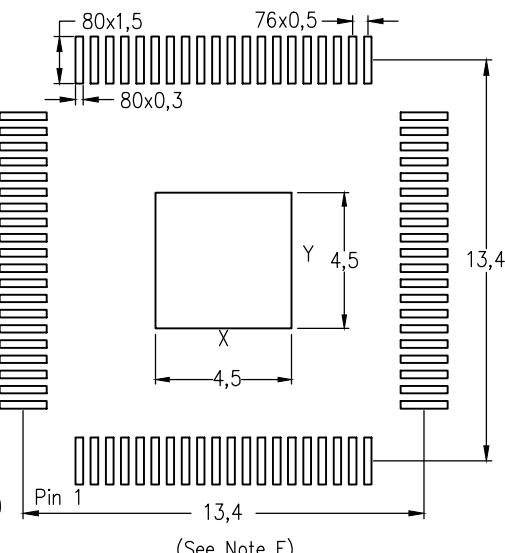

## 6 Pin Configuration and Functions

**Pin Functions**

| PIN       |     | TYPE    | I/O | DESCRIPTION                                                                                           | SUPPLIES     | PU / PD                          |

|-----------|-----|---------|-----|-------------------------------------------------------------------------------------------------------|--------------|----------------------------------|

| NAME      | NO. |         |     |                                                                                                       |              |                                  |

| LDO8      | 1   | Power   | O   | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 $\mu$ A                     |

| PWRHOLD   | 2   | Digital | I   | Switch-on, switch off control signal and GPI                                                          | VRTC, DGND   | Programmable PD (default active) |

| PWRDN     | 3   | Analog  | I   | Reset input, for example, thermal reset                                                               | VRTC, DGND   | PD                               |

| LDO6      | 4   | Power   | O   | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 $\mu$ A                     |

|           | 5   |         |     |                                                                                                       |              |                                  |

| VCC3      | 6   | Power   | I   | LDO6 and LDO7 power Input                                                                             | VCC3, AGND2  | No                               |

| LDO7      | 7   | Power   | O   | LDO regulator output                                                                                  | VCC3, REFGND | PD 5 $\mu$ A                     |

| GPIO0     | 8   | Digital | I/O | GPIO, push pull and OD as output                                                                      | VCC7, DGND   | OD: external PU                  |

| LDO2      | 9   | Power   | O   | LDO regulator output                                                                                  | VCC6, REFGND | No                               |

|           | 10  |         |     |                                                                                                       |              |                                  |

| VCC6      | 11  | Power   | I   | LDO1, LDO2 power Input                                                                                | VCC6, AGND2  | No                               |

|           | 12  |         |     |                                                                                                       |              |                                  |

| LDO1      | 13  | Power   | O   | LDO regulator output                                                                                  | VCC6, REFGND | No                               |

|           | 14  |         |     |                                                                                                       |              |                                  |

| SDA_SDI   | 15  | Digital | I/O | I <sup>2</sup> C bidirectional-data signal and serial-peripheral-interface data input (multiplexed)   | VDDIO, DGND  | External PU                      |

| SCL_SCK   | 16  | Digital | I/O | I <sup>2</sup> C bidirectional-clock signal and serial-peripheral-interface clock input (multiplexed) | VDDIO, DGND  | External PU                      |

| EN2       | 17  | Digital | I/O | Enable for supplies and voltage scaling dedicated to I <sup>2</sup> C data                            | VDDIO, DGND  | External PU                      |

| EN1       | 18  | Digital | I/O | Enable for supplies and voltage scaling dedicated to I <sup>2</sup> C clock                           | VDDIO, DGND  | External PU                      |

| VDDIO     | 19  | Power   | I   | Digital I/O supply                                                                                    | VDDIO, DGND  | No                               |

| AGND2     | 20  | Power   | I/O | Analog ground                                                                                         | AGND2        | No                               |

| VCCIO     | 21  | Power   | I   | VIO DC-DC power Input                                                                                 | VCCIO, GNDIO | No                               |

|           | 22  |         |     |                                                                                                       |              |                                  |

| SWIO      | 23  | Power   | O   | VIO DC-DC switched output                                                                             | VCCIO, GNDIO | No                               |

|           | 24  |         |     |                                                                                                       |              |                                  |

| GNDIO     | 25  | Power   | I/O | VIO DC-DC power ground                                                                                | VCCIO, GNDIO | No                               |

|           | 26  |         |     |                                                                                                       |              |                                  |

| GPIO4     | 27  | Digital | I/O | GPIO                                                                                                  | VRTC, DGND   | OD: External PU                  |

|           |     |         | OD  |                                                                                                       |              |                                  |

| VFBIO     | 28  | Analog  | I   | VIO feedback voltage                                                                                  | VCC7, DGND   | PD 5 $\mu$ A                     |

| HDRST     | 29  | Digital | I   | Cold reset                                                                                            | VRTC, DGND   | PD                               |

| REFGND    | 30  | Analog  | I/O | Reference ground                                                                                      | REFGND       | No                               |

| VREF      | 31  | Analog  | O   | Bandgap voltage                                                                                       | VCC7, REFGND | No                               |

| GPIO5     | 32  | Digital | I/O | GPIO                                                                                                  | VRTC, DGND   | OD: external PU                  |

|           |     |         | OD  |                                                                                                       |              |                                  |

| BOOT1     | 33  | Digital | I   | Power-up sequence selection                                                                           | VRTC, DGND   | No                               |

| GPIO1     | 34  | Digital | I/O | GPIO and LED1 output                                                                                  | VRTC, DGND   | OD: External PU                  |

|           |     |         | OD  |                                                                                                       |              |                                  |

| OSC16MIN  | 35  | Analog  | I   | 16.384-MHz crystal oscillator input                                                                   | VCC7, DGND   | External PD if not in use        |

| OSC16MOUT | 36  | Analog  | O   | 16.384-MHz crystal oscillator output                                                                  | VCC7, DGND   | No                               |

| OSCEXT32K | 37  | Digital | I   | External 32-kHz clock input                                                                           | VRTC, DGND   | External PD if not in use        |

| LDO3      | 38  | Power   | O   | LDO regulator output                                                                                  | VCC5, REFGND | PD 5 $\mu$ A                     |

| VCCS      | 39  | Analog  | I/O | VCC7 voltage sense input                                                                              | VCC7, DGND   | No                               |

| VCC5      | 40  | Power   | I   | LDO3 and LDO4 power Input                                                                             | VCC5, AGND   | No                               |

| LDO4      | 41  | Power   | O   | LDO regulator output                                                                                  | VCC5, REFGND | PD 5 $\mu$ A                     |

| TESTV     | 42  | Analog  | O   | Analog test output (DFT)                                                                              | VCC7, AGND   | No                               |

**Pin Functions (continued)**

| PIN        |     | TYPE    | I/O     | DESCRIPTION                                   | SUPPLIES      | PU / PD                                                        |

|------------|-----|---------|---------|-----------------------------------------------|---------------|----------------------------------------------------------------|

| NAME       | NO. |         |         |                                               |               |                                                                |

| GPIO3      | 43  | Digital | I/O     | GPIO and LED2 output                          | VRTC, DGND    | OD: External PU                                                |

|            |     |         | OD      |                                               |               |                                                                |

| NRESPWRON2 | 44  | Digital | O       | Second NRESPWRON output                       | VRTC, DGND    | PD active during device OFF state. External pullup when ACTIVE |

|            |     |         | OD      |                                               |               |                                                                |

| VBACKUP    | 45  | Power   | I       | Tie this pin to AGND                          | VBACKUP, AGND | No                                                             |

| AGND       | 46  | Power   | I/O     | Analog ground                                 | AGND          | No                                                             |

| VCC7       | 47  | Power   | I       | VRTC power input and analog references supply | VCC7, REFGND  | No                                                             |

| VRTC       | 48  | Power   | O       | LDO regulator output                          | VCC7, REFGND  | PD 5 $\mu$ A                                                   |

| AGNDEX     | 49  | Power   | I/O     | EXTCTRL resistive divider ground              | AGNDEX        | No                                                             |

| VSENSE     | 50  | Analog  | I       | EXTCTRL resistive divider output              | VOUT, AGNDEX  | No                                                             |

| EN         | 51  | Digital | O       | EXTCTRL enable signal for external converter  | VCC7, DGND    | No                                                             |

| VOUT       | 52  | Analog  | I       | EXTCTRL resistive divider input               | VOUT, AGNDEX  | No                                                             |

| DGND       | 53  | Power   | I/O     | Digital ground                                | DGND          | No                                                             |

| VFB1       | 54  | Analog  | I       | VDD1 feedback voltage                         | VCC7, DGND    | PD 5 $\mu$ A                                                   |

| PWRON      | 55  | Digital | I       | External switch-on control (ON button)        | VCC7, DGND    | Programmable PU (default active)                               |

| GND1       | 56  | Power   | I/O     | VDD1 DC-DC power ground                       | VCC1, GND1    | No                                                             |

|            | 57  |         |         |                                               |               |                                                                |

| SW1        | 58  | Power   | O       | VDD1 DC-DC switched output                    | VCC1, GND1    | No                                                             |

|            | 59  |         |         |                                               |               |                                                                |

| VCC1       | 60  | Power   | I       | VDD1 DC-DC power Input                        | VCC1, GND1    | No                                                             |

|            | 61  |         |         |                                               |               |                                                                |

| SLEEP      | 62  | Digital | I       | ACTIVE-SLEEP state transition control signal  | VDDIO, DGND   | Programmable PD (default active)                               |

| GPIO8      | 63  | Digital | I/O, OD | GPIO                                          | VRTC, DGND    | OD: External PU                                                |

| CLK32KOUT  | 64  | Digital | O       | 32-kHz clock output                           | VDDIO, DGND   | PD, disabled in ACTIVE or SLEEP state                          |

| GPIO6      | 65  | Digital | I/O, OD | GPIO                                          | VRTC, DGND    | OD: External PU                                                |

| NRESPWRON  | 66  | Digital | O       | Power off reset                               | VDDIO, DGND   | PD active during device OFF state                              |

| VCC2       | 67  | Power   | I       | VDD2 DC-DC power input                        | VCC2, GND2    | No                                                             |

|            | 68  |         |         |                                               |               |                                                                |

| SW2        | 69  | Power   | O       | VDD2 DC-DC switched output                    | VCC2, GND2    | No                                                             |

|            | 70  |         |         |                                               |               |                                                                |

| GND2       | 71  | Power   | I/O     | VDD2 DC-DC power ground                       | VCC2, GND2    | No                                                             |

|            | 72  |         |         |                                               |               |                                                                |

| GPIO7      | 73  | Digital | I/O, OD | GPIO                                          | VRTC, DGND    | OD: External PU                                                |

| VFB2       | 74  | Analog  | I       | VDD2 DC-DC feedback voltage                   | VCC7, DGND    | PD 5 $\mu$ A                                                   |

| INT1       | 75  | Digital | O       | Interrupt flag                                | VDDIO, DGND   | No                                                             |

| GPIO2      | 76  | Digital | I/O, OD | GPIO and DC-DC clock synchronization          | VRTC, DGND    | OD: External PU                                                |

| LDO5       | 77  | Power   | O       | LDO regulator output                          | VCC4, REFGND  | PD 5 $\mu$ A                                                   |

|            | 78  |         |         |                                               |               |                                                                |

| VCC4       | 79  | Power   | I       | LDO5 power input                              | VCC4, AGND2   | No                                                             |

| VCC8       | 80  | Power   | I       | LDO8 power input                              | VCC8, AGND2   | No                                                             |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                       |                                                                                  | MIN  | MAX                       | UNIT |

|---------------------------------------|----------------------------------------------------------------------------------|------|---------------------------|------|

| Voltage range                         | VCC1, VCC2, VCCIO, VCC3, VCC4, VCC5, VCC7, VCC8                                  | -0.3 | 7                         | V    |

|                                       | VCC6, VDDIO                                                                      | -0.3 | 3.6                       | V    |

|                                       | SW1, SW2, SWIO                                                                   | -0.3 | 7                         | V    |

|                                       | 10 ns Transient                                                                  | -2   | 7                         | V    |

|                                       | VFB1, VFB2, VFBIO                                                                | -0.3 | 3.6                       | V    |

|                                       | VOUT, VSENSE                                                                     | -0.3 | 7                         | V    |

|                                       | BOOT1                                                                            | -0.3 | VRTC <sub>MAX</sub> + 0.3 | V    |

|                                       | SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT, NRESPWRON                    | -0.3 | VDDIOMAX + 0.3            | V    |

|                                       | PWRON                                                                            | -0.3 | 7                         | V    |

|                                       | PWRHOLD, GPIO0                                                                   | -0.3 | 7                         | V    |

|                                       | OSCEXT32K, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8 <sup>(2)</sup> | -0.3 | 7                         | V    |

|                                       | HDRST                                                                            | -0.3 | VRTC <sub>MAX</sub> + 0.3 | V    |

|                                       | OSC16MIN, OSC16MOUT                                                              | -0.3 | 5.7                       | V    |

|                                       | NRESPWRON <sub>2</sub> <sup>(2)</sup>                                            | -0.3 | 7                         | V    |

| Peak output current range             | PWRDN <sup>(3)</sup>                                                             | -0.3 | 7                         | V    |

|                                       | VCCS                                                                             | -0.3 | 7                         | V    |

| Peak output current range             | All other pins than power resources                                              | -5   | 5                         | mA   |

| Functional junction temperature range |                                                                                  | -45  | 150                       | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) VRTC supplies the I/O but the I/O can also be driven from VCC7 or to VCC7 voltage level.

(3) VRTC supplies the input supplied but can also be driven from VCC7 voltage level.

### 7.2 Handling Ratings

|                    |                           |                                                         | MIN                                             | MAX   | UNIT |

|--------------------|---------------------------|---------------------------------------------------------|-------------------------------------------------|-------|------|

| T <sub>stg</sub>   | Storage temperature range |                                                         | -55                                             | 150   | °C   |

| V <sub>(ESD)</sub> | Electrostatic discharge   | Human body model (HBM), per AEC-Q100-002 <sup>(1)</sup> |                                                 | -2000 | 2000 |

|                    |                           | Charged device model (CDM), per AEC Q100-011            | Corner pins (1, 20, 21, 40, 41, 60, 61, and 80) | -750  | 750  |

|                    |                           |                                                         | Other pins                                      | -500  | 500  |

(1) AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

**Note:** VCC7 should be connected to highest supply that is connected to device VCCx pin.

**Exception:** The VCC4, VCC5, VIN, and AVIN inputs can be higher than VCC7. VCCS can be higher than VCC7 if VMBBUF\_BYPASS = 0 (buffer is enabled).

|                     |                                                                      | MIN  | NOM   | MAX  | UNIT |

|---------------------|----------------------------------------------------------------------|------|-------|------|------|

| Input voltage range | VCC5, VCCS                                                           | 2.7  |       | 5.5  | V    |

|                     | VCC3, VCC4, VCC8                                                     | 1.7  |       | 5.5  | V    |

|                     | VCC1, VCC2, VCCIO, VCC7                                              | 4    | 5     | 5.5  | V    |

|                     | VCC6, VDDIO                                                          | 1.4  | 3.3   | 3.6  | V    |

|                     | VSENSE                                                               | -0.1 |       | 6.5  | V    |

|                     | PWRON                                                                | 0    | 3.8   | 5.5  | V    |

|                     | SDA_SDI, SCL_SCK, EN2, EN1, SLEEP, INT1, CLK32KOUT                   | 1.65 | VDDIO | 3.45 | V    |

|                     | PWRHOLD, HDRTS                                                       | 1.65 | VRTC  | 5.5  | V    |

|                     | GPIO0, GPIO1, GPIO2, GPIO3, GPIO4, GPIO5, GPIO6, GPIO7, GPIO8, PWRDN | 1.65 | VRTC  | 5.5  | V    |

|                     | VCCS                                                                 | 0    |       | 5.5  | V    |

|                     | OSCEXT32K                                                            | 0    |       | 5.5  | V    |

## 7.4 Thermal Characteristics

over operating free-air temperature range (unless otherwise noted)

| THERMAL METRIC <sup>(1)</sup> |                                              | TPS659119-Q1<br>PFP (80 PINS) | UNIT |

|-------------------------------|----------------------------------------------|-------------------------------|------|

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 34.1                          | °C/W |

| $R_{\theta JC(\text{top})}$   | Junction-to-case(top) thermal resistance     | 9.6                           | °C/W |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 10.1                          | °C/W |

| $\Psi_{JT}$                   | Junction-to-top characterization parameter   | 0.3                           | °C/W |

| $\Psi_{JB}$                   | Junction-to-board characterization parameter | 9.9                           | °C/W |

| $R_{\theta JC(\text{bot})}$   | Junction-to-case(bottom) thermal resistance  | 0.9                           | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, [SPRA953](#).

## 7.5 External Component Recommendation

For crystal oscillator components, see the [32-kHz RTC Clock](#) section. **Note:** The VCC7 supply must have enough capacitance to specify that when the supply is switched off, voltage does not fall at a rate faster than 10 mV/ms. This ensures that RTC domain data is maintained.

|                         |                            | MIN                           | NOM | MAX | UNIT |    |

|-------------------------|----------------------------|-------------------------------|-----|-----|------|----|

| <b>POWER REFERENCES</b> |                            |                               |     |     |      |    |

| $C_{O(VREF)}$           | VREF filtering capacitor   | Connected from VREF to REFGND | 100 |     | nF   |    |

| <b>VDD1 SMPS</b>        |                            |                               |     |     |      |    |

| $C_{I(VCC1)}$           | Input capacitor            | X5R or X7R dielectric         | 10  |     | μF   |    |

| $C_{O(VDD1)}$           | Output filter capacitor    | X5R or X7R dielectric         | 4   | 10  | 12   | μF |

|                         | $C_O$ filter capacitor ESR | $f = 3$ MHz                   | 10  | 300 | mΩ   |    |

| $L_{O(VDD1)}$           | Inductor                   |                               | 2.2 |     | μH   |    |

| $DCR_L$                 | $L_O$ inductor dc resistor |                               |     | 125 | mΩ   |    |

| <b>VDD2 SMPS</b>        |                            |                               |     |     |      |    |

| $C_{I(VCC2)}$           | Input capacitor            | X5R or X7R dielectric         | 10  |     | μF   |    |

| $C_{O(VDD2)}$           | Output filter capacitor    | X5R or X7R dielectric         | 4   | 10  | 12   | μF |

|                         | $C_O$ filter capacitor ESR | $f = 3$ MHz                   | 10  | 300 | mΩ   |    |

| $L_{O(VDD2)}$           | Inductor                   |                               | 2.2 |     | μH   |    |

| $DCR_L$                 | $L_O$ inductor dc resistor |                               |     | 125 | mΩ   |    |

## External Component Recommendation (continued)

For crystal oscillator components, see the [32-kHz RTC Clock](#) section. **Note:** The VCC7 supply must have enough capacitance to specify that when the supply is switched off, voltage does not fall at a rate faster than 10 mV/ms. This ensures that RTC domain data is maintained.

|                 |                               |                            | MIN | NOM | MAX  | UNIT      |

|-----------------|-------------------------------|----------------------------|-----|-----|------|-----------|

| <b>VIO SMPS</b> |                               |                            |     |     |      |           |

| $C_{I(VCC10)}$  | Input capacitor               | X5R or X7R dielectric      |     | 10  |      | $\mu F$   |

| $C_{O(VIO)}$    | Output filter capacitor       | X5R or X7R dielectric      | 4   | 10  | 12   | $\mu F$   |

|                 | $C_O$ filter capacitor ESR    | $f = 3$ MHz                |     | 10  | 300  | $m\Omega$ |

| $L_{O(VIO)}$    | Inductor                      |                            |     | 2.2 |      | $\mu H$   |

| $DCR_L$         | $L_O$ inductor dc resistor    |                            |     |     | 125  | $m\Omega$ |

| <b>LDO1</b>     |                               |                            |     |     |      |           |

| $C_{I(VCC6)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(LDO1)}$   | Output filtering capacitor    |                            | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO2</b>     |                               |                            |     |     |      |           |

| $C_{O(LDO2)}$   | Output filtering capacitor    |                            | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO3</b>     |                               |                            |     |     |      |           |

| $C_{I(VCC5)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(LDO3)}$   | Output filtering capacitor    |                            | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO4</b>     |                               |                            |     |     |      |           |

| $C_{O(LDO4)}$   | Output filtering capacitor    |                            | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO5</b>     |                               |                            |     |     |      |           |

| $C_{I(VCC4)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(LDO5)}$   | Output filtering capacitor    | $V_{OUT}(LDOx) > 1.2$ V    | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 |                               | $V_{OUT}(LDOx) \leq 1.2$ V | 0.8 | 2   | 2.2  |           |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO6</b>     |                               |                            |     |     |      |           |

| $C_{I(VCC3)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(LDO6)}$   | Output filtering capacitor    | $V_{OUT}(LDOx) > 1.2$ V    | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 |                               | $V_{OUT}(LDOx) \leq 1.2$ V | 0.8 | 2   | 2.2  |           |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO7</b>     |                               |                            |     |     |      |           |

| $C_{O(LDO7)}$   | Output filtering capacitor    | $V_{OUT}(LDOx) > 1.2$ V    | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 |                               | $V_{OUT}(LDOx) \leq 1.2$ V | 0.8 | 2   | 2.2  |           |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>LDO8</b>     |                               |                            |     |     |      |           |

| $C_{I(VCC8)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(LDO8)}$   | Output filtering capacitor    | $V_{OUT}(LDOx) > 1.2$ V    | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 |                               | $V_{OUT}(LDOx) \leq 1.2$ V | 0.8 | 2   | 2.2  |           |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

| <b>VRTC LDO</b> |                               |                            |     |     |      |           |

| $C_{I(VCC7)}$   | Input capacitor               | X5R or X7R dielectric      |     | 4.7 |      | $\mu F$   |

| $C_{O(VRTC)}$   | Output filtering capacitor    |                            | 0.8 | 2.2 | 2.64 | $\mu F$   |

|                 | $C_O$ filtering capacitor ESR |                            | 0   |     | 500  | $m\Omega$ |

## 7.6 I/O Pullup and Pulldown Characteristics

over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

| PARAMETER                                                                            | TEST CONDITIONS                                              | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------|------|-----|-----|------|

| GPIO0-8 external pullup resistor                                                     | Connected to VDDIO                                           | -20% | 120 | 20% | kΩ   |

| GPIO0-8 programmable pulldown (default active except GPIO0)                          | at 1.8 V, VRTC = 1.8 V, OFF state                            | 2    | 4.5 | 15  | μA   |

| SDA_SDI, SCL_SCK, SDASR_EN2, SCLSR_EN1 external pullup resistor                      | Connected to VDDIO                                           |      | 1.2 |     | kΩ   |

| SDA_SDI, SCL_SCK, SDASR_EN2, SCLSR_EN1 programmable pulldown (DFT, default inactive) | Grounded, VDDIO = 1.8 V                                      | -45% | 8   | 45% | kΩ   |

| SLEEP, PWRHOLD, programmable pulldown (default active)                               | at 1.8 V, VRTC = 1.8 V; $T_A = 25^\circ\text{C}$ for PWRHOLD | 2    | 4.5 | 10  | μA   |

| NRESPWRON, NRESPWRON2 pulldown                                                       | at 1.8 V, VCC7 = 5.5 V, OFF state                            | 2    | 4.5 | 10  | μA   |

| 32KCLKOUT pulldown (disabled in ACTIVE-SLEEP state)                                  | at 1.8 V, VRTC = 1.8 V, OFF state                            | 2    | 4.5 | 10  | μA   |

| PWRON programmable pullup (default active)                                           | Grounded, VCC7 = 5.5 V                                       | -43  | -31 | -15 | μA   |

| HDRST programmable pulldown (default active)                                         | at 1.8 V, VRTC = 1.8 V                                       | 2    | 4.5 | 10  | μA   |

(1) The internal pullups on the CTL-I<sup>2</sup>C and SR-I<sup>2</sup>C pins are used for test purposes or when the SR-I<sup>2</sup>C interface is not used. Discrete pullups to the VIO supply must be mounted on the board in order to use the I<sup>2</sup>C interfaces. The internal I<sup>2</sup>C pullups must not be used for functional applications

## 7.7 Digital I/O Voltage Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                           | MIN                        | TYP          | MAX  | UNIT |

|-----------------------------------------------------|----------------------------|--------------|------|------|

| <b>RELATED I/O:<br/>PWRON</b>                       |                            |              |      |      |

| $V_{IL}$ Low-level input voltage                    |                            | 0.3 x VBAT   |      | V    |

| $V_{IH}$ High-level input voltage                   |                            | 0.7 x VBAT   |      | V    |

| <b>RELATED I/O:<br/>PWRHOLD, GPIO0-8, PWRDN</b>     |                            |              |      |      |

| $V_{IL}$ Low-level input voltage                    |                            | 0.45         |      | V    |

| $V_{IH}$ High-level input voltage                   |                            | 1.3          | VBAT | V    |

| <b>RELATED I/O:<br/>BOOT1</b>                       |                            |              |      |      |

| Low level input – Impedance between BOOT1 and GND   |                            | 10           |      | kΩ   |

| High level input – Impedance between BOOT1 and VRTC |                            | 10           |      | kΩ   |

| Hi-Z level input – Impedance between BOOT1 and GND  |                            | 500          |      | kΩ   |

| <b>RELATED I/O:<br/>SLEEP</b>                       |                            |              |      |      |

| $V_{IL}$ Low-level input voltage                    |                            | 0.35 x VDDIO |      | V    |

| $V_{IH}$ High-level input voltage                   |                            | 0.65 x VDDIO |      | V    |

| <b>RELATED I/O:<br/>HDRST</b>                       |                            |              |      |      |

| $V_{IL}$ Low-level input voltage                    |                            | 0.35 x VRTC  |      | V    |

| $V_{IH}$ High-level input voltage                   |                            | 0.65 x VRTC  |      | V    |

| <b>RELATED I/O:<br/>NRESPWRON, INT1, 32KCLKOUT</b>  |                            |              |      |      |

| $V_{OL}$ Low-level output voltage                   | $I_{OL} = 100 \mu\text{A}$ |              | 0.2  | V    |

|                                                     | $I_{OL} = 2 \text{ mA}$    |              | 0.45 | V    |

| $V_{OH}$ High-level output voltage                  | $I_{OH} = 100 \mu\text{A}$ | VDDIO – 0.2  |      | V    |

|                                                     | $I_{OH} = 2 \text{ mA}$    | VDDIO – 0.45 |      | V    |

| <b>Related I/O:<br/>EN</b>                          |                            |              |      |      |

| $V_{OL}$ Low-level output voltage                   | $I_{OL} = 100 \mu\text{A}$ |              | 0.2  | V    |

|                                                     | $I_{OL} = 2 \text{ mA}$    |              | 0.9  | V    |

## Digital I/O Voltage Electrical Characteristics (continued)

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                            |                                                                | MIN                           | TYP         | MAX         | UNIT |

|----------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------|-------------|-------------|------|

| V <sub>OH</sub>                                                      | High-level output voltage                                      | I <sub>OH</sub> = 100 $\mu$ A | VCC7 – 0.2  |             | V    |

|                                                                      |                                                                | I <sub>OH</sub> = 2 mA        | VCC7 – 0.45 |             | V    |

| <b>RELATED I/O:<br/>GPIO0 (PUSH-PULL MODE)</b>                       |                                                                |                               |             |             |      |

| V <sub>OL</sub>                                                      | Low-level output voltage                                       | I <sub>OL</sub> = 100 $\mu$ A |             | 0.2         | V    |

|                                                                      |                                                                | I <sub>OL</sub> = 2 mA        |             | 0.45        | V    |

| V <sub>OH</sub>                                                      | High-level output voltage                                      | I <sub>OH</sub> = 100 $\mu$ A | VCC7 – 0.2  |             | V    |

|                                                                      |                                                                | I <sub>OH</sub> = 2 mA        | VCC7 – 0.45 |             | V    |

| <b>RELATED OPEN-DRAIN I/O:<br/>GPIO0, GPIO2, GPIO4-8, NRESPWRON2</b> |                                                                |                               |             |             |      |

| V <sub>OL</sub>                                                      | Low-level output voltage                                       | I <sub>OL</sub> = 100 $\mu$ A |             | 0.2         | V    |

|                                                                      |                                                                | I <sub>OL</sub> = 2 mA        |             | 0.45        | V    |

| <b>RELATED OPEN-DRAIN I/O:<br/>GPIO1, GPIO3</b>                      |                                                                |                               |             |             |      |

| V <sub>OL</sub>                                                      | Low-level output voltage                                       | I <sub>OL</sub> = 100 $\mu$ A |             | 0.2         | V    |

|                                                                      |                                                                | I <sub>OL</sub> = 2 mA        |             | 0.4         | V    |

| <b>I</b>                                                             |                                                                |                               |             |             |      |

| V <sub>IL</sub>                                                      | Low-level input voltage                                        |                               | -0.5        | 0.3 x VDDIO | V    |

| V <sub>IH</sub>                                                      | High-level input voltage                                       |                               | 0.7 x VDDIO |             | V    |

|                                                                      | Hysteresis                                                     |                               | 0.1 x VDDIO |             | V    |

| V <sub>OL</sub>                                                      | Low-level output voltage at 3 mA (sink current), VDDIO = 1.8 V |                               |             | 0.2 x VDDIO | V    |

| V <sub>OL</sub>                                                      | Low-level output voltage at 3 mA (sink current), VDDIO = 3.3 V |                               |             | 0.4 x VDDIO | V    |

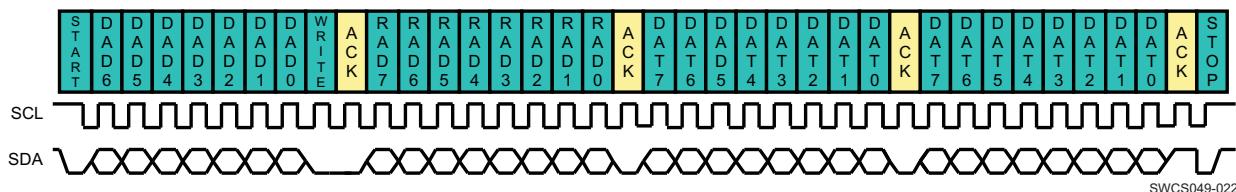

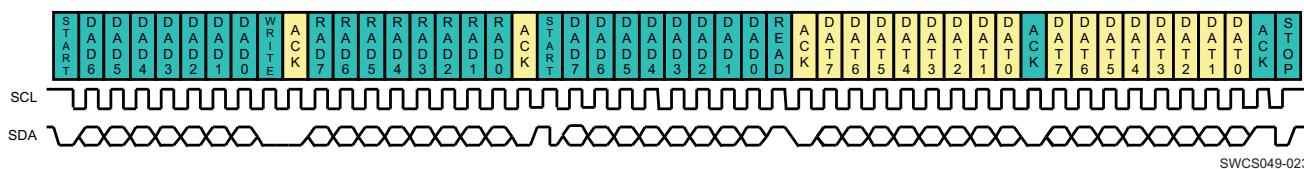

## 7.8 I<sup>2</sup>C Interface and Control Signals

over operating free-air temperature range (unless otherwise noted)

| NO.                          | PARAMETER                              | TEST CONDITIONS <sup>(1)</sup> (2) | MIN                   | TYP | MAX  | UNIT |

|------------------------------|----------------------------------------|------------------------------------|-----------------------|-----|------|------|

| <b>GENERAL REQUIREMENTS</b>  |                                        |                                    |                       |     |      |      |

|                              | INT1 rise and fall times               | $C_L = 5$ to 35 pF                 | 5                     | 10  | ns   |      |

|                              | NRESPWRON rise and fall times          | $C_L = 5$ to 35 pF                 | 5                     | 10  | ns   |      |

| <b>SLAVE HIGH-SPEED MODE</b> |                                        |                                    |                       |     |      |      |

|                              | SCL/EN1 and SDA/EN2 rise and fall time | $C_L = 10$ to 100 pF               | 10                    | 80  | ns   |      |

|                              | Data rate                              |                                    |                       | 3.4 | Mbps |      |

| I3                           | $t_{su}(SDA-SCLH)$                     | Setup time, SDA valid to SCL high  |                       | 10  | ns   |      |

| I4                           | $t_h(SCLL-SDA)$                        | Hold time, SDA valid from SCL low  |                       | 0   | 70   | ns   |

| I7                           | $t_{su}(SCLH-SDAL)$                    | Setup time, SCL high to SDA low    |                       | 160 | ns   |      |

| I8                           | $t_h(SDAL-SCLL)$                       | Hold time, SCL low from SDA low    |                       | 160 | ns   |      |

| I9                           | $t_{su}(SDAH-SCLH)$                    | Setup time, SDA high to SCL high   |                       | 160 | ns   |      |

| <b>SLAVE<br/>FAST MODE</b>   |                                        |                                    |                       |     |      |      |

|                              | SCL/EN1 and SDA/EN2 rise and fall time | $C_L = 10$ to 400 pF               | $20 + 0.1 \times C_L$ | 250 | ns   |      |

|                              | Data rate                              |                                    |                       | 400 | Kbps |      |

| I3                           | $t_{su}(SDA-SCLH)$                     | Setup time, SDA valid to SCL high  |                       | 100 | ns   |      |

| I4                           | $t_h(SCLL-SDA)$                        | Hold time, SDA valid from SCL low  |                       | 0   | 0.9  | μs   |

| I7                           | $t_{su}(SCLH-SDAL)$                    | Setup time, SCL high to SDA low    |                       | 0.6 | μs   |      |

| I8                           | $t_h(SDAL-SCLL)$                       | Hold time, SCL low from SDA low    |                       | 0.6 | μs   |      |

| I9                           | $t_{su}(SDAH-SCLH)$                    | Setup time, SDA high to SCL high   |                       | 0.6 | μs   |      |

| <b>SLAVE STANDARD MODE</b>   |                                        |                                    |                       |     |      |      |

|                              | SCL/EN1 and SDA/EN2 rise and fall time | $C_L = 10$ to 400 pF               |                       | 250 | ns   |      |

|                              | Data rate                              |                                    |                       | 100 | Kbps |      |

| I3                           | $t_{su}(SDA-SCLH)$                     | Setup time, SDA valid to SCL high  |                       | 250 | ns   |      |

| I4                           | $t_h(SCLL-SDA)$                        | Hold time, SDA valid from SCL low  |                       | 0   | μs   |      |

| I7                           | $t_{su}(SCLH-SDAL)$                    | Setup time, SCL high to SDA low    |                       | 4.7 | μs   |      |

| I8                           | $t_h(SDAL-SCLL)$                       | Hold time, SCL low from SDA low    |                       | 4   | μs   |      |

| I9                           | $t_{su}(SDAH-SCLH)$                    | Setup time, SDA high to SCL high   |                       | 4   | μs   |      |

(1) The input timing requirements are given by considering a rising or falling time of: 80 ns in high-speed mode (3.4 Mbps) 300 ns in fast-speed mode (400 kbps) 1000 ns in Standard mode (100 kbps)

(2) SDA is SDA\_SDI or EN2 signal, SCL is SCL\_SCK or EN1 signal

## 7.9 Switching Characteristics—I<sup>2</sup>C Interface and Control Signals

over operating free-air temperature range (unless otherwise noted)

| NO.                          | PARAMETER   | TEST CONDITIONS          | MIN | TYP | MAX | UNIT |

|------------------------------|-------------|--------------------------|-----|-----|-----|------|

| <b>SLAVE HIGH-SPEED MODE</b> |             |                          |     |     |     |      |

| I1                           | $t_w(SCLL)$ | Pulse duration, SCL low  |     | 160 | ns  |      |

| I2                           | $t_w(SCLH)$ | Pulse duration, SCL high |     | 60  | ns  |      |

| <b>SLAVE FAST MODE</b>       |             |                          |     |     |     |      |

| I1                           | $t_w(SCLL)$ | Pulse duration, SCL low  |     | 1.3 | μs  |      |

| I2                           | $t_w(SCLH)$ | Pulse duration, SCL high |     | 0.6 | μs  |      |

| <b>SLAVE STANDARD MODE</b>   |             |                          |     |     |     |      |

| I1                           | $t_w(SCLL)$ | Pulse duration, SCL low  |     | 4.7 | μs  |      |

| I2                           | $t_w(SCLH)$ | Pulse duration, SCL high |     | 4   | μs  |      |

## 7.10 Power Consumption

over operating free-air temperature range (unless otherwise noted)

All current consumption measurements are relative to the FULL chip, all VCC inputs set to VBAT voltage, COMP2 is off.

| PARAMETER           | TEST CONDITIONS                                                                 | MIN | TYP  | MAX | UNIT |

|---------------------|---------------------------------------------------------------------------------|-----|------|-----|------|

| Device OFF state    | VBAT = 5 V, XTAL oscillator running                                             |     | 2.5  |     | mA   |

|                     | VBAT = 5 V, Bypass clock used                                                   |     | 22   |     | µA   |

| Device SLEEP state  | VBAT = 5 V, 3 DCDCs on in PFM mode, 5 LDOs on, no load, XTAL oscillator running |     | 2.8  |     | mA   |

| Device ACTIVE state | VBAT = 5 V, 3 DCDCs on in PWM mode, 5 LDOs on, no load, XTAL oscillator running |     | 26.6 |     | mA   |

## 7.11 Power References and Thresholds

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                    | TEST CONDITIONS                                                  | MIN   | TYP   | MAX  | UNIT |

|--------------------------------------------------------------|------------------------------------------------------------------|-------|-------|------|------|

| Output reference voltage (VREF pin)                          | Device in active or low-power mode                               | -1%   | 0.85  | 1%   | V    |

| Main battery not present falling threshold VBNP <sub>R</sub> | Measured on pin VCC7, falling (Triggering monitored on pin VRTC) | 1.8   | 2.1   | 2.3  | V    |

| PORXTAL                                                      | The POR threshold for rising VCC7 voltages                       | 3.58  | 3.77  | 3.96 | V    |

|                                                              | The POR threshold for falling VCC7 voltages                      | 3.50  | 3.68  | 3.87 | V    |

|                                                              | Difference between rising and falling thresholds                 | 62.55 | 89.35 | 200  | mV   |

## 7.12 Thermal Monitoring and Shutdown

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                       | TEST CONDITIONS                                   | MIN | TYP | MAX | UNIT |

|-------------------------------------------------|---------------------------------------------------|-----|-----|-----|------|

| Hot-die temperature rising threshold            | THERM_HDSEL[1:0] = 00                             |     | 117 |     | °C   |

|                                                 | THERM_HDSEL[1:0] = 01                             |     | 121 |     |      |

|                                                 | THERM_HDSEL[1:0] = 10                             | 113 | 125 | 136 |      |

|                                                 | THERM_HDSEL[1:0] = 11                             |     | 130 |     |      |

| Hot-die temperature hysteresis                  |                                                   |     | 10  |     | °C   |

| Thermal shutdown temperature rising threshold   |                                                   | 150 | 165 | 180 | °C   |

| Thermal shutdown temperature recovery threshold | THERM_HDSEL[1:0] = 00                             |     | 107 |     | °C   |

|                                                 | THERM_HDSEL[1:0] = 01                             |     | 111 |     |      |

|                                                 | THERM_HDSEL[1:0] = 10                             |     | 115 |     |      |

|                                                 | THERM_HDSEL[1:0] = 11                             |     | 120 |     |      |

| Ground current                                  | Device in ACTIVE state, Temp = 27°C, VCC7 = 3.8 V |     | 6   |     | µA   |

## 7.13 32-kHz RTC Clock

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                              | TEST CONDITIONS                                                            | MIN  | TYP    | MAX  | UNIT          |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|--------|------|---------------|

| <b>GENERAL CLK32KOUT REQUIREMENTS</b>                                                  |                                                                            |      |        |      |               |

| CLK32KOUT rise and fall time                                                           | $C_L = 35 \text{ pF}$                                                      |      |        | 10   | ns            |

| <b>EXTERNAL CLOCK (OSC16MIN GROUNDED, OSC16MOUT FLOATING, AND OSCEXT32K INPUT)</b>     |                                                                            |      |        |      |               |

| Input bypass clock frequency                                                           | OSCKIN input                                                               |      | 32     |      | kHz           |

| Input bypass clock duty cycle                                                          | OSCKIN input                                                               | 40%  |        | 60%  |               |

| Input bypass clock rise and fall time                                                  | 10% – 90%, OSCEXT32K input                                                 |      | 10     | 20   | ns            |

| CLK32KOUT duty cycle                                                                   | Logic output signal                                                        | 40%  |        | 60%  |               |

| Bypass clock setup time                                                                | 32KCLKOUT output                                                           |      |        | 1    | ms            |

| Ground current                                                                         | Bypass mode                                                                |      |        | 1.5  | $\mu\text{A}$ |

| <b>CRYSTAL OSCILLATOR (CRYSTAL BETWEEN OSC16MIN AND OSC16MOUT, OSCEXT32K GROUNDED)</b> |                                                                            |      |        |      |               |

| Crystal frequency                                                                      | at specified load cap value                                                |      | 16.384 |      | MHz           |

| Crystal tolerance                                                                      | at 27°C                                                                    | –20  | 0      | 20   | ppm           |

| Oscillator frequency drift                                                             | $T_J$ from –40°C to 125°C, VCC7 from 4 V to 5.5 V; excluding crystal drift | –50  |        | 50   | ppm           |

| Max crystal series resistor                                                            | at fundamental frequency                                                   |      | 90     |      | $\Omega$      |

| Oscillator startup time                                                                | Power on until first time slot                                             |      |        | 13.2 | ms            |

| Drive level power                                                                      | Steady state operation                                                     | 15   | 120    |      | $\mu\text{W}$ |

| Ground current                                                                         |                                                                            |      | 2.5    |      | mA            |

| Overall frequency tolerance                                                            | CLK32KOUT output                                                           | –1%  |        | 1%   |               |

| Output frequency                                                                       | CLK32KOUT output                                                           |      | 32.768 |      | kHz           |

| Crystal motional inductance                                                            | According to crystal data sheet                                            | 23   | 33     | 43   | $\mu\text{H}$ |

| Crystal shunt capacitance                                                              | According to crystal data sheet                                            | 0.5  |        | 4    | $\text{pF}$   |

| Crystal load capacitance                                                               | According to crystal data sheet; including PCB parasitic capacitance       | 9    | 10     | 11   | $\text{pF}$   |

| <b>RC OSCILLATOR (OSC16MIN AND OSCEXT32K GROUNDED, OSC16MOUT FLOATING)</b>             |                                                                            |      |        |      |               |

| Output frequency                                                                       | CK32KOUT output                                                            |      | 32     |      | kHz           |

| Output frequency accuracy                                                              | at 25°C                                                                    | –15% | 0      | 15%  |               |

| Cycle jitter (RMS)                                                                     | Oscillator contribution                                                    |      |        | 10%  |               |

| Output duty cycle                                                                      |                                                                            | 40%  | 50%    | 60%  |               |

| Settling time                                                                          |                                                                            |      |        | 150  | $\mu\text{s}$ |

| Ground current                                                                         | Active at fundamental frequency                                            |      | 4      |      | $\mu\text{A}$ |

## 7.14 VRTC LDO

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                         | TEST CONDITIONS                                                                                                                                                                                | MIN                  | TYP    | MAX | UNIT          |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--------|-----|---------------|

| Input voltage $V_{IN}$            | On mode                                                                                                                                                                                        | 2.5                  |        | 5.5 | V             |

|                                   | Backup mode                                                                                                                                                                                    | 1.9                  |        | 3   |               |

| DC output voltage $V_{OUT}$       | On mode, $3 \text{ V} < V_{IN} < 5.5 \text{ V}$                                                                                                                                                | 1.78                 | 1.83   | 1.9 | V             |

|                                   | Backup mode, $2.3 \text{ V} \leq V_{IN} \leq 2.6 \text{ V}$                                                                                                                                    | 1.72                 | 1.78   | 1.9 |               |

| Rated output current $I_{OUTmax}$ | On mode                                                                                                                                                                                        | 20                   |        |     | mA            |

|                                   | Backup mode                                                                                                                                                                                    | 0.1                  |        |     |               |

| DC load regulation                | On mode, $I_{OUT} = I_{OUTmax}$ to 0                                                                                                                                                           |                      | 100    |     | mV            |

|                                   | Backup mode, $I_{OUT} = I_{OUTmax}$ to 0                                                                                                                                                       |                      | 100    |     |               |

| DC line regulation                | On mode, $V_{IN} = 3 \text{ V}$ to $V_{INmax}$ at $I_{OUT} = I_{OUTmax}$                                                                                                                       |                      | 2.5    |     | mV            |

|                                   | Backup mode, $V_{IN} = 2.3 \text{ V}$ to $5.5 \text{ V}$ at $I_{OUT} = I_{OUTmax}$                                                                                                             |                      | 100    |     |               |

| Transient load regulation         | On mode, $V_{IN} = V_{INmin} + 0.2 \text{ V}$ to $V_{INmax}$<br>$I_{OUT} = I_{OUTmax}/2$ to $I_{OUTmax}$ in 5 $\mu\text{s}$<br>and $I_{OUT} = I_{OUTmax}$ to $I_{OUTmax}/2$ in 5 $\mu\text{s}$ |                      | 50 (1) |     | mV            |

| Transient line regulation         | On mode, $V_{IN} = V_{INmin} + 0.5 \text{ V}$ to $V_{INmin}$ in 30 $\mu\text{s}$<br>and $V_{IN} = V_{INmin}$ to $V_{INmin} + 0.5 \text{ V}$ in 30 $\mu\text{s}$ ,<br>$I_{OUT} = I_{OUTmax}/2$  |                      | 25 (1) |     | mV            |

| Turn-on time                      | $I_{OUT} = 0$ , $V_{IN}$ rising from 0 up to 3.6 V, at $V_{OUT} = 0.1 \text{ V}$ up to $V_{OUTmin}$                                                                                            |                      | 2.2    |     | ms            |

| Ripple rejection                  | $V_{IN} = V_{INDC} + 100 \text{ mV}_{pp}$ tone, $V_{INDC+} = V_{INmin} + 0.1 \text{ V}$ to $V_{INmax}$ at $I_{OUT} = I_{OUTmax}/2$                                                             | $f = 217 \text{ Hz}$ | 55     |     | dB            |

|                                   |                                                                                                                                                                                                | $f = 50 \text{ kHz}$ | 35     |     |               |

| Ground current                    | Device in ACTIVE state                                                                                                                                                                         |                      | 23     |     | $\mu\text{A}$ |

|                                   | Device in BACKUP or OFF state                                                                                                                                                                  |                      | 3      |     |               |

(1) These parameters are not tested. They are used for design specification only.

## 7.15 VIO SMPS

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                                                     | TEST CONDITIONS                                                              | MIN        | TYP   | MAX | UNIT             |