ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1, ADS7954-Q1 ADS7956-Q1, ADS7957-Q1, ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1

ZHCSCF3A - MAY 2014 - REVISED AUGUST 2014

# ADS79xx-Q1 8 位,10 位和 12 位,1MSPS,4 通道,8 通道, 16 通道,单端,微功耗,串行接口,模数转换器

## 特性

- 符合汽车应用要求

- 具有经 AEC-Q100 测试的下列结果:

- 器件温度 1 级: -40°C 至 125°C 的环境运行温 度范围

- 器件人体模型 (HBM) 静电放电 (ESD) 分类等级

- 器件充电器件模型 (CDM) ESD 分类等级 C4B

- 产品系列:

- 8 位, 10 位和 12 位分辨率

- 4 通道、8 通道和 12 通道器件与 16 通道器件 均采用相同封装尺寸

- 1MHz 采样率串行器件

- 模拟电源范围: 2.7V 至 5.25V

- I/O 电源范围: 1.7V 至 5.25V

- 两个软件可选单极、输入范围:

- (0V至2.5V)或(0V至5V)

- 针对通道选择的自动和手动模式

- 每通道两个可编程警报级别

- 四个独立可配置通用输入输出 (GPIO) 接口

- 典型功率耗散值: 1MSPS 下为 14.5mW (V<sub>(+VA)</sub> =  $5V_{(+VBD)} = 3V$

- 断电电流 (1µA)

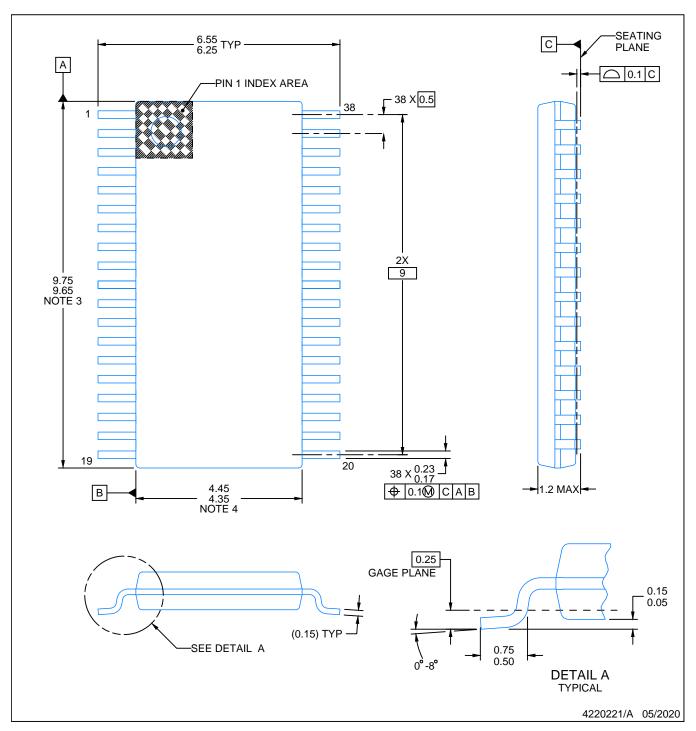

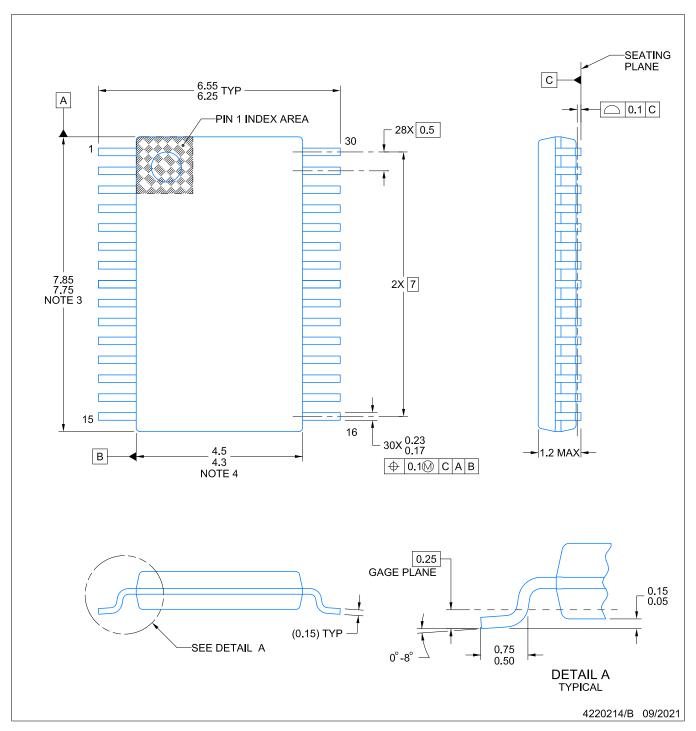

- 30 引脚和 38 引脚薄型小外形尺寸 (TSSOP) 封装

## 2 应用范围

- 车载系统

- 电源监控

- 电池供电系统

- 高速、数据采集系统

## 3 说明

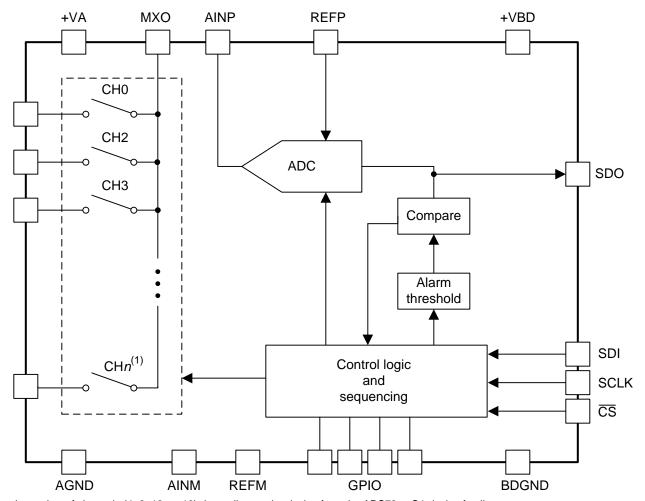

ADS79xx-Q1 器件系列由多通道 8 位, 10 位和 12 位 模数转换器 (ADC) 组成。 此器件包括一个基于电容器 的逐次逼近寄存器 (SAR) ADC, 此 ADC 支持固有的 采样保持。 多特性和出色性能使得 ADS79xx-Q1 器件 可用于需要对多条通道进行监控的广泛应用。

ADS79xx-Q1 器件在 2.7V 至 5.25V 的宽模拟电源范 围内运行。由于功耗极低,这些器件非常适合于电池供 电和隔离式电源供电的应用。

4 通道和 8 通道器件采用 30 引脚 TSSOP 封装。 12 通道和 16 通道器件采用 38 引脚 TSSOP 封装。

#### 器件信息(1)

| 器件名称       | 封装         | 封装尺寸                |  |  |  |

|------------|------------|---------------------|--|--|--|

| ADS7950-Q1 |            |                     |  |  |  |

| ADS7951-Q1 |            |                     |  |  |  |

| ADS7954-Q1 | TSSOP (30) | 7.80mm × 4.40mm     |  |  |  |

| ADS7958-Q1 |            |                     |  |  |  |

| ADS7959-Q1 |            |                     |  |  |  |

| ADS7952-Q1 |            |                     |  |  |  |

| ADS7953-Q1 |            |                     |  |  |  |

| ADS7956-Q1 | TCCOD (20) | 9.70mm x 4.40mm     |  |  |  |

| ADS7957-Q1 | TSSOP (38) | 9.70Hill X 4.40Hill |  |  |  |

| ADS7960-Q1 |            |                     |  |  |  |

| ADS7961-Q1 |            |                     |  |  |  |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

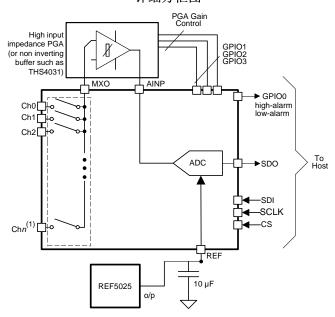

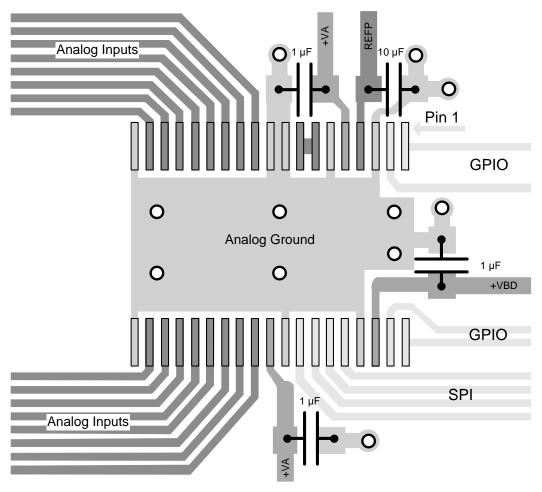

## 详细方框图

www.ti.com.cn

# 目录

| 1 | 特性1                                                         |    | 8.1 Overview                   | 20 |

|---|-------------------------------------------------------------|----|--------------------------------|----|

| 2 | 应用范围1                                                       |    | 8.2 Functional Block Diagram   | 20 |

| 3 | 说明1                                                         |    | 8.3 Feature Description        | 21 |

| 4 | 修订历史记录 2                                                    |    | 8.4 Device Functional Modes    | 25 |

| 5 | Device Comparison Table                                     |    | 8.5 Digital Output Code        |    |

| 6 | Pin Configurations and Functions                            |    | 8.6 Programming: GPIO          |    |

| 7 | Specifications 5                                            | 9  | Application and Implementation | 40 |

| • | 7.1 Absolute Maximum Ratings                                |    | 9.1 Application Information    | 40 |

|   | 7.2 Handling Ratings                                        |    | 9.2 Typical Applications       |    |

|   | 7.3 Recommended Operating Conditions                        |    | 9.3 Do's and Don'ts            | 42 |

|   | 7.4 Thermal Information                                     | 10 | Power-Supply Recommendations   | 42 |

|   | 7.5 Electrical Characteristics: ADS7950-Q1, ADS7951-        | 11 | Layout                         | 43 |

|   | Q1, ADS7952-Q1, ADS7953-Q1                                  |    | 11.1 Layout Guidelines         | 43 |

|   | 7.6 Electrical Characteristics: ADS7954-Q1, ADS7956-        |    | 11.2 Layout Example            | 43 |

|   | Q1, ADS7957-Q18                                             | 12 | 器件和文档支持                        | 44 |

|   | 7.7 Electrical Characteristics: ADS7958-Q1, ADS7959-        |    | 12.1 文档支持                      | 44 |

|   | Q1, ADS7960-Q1, ADS7961-Q1                                  |    | 12.2 相关链接                      | 44 |

|   | 7.8 Timing Requirements                                     |    | 12.3 商标                        | 44 |

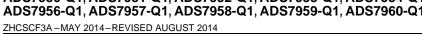

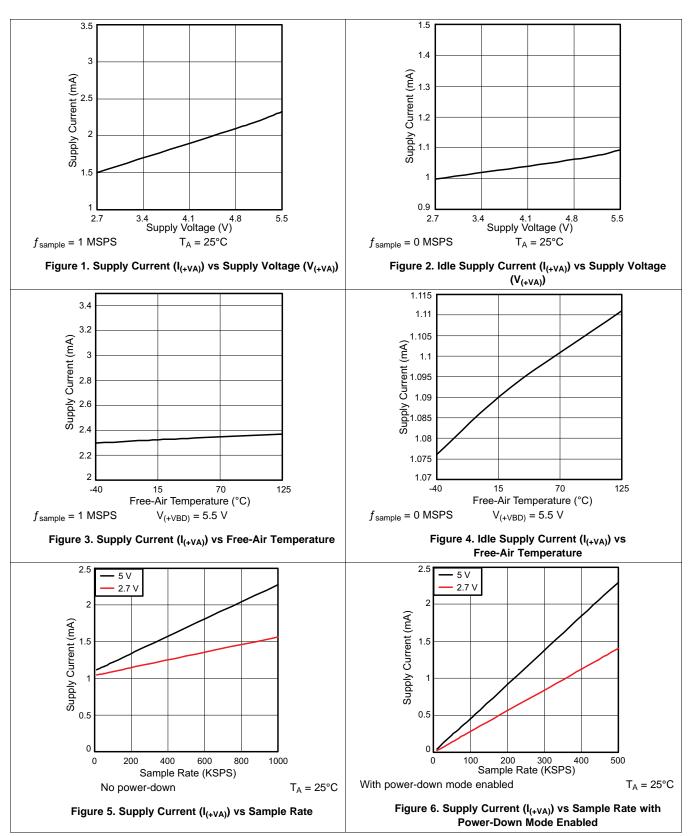

|   | 7.9 Typical Characteristics (All ADS79xx-Q1 Family Devices) |    | 12.4 静电放电警告                    | 44 |

|   | 7.10 Typical Characteristics (12-Bit Devices Only) 13       |    | 12.5 术语表                       |    |

| 8 | Detailed Description                                        | 13 | 机械封装和可订购信息                     | 44 |

| U | Detailed Description 20                                     |    |                                |    |

# 4 修订历史记录

| CI | hanges from Original (May 2014) to Revision A         | Page |

|----|-------------------------------------------------------|------|

| •  | 在器件信息表中添加了所有器件                                        |      |

| •  | Deleted Device Comparison Table footnote              | 3    |

| •  | Changed entire Application and Implementation section | 40   |

# 5 Device Comparison Table

|                    | RESOLUTION |            |            |  |  |  |

|--------------------|------------|------------|------------|--|--|--|

| NUMBER OF CHANNELS | 12 BIT     | 10 BIT     | 8 BIT      |  |  |  |

| 4                  | ADS7950-Q1 | ADS7954-Q1 | ADS7958-Q1 |  |  |  |

| 8                  | ADS7951-Q1 | _          | ADS7959-Q1 |  |  |  |

| 12                 | ADS7952-Q1 | ADS7956-Q1 | ADS7960-Q1 |  |  |  |

| 16                 | ADS7953-Q1 | ADS7957-Q1 | ADS7961-Q1 |  |  |  |

# 6 Pin Configurations and Functions

#### DBT Package TSSOP-30 (Top View)

| GPIO2 1 |                          | 30 GPIO1 | GPIO2 1 |            | 30 | GPIO1 |

|---------|--------------------------|----------|---------|------------|----|-------|

| GPIO3 2 | _                        | 29 GPIO0 | GPIO3 2 | - U        | 29 | GPIO0 |

| REFM 3  |                          | 28 +VBD  | REFM 3  |            | 28 | +VBD  |

| REFP 4  |                          | 27 BDGND | REFP 4  |            | 27 | BDGND |

| +VA 5   |                          | 26 SDO   | +VA 5   |            | 26 | SDO   |

| AGND 6  |                          | 25 SDI   | AGND 6  |            | 25 | SDI   |

| MXO 7   |                          | 24 SCLK  | MXO 7   |            | 24 | SCLK  |

| AINP 8  | ADS7950-Q1<br>ADS7954-Q1 | 23 CS    | AINP 8  | ADS7951-Q1 | 23 | CS    |

| AINM 9  |                          | 22 AGND  | AINM 9  | ADS7959-Q1 | 22 | AGND  |

| AGND 10 |                          | 21 +VA   | AGND 10 |            | 21 | +VA   |

| NC 11   |                          | 20 CH0   | CH7 [1] |            | 20 | CH0   |

| CH3 12  |                          | 19 NC    | CH6 12  |            | 19 | CH1   |

| NC 13   |                          | 18 CH1   | CH5 13  |            | 18 | CH2   |

| CH2 14  |                          | 17 NC    | CH4 14  |            | 17 | CH3   |

| NC 15   |                          | 16 NC    | NC 15   |            | 16 | NC    |

|         |                          | J        |         |            |    |       |

NC = No internal connection

#### DBT Package TSSOP-38 (Top View)

| GPIO2 1 |                          | 38 | GPIO1 | GPIO2 1 |                          | 38 | GPIO1 |

|---------|--------------------------|----|-------|---------|--------------------------|----|-------|

| GPIO3 2 |                          | 37 | GPIO0 | GPIO3 2 |                          | 37 | GPI00 |

| REFM 3  |                          | 36 | +VBD  | REFM 3  |                          | 36 | +VBD  |

| REFP 4  |                          | 35 | BDGND | REFP 4  |                          | 35 | BDGND |

| +VA 5   |                          | 34 | SDO   | +VA 5   |                          | 34 | SDO   |

| AGND 6  |                          | 33 | SDI   | AGND 6  |                          | 33 | SDI   |

| MXO 7   |                          | 32 | SCLK  | MXO 7   |                          | 32 | SCLK  |

| AINP 8  |                          | 31 | CS    | AINP 8  |                          | 31 | CS    |

| AINM 9  |                          | 30 | AGND  | AINM 9  |                          | 30 | AGND  |

| AGND 10 | ADS7952-Q1<br>ADS7956-Q1 | 29 | +VA   | AGND 10 | ADS7953-Q1<br>ADS7957-Q1 | 29 | +VA   |

| NC 11   | ADS7960-Q1               | 28 | CH0   | CH15 11 | ADS7961-Q1               | 28 | CH0   |

| NC 12   |                          | 27 | CH1   | CH14 12 |                          | 27 | CH1   |

| NC 13   |                          | 26 | CH2   | CH13 13 |                          | 26 | CH2   |

| NC 14   |                          | 25 | CH3   | CH12 14 |                          | 25 | CH3   |

| CH11 15 |                          | 24 | CH4   | CH11 15 |                          | 24 | CH4   |

| CH10 16 |                          | 23 | CH5   | CH10 16 |                          | 23 | CH5   |

| CH9 17  |                          | 22 | CH6   | CH9 17  |                          | 22 | CH6   |

| CH8 18  |                          | 21 | CH7   | CH8 18  |                          | 21 | CH7   |

| AGND 19 |                          | 20 | AGND  | AGND 19 |                          | 20 | AGND  |

|         |                          |    |       |         |                          | 1  |       |

ZHCSCF3A-MAY 2014-REVISED AUGUST 2014

www.ti.com.cn

### **Pin Functions**

|                   |                                          | PIN                                      |                           | 1 111 1 0                                |     |                                                                                 |

|-------------------|------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|-----|---------------------------------------------------------------------------------|

|                   | NUMBER                                   |                                          |                           |                                          |     |                                                                                 |

| NAME              | ADS7953-Q1,<br>ADS7957-Q1,<br>ADS7961-Q1 | ADS7952-Q1,<br>ADS7956-Q1,<br>ADS7960-Q1 | ADS7951-Q1,<br>ADS7959-Q1 | ADS7950-Q1,<br>ADS7954-Q1,<br>ADS7958-Q1 | 1/0 | DESCRIPTION                                                                     |

| ADC ANALO         | G INPUT                                  |                                          |                           |                                          |     |                                                                                 |

| AINM              | 9                                        | 9                                        | 9                         | 9                                        | I   | ADC input ground                                                                |

| AINP              | 8                                        | 8                                        | 8                         | 8                                        | I   | Signal input to ADC                                                             |

| DIGITAL CO        | NTROL SIGNAL                             | .s                                       |                           |                                          |     |                                                                                 |

| CS                | 31                                       | 31                                       | 23                        | 23                                       | I   | Chip-select input                                                               |

| SCLK              | 32                                       | 32                                       | 24                        | 24                                       | I   | Serial clock input                                                              |

| SDI               | 33                                       | 33                                       | 25                        | 25                                       | I   | Serial data input                                                               |

| SDO               | 34                                       | 34                                       | 26                        | 26                                       | 0   | Serial data output                                                              |

| GENERAL P         | URPOSE INPUT                             | S AND OUTPU                              | TS <sup>(1)</sup>         |                                          | ,   |                                                                                 |

| GPIO0             |                                          |                                          |                           |                                          | I/O | General-purpose input or output                                                 |

| High or low alarm | 37                                       | 37                                       | 29                        | 29                                       | 0   | Active high output indicating high alarm or low alarm, depending on programming |

| GPIO1             | 38                                       | 38                                       | 30                        | 30                                       | I/O | General-purpose input or output                                                 |

| Low alarm         | 36                                       | 36                                       | 30                        | 30                                       | 0   | Active high output indicating low alarm                                         |

| GPIO2             | 1                                        | 1                                        | 1                         | 1                                        | I/O | General-purpose input or output                                                 |

| Range             |                                          | '                                        | '                         | '                                        | I   | Selects range: High → Range 2; Low → Range 1                                    |

| GPIO3             | 2                                        | 2                                        | 2                         | 2                                        | I/O | Genera-purpose input or output                                                  |

| PD                |                                          |                                          |                           |                                          | I   | Active low power-down input                                                     |

| MULTIPLEXI        | ER                                       |                                          |                           |                                          |     |                                                                                 |

| Ch0               | 28                                       | 28                                       | 20                        | 20                                       | 1   |                                                                                 |

| Ch1               | 27                                       | 27                                       | 19                        | 18                                       | 1   |                                                                                 |

| Ch2               | 26                                       | 26                                       | 18                        | 14                                       | ı   |                                                                                 |

| Ch3               | 25                                       | 25                                       | 17                        | 12                                       | I   |                                                                                 |

| Ch4               | 24                                       | 24                                       | 14                        | _                                        | I   |                                                                                 |

| Ch5               | 23                                       | 23                                       | 13                        | _                                        | I   |                                                                                 |

| Ch6               | 22                                       | 22                                       | 12                        | _                                        | I   |                                                                                 |

| Ch7               | 21                                       | 21                                       | 11                        | _                                        | I   | Analog channels for multiplexer                                                 |

| Ch8               | 18                                       | 18                                       | _                         | _                                        | I   |                                                                                 |

| Ch9               | 17                                       | 17                                       | _                         | _                                        | 1   |                                                                                 |

| Ch10              | 16                                       | 16                                       | _                         | _                                        | 1   |                                                                                 |

| Ch11              | 15                                       | 15                                       | _                         | _                                        |     |                                                                                 |

| Ch12              | 14                                       | _                                        | _                         | _                                        | - 1 |                                                                                 |

| Ch13              | 13                                       | _                                        | _                         | _                                        | 1   |                                                                                 |

| Ch14              | 12                                       | _                                        | _                         | _                                        | 1   |                                                                                 |

| Ch15              | 11                                       | _                                        | _                         | _                                        | 1   | N. W. L.                                                                        |

| MXO               | 7                                        | 7                                        | 7                         | 7                                        | 0   | Multiplexer output                                                              |

| NC PINS           |                                          | 4.4                                      | 4.5                       | 4.4                                      |     |                                                                                 |

|                   | _                                        | 11                                       | 15                        | 11                                       |     |                                                                                 |

|                   |                                          | 12                                       | 16                        | 13                                       |     |                                                                                 |

| NC                |                                          | 13                                       | _                         | 15                                       | _   | Pins internally not connected, do not float these pins                          |

|                   |                                          | 14                                       | _                         | 16                                       |     |                                                                                 |

|                   |                                          | _                                        | _                         | 17                                       |     |                                                                                 |

|                   |                                          | _                                        | _                         | 19                                       |     |                                                                                 |

<sup>(1)</sup> These pins have programmable dual functionality. See Table 12 for functionality programming.

### Pin Functions (continued)

|           |                                          | PIN                                      |                           |                                          |     |                      |

|-----------|------------------------------------------|------------------------------------------|---------------------------|------------------------------------------|-----|----------------------|

|           | NUMBER                                   |                                          |                           |                                          |     |                      |

| NAME      | ADS7953-Q1,<br>ADS7957-Q1,<br>ADS7961-Q1 | ADS7952-Q1,<br>ADS7956-Q1,<br>ADS7960-Q1 | ADS7951-Q1,<br>ADS7959-Q1 | ADS7950-Q1,<br>ADS7954-Q1,<br>ADS7958-Q1 | 1/0 | DESCRIPTION          |

| POWER SUP | PLY AND GRO                              | UND                                      |                           |                                          |     |                      |

|           | 6                                        | 6                                        | 6                         | 6                                        |     |                      |

|           | 10                                       | 10                                       | 10                        | 10                                       |     |                      |

| AGND      | 19                                       | 19                                       | 22                        | 22                                       | _   | Analog ground        |

|           | 20                                       | 20                                       | _                         | _                                        |     |                      |

|           | 30                                       | 30                                       | _                         | _                                        |     |                      |

| BDGND     | 35                                       | 35                                       | 27                        | 27                                       | _   | Digital ground       |

| +VA       | 5                                        | 5                                        | 5                         | 5                                        |     | Analog navier cumply |

| +VA       | 29                                       | 29                                       | 21                        | 21                                       | _   | Analog power supply  |

| +VBD      | 36                                       | 36                                       | 28                        | 28                                       | _   | Digital I/O supply   |

| REFERENCE | •                                        |                                          |                           |                                          |     |                      |

| REFM      | 3                                        | 3                                        | 3                         | 3                                        | I   | Reference ground     |

| REFP      | 4                                        | 4                                        | 4                         | 4                                        | I   | Reference input      |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted).

| ore: eperaning nee an term           | perature range (united this mea). |      |                   |      |

|--------------------------------------|-----------------------------------|------|-------------------|------|

|                                      |                                   | MIN  | MAX               | UNIT |

| Supply voltage to ground             | +VA to AGND, +VBD to BDGND        | -0.3 | 7                 | V    |

| Signal input                         | AINP or CHn to AGND               | -0.3 | $V_{(+VA)} + 0.3$ | V    |

| Digital input                        | To BDGND                          | -0.3 | 7                 | V    |

| Digital output                       | To BDGND                          | -0.3 | $V_{(+VA)} + 0.3$ | V    |

| Junction temperature, T <sub>J</sub> |                                   |      | 150               | °C   |

<sup>(1)</sup> Stresses beyond those listed as *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated as *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 Handling Ratings

|                    | inig itatilige          |                                                                    |                                                                                                 |      |     |      |

|--------------------|-------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|-----|------|

|                    |                         |                                                                    |                                                                                                 | MIN  | MAX | UNIT |

| $T_{stg}$          | Storage temperatu       | ire range                                                          | range                                                                                           |      |     |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup> , level H2 |                                                                                                 | -2   | 2   | kV   |

|                    |                         | Charged-device model (CDM),<br>per AEC Q100-001, level C4B         | Corner pins<br>(1, 15, 16, and 30 for 30-pin packages<br>1, 19, 20, and 38 for 38-pin packages) | -750 | 750 | ٧    |

|                    |                         |                                                                    | All pins                                                                                        | -500 | 500 |      |

<sup>(1)</sup> AEC Q100-002 indicates HBM stressing is done in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                     |                             | MIN | NOM | MAX         | UNIT |

|---------------------|-----------------------------|-----|-----|-------------|------|

| V <sub>(+VA)</sub>  | Analog power-supply voltage | 2.7 | 3.3 | 5.25        | V    |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage  | 1.7 | 3.3 | $V_{(+VA)}$ | V    |

| $V_{(REF)}$         | Reference voltage           | 2   | 2.5 | 3           | V    |

| $f_{(SCLK)}$        | SCLK frequency              |     |     | 20          | MHz  |

| $T_A$               | Operating temperature range | -40 |     | 125         | °C   |

#### 7.4 Thermal Information

|                        |                                              | ADS79       |             |      |

|------------------------|----------------------------------------------|-------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DBT (TSSOP) | DBT (TSSOP) | UNIT |

|                        |                                              | 38 PINS     | 30 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 83.6        | 89.8        |      |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 29.8        | 22.9        |      |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 44.7        | 43.1        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 2.9         | 0.8         | C/VV |

| ΨЈВ                    | Junction-to-board characterization parameter | 44.1        | 42.5        |      |

| $R_{\theta JC(bot)}$   | Junction-to-case (bottom) thermal resistance | n/a         | n/a         |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

# 7.5 Electrical Characteristics: ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1

$V_{\text{(+VA)}} = 2.7 \text{ V}$  to 5.25 V,  $V_{\text{(+VBD)}} = 1.7 \text{ V}$  to  $V_{\text{(+VA)}}$ ,  $V_{\text{ref}} = 2.5 \text{ V} \pm 0.1 \text{ V}$ ,  $T_{\text{A}} = -40 ^{\circ}\text{C}$  to 125 °C,  $f_{\text{sample}} = 1 \text{ MHz}$  (unless otherwise noted)

|       | PARAMETER                            | TEST CONDITIONS                          | MIN  | TYP   | MAX                      | UNIT               |

|-------|--------------------------------------|------------------------------------------|------|-------|--------------------------|--------------------|

| ANALO | G INPUT                              |                                          | '    |       |                          |                    |

|       | Full-scale input span <sup>(1)</sup> | Range 1                                  | 0    |       | $V_{ref}$                | V                  |

|       | Full-scale input span ??             | Range 2 while 2 x V <sub>ref</sub> ≤ +VA | 0    |       | 2 × V <sub>ref</sub>     | V                  |

|       |                                      | Range 1                                  | -0.2 |       | V <sub>ref</sub> + 0.2   | V                  |

|       | Absolute input range                 | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | -0.2 |       | $2 \times V_{ref} + 0.2$ | V                  |

|       | Input capacitance                    |                                          |      | 15    |                          | ρF                 |

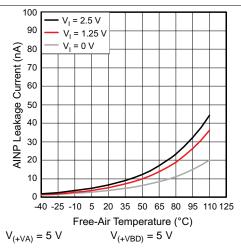

|       | Input leakage current                | T <sub>A</sub> = 125°C                   |      | 61    |                          | nA                 |

| SYSTE | // PERFORMANCE                       |                                          |      |       |                          |                    |

|       | Resolution                           |                                          |      | 12    |                          | Bits               |

|       | No missing codes                     |                                          | 11   |       |                          | Bits               |

|       | Integral linearity                   |                                          | -1.5 | ±0.75 | 1.5                      | LSB <sup>(2)</sup> |

|       | Differential linearity               |                                          | -2   | ±0.75 | 1.5                      | LSB                |

|       | Offset error <sup>(3)</sup>          |                                          | -3.5 | ±1.1  | 3.5                      | LSB                |

|       | Gain error                           | Range 1                                  | -2   | ±0.2  | 2                        | LSB                |

|       | Gain enoi                            | Range 2                                  |      | ±0.2  |                          | LSB                |

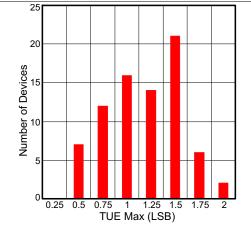

| TUE   | Total unadjusted error               |                                          |      | ±2    |                          | LSB                |

| SAMPL | NG DYNAMICS                          |                                          |      |       |                          | •                  |

|       | Conversion time                      | 20-MHz SCLK                              |      |       | 800                      | ns                 |

|       | Acquisition time                     |                                          | 325  |       |                          | ns                 |

|       | Maximum throughput rate              | 20-MHz SCLK                              |      |       | 1                        | MHz                |

|       | Aperture delay                       |                                          |      | 5     |                          | ns                 |

|       | Step response                        |                                          |      | 150   |                          | ns                 |

|       | Over voltage recovery                |                                          |      | 150   |                          | ns                 |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

<sup>(2)</sup> LSB means least-significant bit.

<sup>(3)</sup> Measured relative to an ideal full-scale input

**STRUMENTS**

# Electrical Characteristics: ADS7950-Q1, ADS7951-Q1, ADS7952-Q1, ADS7953-Q1 (continued)

$V_{\text{(+VA)}}$  = 2.7 V to 5.25 V,  $V_{\text{(+VBD)}}$  = 1.7 V to  $V_{\text{(+VA)}}$ ,  $V_{\text{ref}}$  = 2.5 V ± 0.1 V,  $T_{\text{A}}$  = -40°C to 125°C,  $f_{\text{sample}}$  = 1 MHz (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                                              | MIN                          | TYP          | MAX                | UNIT  |

|---------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------|--------------|--------------------|-------|

| DYNAMIC             | C CHARACTERISTICS                           |                                                                                                                              |                              |              |                    |       |

| THD                 | Total harmonic distortion (4)               | 100 kHz                                                                                                                      |                              | -82          |                    | dB    |

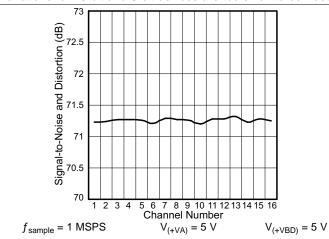

| SNR                 | Signal-to-noise ratio                       | 100 kHz                                                                                                                      | 70                           | 71.7         |                    | dB    |

| SINAD               | Signal-to-noise + distortion                | 100 kHz                                                                                                                      | 68                           | 71.3         |                    | dB    |

| SFDR                | Spurious-free dynamic range                 | 100 kHz                                                                                                                      |                              | 84           |                    | dB    |

|                     | Small signal bandwidth                      | At –3 dB                                                                                                                     |                              | 47           |                    | MHz   |

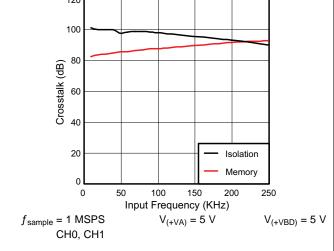

|                     |                                             | Any off-channel with 100 kHz. Full-scale input to channel being sampled with DC input (isolation crosstalk).                 |                              | -95          |                    | dB    |

|                     | Channel-to-channel crosstalk                | From previously sampled to channel with 100 kHz. Full-scale input to channel being sampled with DC input (memory crosstalk). |                              | -85          |                    | dB    |

| EXTERN              | AL REFERENCE INPUT                          |                                                                                                                              |                              |              |                    |       |

| V <sub>ref</sub>    | Reference voltage at REFP <sup>(5)</sup>    |                                                                                                                              | 2                            | 2.5          | 3                  | V     |

| R <sub>ref</sub>    | Reference resistance                        |                                                                                                                              |                              | 100          |                    | kΩ    |

| ALARM S             | SETTING                                     |                                                                                                                              |                              |              |                    |       |

|                     | Higher threshold range                      |                                                                                                                              | 0                            |              | FFC                | Hex   |

|                     | Lower threshold range                       |                                                                                                                              | 0                            |              | FFC                | Hex   |

| DIGITAL             | INPUT/OUTPUT (CMOS Logic Family)            |                                                                                                                              |                              |              |                    |       |

| $V_{IH}$            | High logic-level input voltage              |                                                                                                                              | 0.7 x<br>V <sub>(+VBD)</sub> |              |                    | V     |

| .,                  |                                             | V <sub>(+VA)</sub> = 5 V                                                                                                     |                              |              | 0.8                | V     |

| $V_{IL}$            | Low logic-level input voltage               | V <sub>(+VA)</sub> = 3 V                                                                                                     |                              |              | 0.4                | V     |

| V <sub>OH</sub>     | High logic-level output voltage             | At source current (I <sub>S</sub> ) = 200 μA                                                                                 | V <sub>(+VBD)</sub> - 0.2    |              |                    | V     |

| V <sub>OL</sub>     | Low logic-level output voltage              | At I <sub>sink</sub> = 200 μA                                                                                                | 0.4                          |              |                    | V     |

|                     | Data format MSB first                       |                                                                                                                              |                              | MSB first    |                    |       |

| POWER               | SUPPLY REQUIREMENTS                         |                                                                                                                              |                              |              | <del>!</del>       |       |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                                                                              | 2.7                          | 3.3          | 5.25               | V     |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                                                                              | 1.7                          | 3.3          | V <sub>(+VA)</sub> | V     |

|                     |                                             | At $V_{(+VA)} = 2.7 \text{ V}$ to 3.6 V and 1-MHz throughput                                                                 |                              | 1.8          |                    | mA    |

|                     | 0 1 11                                      | At $V_{(+VA)} = 2.7 \text{ V}$ to 3.6 V static state                                                                         |                              | 1.05         |                    | mA    |

| $I_{(+VA)}$         | Supply current (normal mode)                | At $V_{(+VA)} = 4.7 \text{ V}$ to 5.25 V and 1-MHz throughput                                                                |                              | 2.3          | 3                  | mA    |

|                     |                                             | At $V_{(+VA)} = 4.7 \text{ V}$ to 5.25 V static state                                                                        |                              | 1.1          | 1.5                | mA    |

|                     | Power-down state supply current             |                                                                                                                              |                              | 1            |                    | μA    |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | V <sub>(+VA)</sub> = 5.25 V, f <sub>sample</sub> = 1 MHz                                                                     |                              | 1            |                    | mA    |

|                     | Power-up time                               |                                                                                                                              |                              |              | 1                  | μs    |

|                     | Invalid conversions after power up or reset |                                                                                                                              |                              |              | 1                  | cycle |

|                     | Latch-up                                    |                                                                                                                              | JES                          | SD78 class I |                    |       |

| TEMPER              | ATURE RANGE                                 |                                                                                                                              |                              |              |                    |       |

|                     | Specified performance                       |                                                                                                                              | -40                          |              | 125                | °C    |

<sup>(4)</sup> Calculated on the first nine harmonics of the input frequency.

<sup>(5)</sup> The device is designed to operate over V<sub>ref</sub> = 2 V to 3 V. However, lower noise performance can be expected at V<sub>ref</sub> < 2.4 V, because of SNR degradation resulting from lowered signal range.</p>

ZHCSCF3A -MAY 2014-REVISED AUGUST 2014

## 7.6 Electrical Characteristics: ADS7954-Q1, ADS7956-Q1, ADS7957-Q1

$V_{\text{(+VA)}} = 2.7 \text{ V to } 5.25 \text{ V}, V_{\text{(+VBD)}} = 1.7 \text{ V to } V_{\text{(+VA)}}, V_{\text{ref}} = 2.5 \text{ V} \pm 0.1 \text{ V}, T_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } 125 ^{\circ}\text{C}, f_{\text{sample}} = 1 \text{ MHz (unless otherwise } 1.00 ^{\circ}\text{C})$

|                  | PARAMETER                            | TEST CONDITIONS                                                                                           | MIN                          | TYP      | MAX                       | UNIT               |

|------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------|----------|---------------------------|--------------------|

| ANALOG           |                                      |                                                                                                           |                              |          |                           |                    |

|                  |                                      | Range 1                                                                                                   | 0                            |          | $V_{ref}$                 | V                  |

|                  | Full-scale input span <sup>(1)</sup> | Range 2 while 2 × V <sub>ref</sub> ≤ +VA                                                                  | 0                            |          | 2 × V <sub>ref</sub>      | V                  |

|                  |                                      | Range 1                                                                                                   | -0.2                         |          | V <sub>ref</sub> + 0.2    | V                  |

|                  | Absolute input range                 | Range 2 while 2 × V <sub>ref</sub> ≤ +VA                                                                  | -0.2                         |          | 2 × V <sub>ref</sub> +0.2 | V                  |

|                  | Input capacitance                    | Traingo 2 Willio 2 X Vier 2 TV/Y                                                                          | 0.2                          | 15       | Z X V rer 10.2            | ρF                 |

|                  | Input leakage current                | T <sub>A</sub> = 125°C                                                                                    |                              | 61       |                           | nA                 |

| SYSTEM           | PERFORMANCE                          | 1 <sub>A</sub> = 125 0                                                                                    |                              | 01       |                           | 11/1               |

| 3131EM           | Resolution                           |                                                                                                           |                              | 10       |                           | Bits               |

|                  | No missing codes                     |                                                                                                           | 10                           | 10       |                           | Bits               |

|                  | -                                    |                                                                                                           | -0.5                         | ±0.2     | 0.5                       | LSB <sup>(2)</sup> |

|                  | Integral linearity                   |                                                                                                           |                              |          |                           |                    |

|                  | Differential linearity               |                                                                                                           | -0.5                         | ±0.2     | 0.5                       | LSB                |

|                  | Offset error <sup>(3)</sup>          |                                                                                                           | -1.5                         | ±0.5     | 1.5                       | LSB                |

|                  | Gain error                           | Range 1                                                                                                   | -1                           | ±0.1     | 1                         | LSB                |

|                  |                                      | Range 2                                                                                                   |                              | ±0.1     |                           | LSB                |

| SAMPLIN          | NG DYNAMICS                          |                                                                                                           |                              |          |                           |                    |

|                  | Conversion time                      | 20-MHz SCLK                                                                                               |                              |          | 800                       | ns                 |

|                  | Acquisition time                     |                                                                                                           | 325                          |          |                           | ns                 |

|                  | Maximum throughput rate              | 20-MHz SCLK                                                                                               |                              |          | 1                         | MHz                |

|                  | Aperture delay                       |                                                                                                           |                              | 5        |                           | ns                 |

|                  | Step response                        |                                                                                                           |                              | 150      |                           | ns                 |

|                  | Over voltage recovery                |                                                                                                           |                              | 150      |                           | ns                 |

| DYNAMI           | C CHARACTERISTICS                    |                                                                                                           | 1                            |          |                           |                    |

| THD              | Total harmonic distortion (4)        | 100 kHz                                                                                                   |                              | -80      |                           | dB                 |

| SNR              | Signal-to-noise ratio                | 100 kHz                                                                                                   | 60                           |          |                           | dB                 |

| SINAD            | Signal-to-noise + distortion         | 100 kHz                                                                                                   | 60                           |          |                           | dB                 |

| SFDR             | Spurious-free dynamic range          | 100 kHz                                                                                                   |                              | 82       |                           | dB                 |

|                  | Full-power bandwidth                 | At –3 dB                                                                                                  |                              | 47       |                           | MHz                |

|                  | Channel-to-channel crosstalk         | Any off-channel with 100 kHz. Full-scale input to channel being sampled with dc input.                    |                              | -95      |                           | dB                 |

|                  | Chainer-to-chainer crosstaik         | From previously sampled to channel with 100 kHz. Full-scale input to channel being sampled with dc input. |                              | -85      |                           | dB                 |

| EXTERN           | AL REFERENCE INPUT                   |                                                                                                           |                              |          |                           |                    |

| V <sub>ref</sub> | Reference voltage at REFP            |                                                                                                           | 2                            | 2.5      | 3                         | V                  |

| R <sub>ref</sub> | Reference resistance                 |                                                                                                           |                              | 100      |                           | kΩ                 |

| ALARM            | SETTING                              | ·                                                                                                         |                              |          |                           |                    |

|                  | Higher threshold range               |                                                                                                           | 000                          |          | FFC                       | Hex                |

|                  | Lower threshold range                |                                                                                                           | 000                          |          | FFC                       | Hex                |

| DIGITAL          | INPUT/OUTPUT (CMOS Logic Famil       | у)                                                                                                        |                              |          |                           |                    |

| V <sub>IH</sub>  | High logic-level input voltage       |                                                                                                           | 0.7 ×<br>V <sub>(+VBD)</sub> |          |                           | V                  |

|                  |                                      | V <sub>(+VBD)</sub> = 5 V                                                                                 | (,,,,,,)                     |          | 0.8                       | V                  |

| V <sub>IL</sub>  | Low logic-level input voltage        | V <sub>(+VBD)</sub> = 3 V                                                                                 |                              |          | 0.4                       | V                  |

| $V_{OH}$         | High logic-level output voltage      | At source current (I <sub>S</sub> ) = 200 μA                                                              | V <sub>(+VBD)</sub> –<br>0.2 |          |                           | V                  |

| V <sub>OL</sub>  | Low logic-level output voltage       | At I <sub>sink</sub> = 200 μA                                                                             | 0.4                          |          |                           | V                  |

| -                | Data format MSB first                |                                                                                                           |                              | MSB firs | t                         |                    |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

<sup>(2)</sup> LSB means least significant bit.

<sup>(3)</sup> Measured relative to an ideal full-scale input

Calculated on the first nine harmonics of the input frequency. (4)

## Electrical Characteristics: ADS7954-Q1, ADS7956-Q1, ADS7957-Q1 (continued)

$V_{\text{(+VA)}}$  = 2.7 V to 5.25 V,  $V_{\text{(+VBD)}}$  = 1.7 V to  $V_{\text{(+VA)}}$ ,  $V_{\text{ref}}$  = 2.5 V ± 0.1 V,  $T_{\text{A}}$  = -40°C to 125°C,  $f_{\text{sample}}$  = 1 MHz (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                        | MIN | TYP          | MAX                | UNIT  |

|---------------------|---------------------------------------------|------------------------------------------------------------------------|-----|--------------|--------------------|-------|

| POWER S             | SUPPLY REQUIREMENTS                         |                                                                        |     |              |                    |       |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                        | 2.7 | 3.3          | 5.25               | V     |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                        | 1.7 | 3.3          | V <sub>(+VA)</sub> | V     |

|                     |                                             | At V <sub>(+VA)</sub> = 2.7 V to 3.6 V and 1-MHz throughput            |     | 1.8          |                    | mA    |

|                     | Contain account (a contain                  | At $V_{(+VA)} = 2.7 \text{ V to } 3.6 \text{ V static state}$          |     | 1.05         | 1                  | mA    |

| I <sub>(+VA)</sub>  | Supply current (normal mode)                | At V <sub>(+VA)</sub> = 4.7 V to 5.25 V and 1-MHz throughput           |     | 2.3          | 3                  | mA    |

|                     |                                             | At $V_{(+VA)} = 4.7 \text{ V to } 5.25 \text{ V static state}$         |     | 1.1          | 1.5                | mA    |

|                     | Power-down state supply current             |                                                                        |     | 1            |                    | μΑ    |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | $V_{\text{(+VA)}} = 5.25 \text{ V}, f_{\text{sample}} = 1 \text{ MHz}$ |     | 1            |                    | mA    |

|                     | Power-up time                               |                                                                        |     |              | 1                  | μs    |

|                     | Invalid conversions after power up or reset |                                                                        |     |              | 1                  | cycle |

|                     | Latch-up                                    |                                                                        | JE  | SD78 class I |                    |       |

| TEMPERA             | ATURE RANGE                                 |                                                                        | •   |              |                    |       |

|                     | Specified performance                       |                                                                        | -40 |              | 125                | °C    |

## 7.7 Electrical Characteristics: ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1

$V_{\text{(+VA)}} = 2.7 \text{ V to } 5.25 \text{ V}, V_{\text{(+VBD)}} = 1.7 \text{ V to } V_{\text{(+VA)}}, V_{\text{ref}} = 2.5 \text{ V} \pm 0.1 \text{ V}, T_{\text{A}} = -40 ^{\circ}\text{C} \text{ to } 125 ^{\circ}\text{C}, f_{\text{sample}} = 1 \text{ MHz (unless otherwise noted)}$

| PARAMETER                            | TEST CONDITIONS                          | MIN   | TYP  | MAX                           | UNIT               |

|--------------------------------------|------------------------------------------|-------|------|-------------------------------|--------------------|

| ANALOG INPUT                         |                                          |       |      |                               |                    |

| Full-scale input span <sup>(1)</sup> | Range 1                                  | 0     |      | $V_{ref}$                     | V                  |

| Full-scale input span ···            | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | 0     |      | 2 × V <sub>ref</sub>          | V                  |

| About do investment                  | Range 1                                  | -0.20 |      | V <sub>ref</sub> + 0.2        | V                  |

| Absolute input range                 | Range 2 while 2 × V <sub>ref</sub> ≤ +VA | -0.20 |      | 2 × V <sub>ref</sub><br>+ 0.2 | V                  |

| Input capacitance                    |                                          |       | 15   |                               | ρF                 |

| Input leakage current                | T <sub>A</sub> = 125°C                   |       | 61   |                               | nA                 |

| SYSTEM PERFORMANCE                   |                                          | ·     |      |                               |                    |

| Resolution                           |                                          |       | 8    |                               | Bits               |

| No missing codes                     |                                          | 8     |      |                               | Bits               |

| Integral linearity                   |                                          | -0.3  | ±0.1 | 0.3                           | LSB <sup>(2)</sup> |

| Differential linearity               |                                          | -0.3  | ±0.1 | 0.3                           | LSB                |

| Offset error <sup>(3)</sup>          |                                          | -0.5  | ±0.2 | 0.5                           | LSB                |

| 0-1                                  | Range 1                                  | -0.6  | ±0.1 | 0.6                           | LSB                |

| Gain error                           | Range 2                                  |       | ±0.1 |                               | LSB                |

| SAMPLING DYNAMICS                    | •                                        |       |      |                               |                    |

| Conversion time                      | 20-MHz SCLK                              |       |      | 800                           | ns                 |

| Acquisition time                     |                                          | 325   |      |                               | ns                 |

| Maximum throughput rate              | 20-MHz SCLK                              |       |      | 1                             | MHz                |

| Aperture delay                       |                                          |       | 5    |                               | ns                 |

| Step response                        |                                          |       | 150  |                               | ns                 |

| Over voltage recovery                |                                          |       | 150  |                               | ns                 |

<sup>(1)</sup> Ideal input span; does not include gain or offset error.

<sup>(2)</sup> LSB means least significant bit.

<sup>(3)</sup> Measured relative to an ideal full-scale input

# Electrical Characteristics: ADS7958-Q1, ADS7959-Q1, ADS7960-Q1, ADS7961-Q1 (continued)

$V_{\text{(+VA)}}$  = 2.7 V to 5.25 V,  $V_{\text{(+VBD)}}$  = 1.7 V to  $V_{\text{(+VA)}}$ ,  $V_{\text{ref}}$  = 2.5 V ± 0.1 V,  $T_{\text{A}}$  = -40°C to 125°C,  $f_{\text{sample}}$  = 1 MHz (unless otherwise noted)

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                           | MIN                          | TYP      | MAX                | UNIT  |

|---------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------|------------------------------|----------|--------------------|-------|

| DYNAMI              | C CHARACTERISTICS                           |                                                                                                           |                              |          |                    |       |

| THD                 | Total harmonic distortion (4)               | 100 kHz                                                                                                   |                              | -75      |                    | dB    |

| SNR                 | Signal-to-noise ratio                       | 100 kHz                                                                                                   | 49                           |          |                    | dB    |

| SINAD               | Signal-to-noise + distortion                | 100 kHz                                                                                                   | 49                           |          |                    | dB    |

| SFDR                | Spurious-free dynamic range                 | 100 kHz                                                                                                   |                              | -78      |                    | dB    |

|                     | Full-power bandwidth                        | At –3 dB                                                                                                  |                              | 47       |                    | MHz   |

|                     | Observation sharmed assertable              | Any off-channel with 100 kHz. Full-scale input to channel being sampled with dc input.                    |                              | -95      |                    | dB    |

|                     | Channel-to-channel crosstalk                | From previously sampled to channel with 100 kHz. Full-scale input to channel being sampled with dc input. |                              | -85      |                    | dB    |

| EXTERN              | IAL REFERENCE INPUT                         |                                                                                                           |                              |          |                    |       |

| Vref                | reference voltage at REFP                   |                                                                                                           | 2                            | 2.5      | 3                  | V     |

|                     | Reference resistance                        |                                                                                                           |                              | 100      |                    | kΩ    |

| ALARM               | SETTING                                     |                                                                                                           |                              |          |                    |       |

|                     | Higher threshold range                      |                                                                                                           | 000                          |          | FF                 | Hex   |

|                     | Lower threshold range                       |                                                                                                           | 000                          |          | FF                 | Hex   |

| DIGITAL             | . INPUT/OUTPUT (CMOS Logic Family)          |                                                                                                           |                              |          | '                  |       |

| V <sub>IH</sub>     | High logic-level input voltage              |                                                                                                           | 0.7 ×<br>V <sub>(+VBD)</sub> |          |                    | V     |

| .,                  | I am la sia lawal isan dan alƙara           | V <sub>(+VBD)</sub> = 5 V                                                                                 |                              |          | 0.8                | V     |

| V <sub>IL</sub>     | Low logic-level input voltage               | V <sub>(+VBD)</sub> = 3 V                                                                                 |                              |          | 0.4                | V     |

| V <sub>OH</sub>     | High logic-level output voltage             | At source current (I <sub>S</sub> ) = 200 μA                                                              | V <sub>(+VBD)</sub> – 0.2    |          |                    | V     |

| V <sub>OL</sub>     | Low logic-level output voltage              | At I <sub>sink</sub> = 200 μA                                                                             | 0.4                          |          |                    | V     |

|                     | Data format                                 |                                                                                                           | MS                           | BB first |                    |       |

| POWER               | SUPPLY REQUIREMENTS                         |                                                                                                           |                              |          |                    |       |

| V <sub>(+VA)</sub>  | Analog power-supply voltage                 |                                                                                                           | 2.7                          | 3.3      | 5.25               | V     |

| V <sub>(+VBD)</sub> | Digital I/O-supply voltage                  |                                                                                                           | 1.7                          | 3.3      | V <sub>(+VA)</sub> | V     |

|                     |                                             | At V <sub>(+VA)</sub> = 2.7 V to 3.6 V and 1-MHz throughput                                               |                              | 1.8      |                    | mA    |

|                     | C                                           | At V <sub>(+VA)</sub> = 2.7 V to 3.6 V static state                                                       |                              | 1.05     |                    | mA    |

| I <sub>(+VA)</sub>  | Supply current (normal mode)                | At V <sub>(+VA)</sub> = 4.7 V to 5.25 V and 1-MHz throughput                                              |                              | 2.3      | 3                  | mA    |

|                     |                                             | At V <sub>(+VA)</sub> = 4.7 V to 5.25 V static state                                                      |                              | 1.1      | 1.5                | mA    |

|                     | Power-down state supply current             |                                                                                                           |                              | 1        |                    | μA    |

| I <sub>(+VBD)</sub> | Digital I/O-supply current                  | V <sub>(+VA)</sub> = 5.25 V, f <sub>sample</sub> = 1 MHz                                                  |                              | 1        |                    | mA    |

|                     | Power-up time                               |                                                                                                           |                              |          | 1                  | μs    |

|                     | Invalid conversions after power up or reset |                                                                                                           |                              |          | 1                  | cycle |

|                     | Latch-up                                    |                                                                                                           | JESD                         | 78 class | I                  |       |

| TEMPER              | RATURE RANGE                                |                                                                                                           |                              |          | l                  |       |

|                     | Specified performance                       |                                                                                                           | -40                          |          | 125                | °C    |

|                     |                                             | 1                                                                                                         |                              |          |                    |       |

<sup>(4)</sup> Calculated on the first nine harmonics of the input frequency.

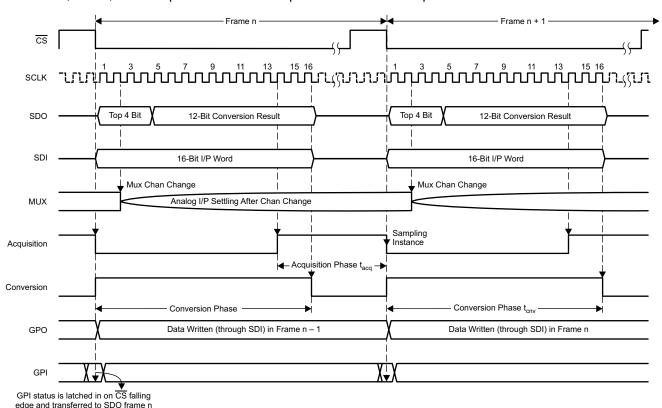

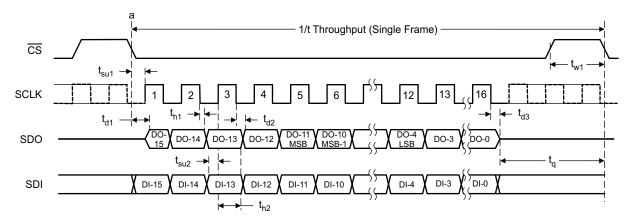

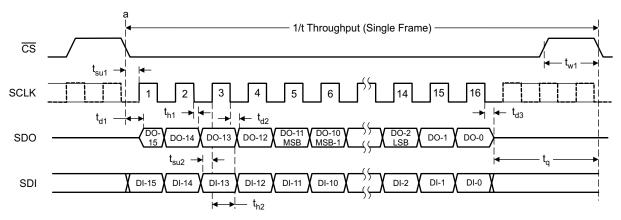

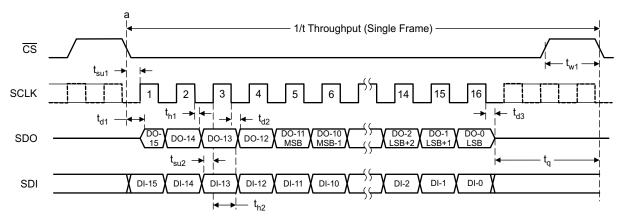

## 7.8 Timing Requirements

All specifications typical at  $-40^{\circ}$ C to  $125^{\circ}$ C,  $V_{(+VA)} = 2.7$  V to 5.25 V (unless otherwise specified). See Figure 45, Figure 46, Figure 47, and Figure 48.

|                  | PARAMETER <sup>(1)(2)</sup>                                                          | MIN                               | TYP | MAX | UNIT |      |

|------------------|--------------------------------------------------------------------------------------|-----------------------------------|-----|-----|------|------|

|                  |                                                                                      | $V_{(+VBD)} = 1.8 \text{ V}$      |     |     |      |      |

| t <sub>c</sub>   | Conversion time                                                                      | $V_{\text{(+VBD)}} = 3 \text{ V}$ |     |     | 16   | SCLK |

|                  |                                                                                      | $V_{\text{(+VBD)}} = 5 \text{ V}$ |     |     | 16   | SCLK |

|                  |                                                                                      | V <sub>(+VBD)</sub> = 1.8 V       | 40  |     |      | ns   |

| t <sub>q</sub>   | Minimum quiet sampling time needed from bus Tri-state to<br>start of next conversion | V <sub>(+VBD)</sub> = 3 V         | 40  |     |      | ns   |

|                  |                                                                                      | V <sub>(+VBD)</sub> = 5 V         | 40  |     |      | ns   |

|                  |                                                                                      | V <sub>(+VBD)</sub> = 1.8 V       |     |     | 38   | ns   |

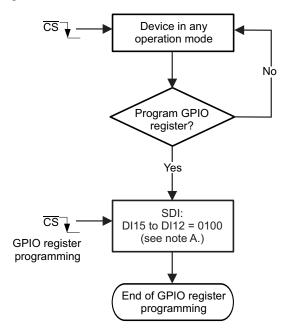

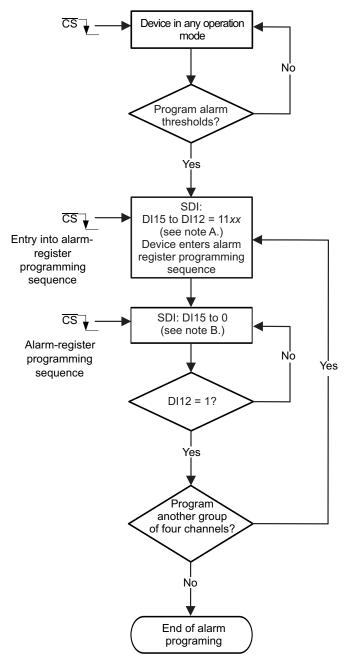

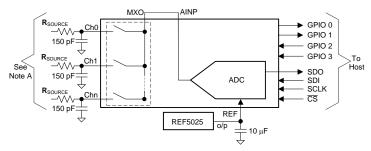

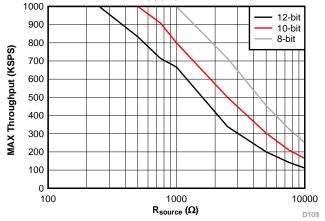

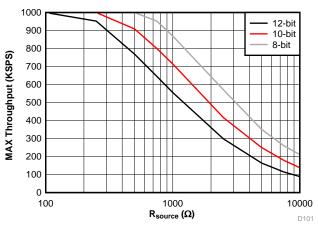

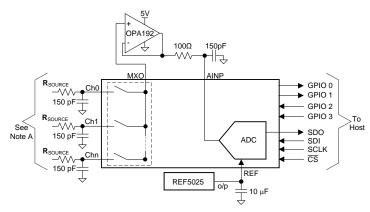

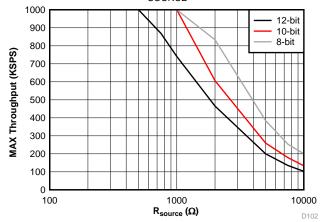

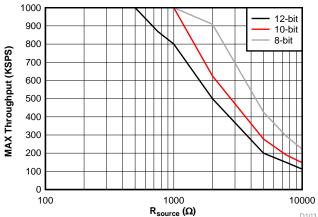

| t <sub>d1</sub>  | Delay time, CS low to first data (DO-15) out                                         | V <sub>(+VBD)</sub> = 3 V         |     |     | 27   | ns   |