## LMC7221 Tiny CMOS Comparator with Rail-To-Rail Input and Open Drain Output

Check for Samples: [LMC7221](#)

### FEATURES

- Tiny 5-Pin SOT-23 package saves space

- Package is less than 1.43 mm thick

- Ensured specs at 2.7V, 5V, 15V supplies

- Typical supply current 7  $\mu$ A at 5V

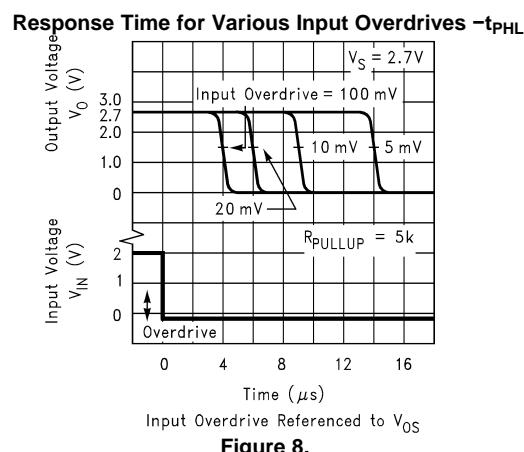

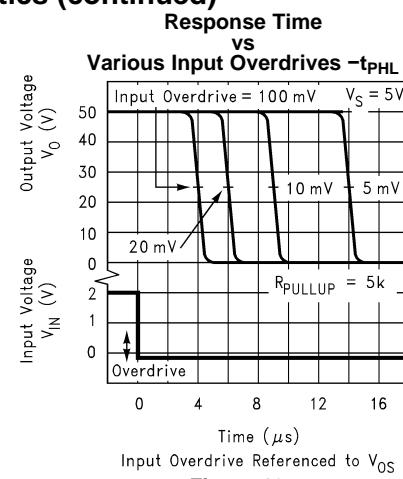

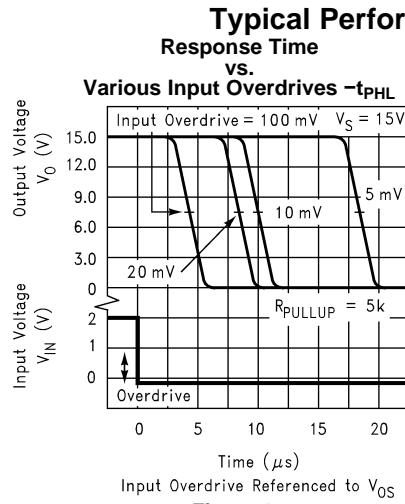

- Response time of 4  $\mu$ s at 5V

- LMC7221—open drain output

- Input common-mode range beyond  $V^-$  and  $V^+$

- Low input current

### APPLICATIONS

- Mixed voltage battery powered products

- Notebooks and PDAs

- PCMCIA cards

- Mobile communications

- Alarm and security circuits

- Driving low current LEDs

- Direct sensor interface

### Connection Diagram

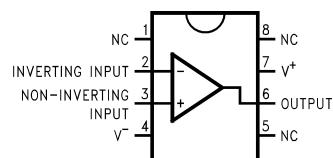

8-Pin SOIC - Top View

Figure 1. See Package Number D0008A

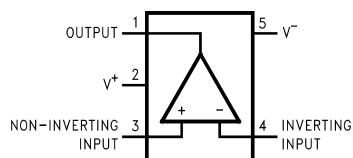

5-Pin SOT-23 - Top View

Figure 2. See Package Number DBV0005A

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

**Absolute Maximum Ratings <sup>(1)</sup>**

|                                          |                           |

|------------------------------------------|---------------------------|

| ESD Tolerance <sup>(2)</sup>             | 2 kV                      |

| Differential Input Voltage               | $V^+ +0.3V$ , $V^- -0.3V$ |

| Voltage at Input                         | $V^+ +0.3V$ , $V^- -0.3V$ |

| Voltage at Output Pin                    | 15V                       |

| Supply Voltage ( $V^+ - V^-$ )           | 16V                       |

| Current at Input Pin <sup>(3)</sup>      | $\pm 5$ mA                |

| Current at Output Pin <sup>(4) (5)</sup> | $\pm 30$ mA               |

| Current at Power Supply Pin              | 40 mA                     |

| Lead Temperature (soldering, 10 sec.)    | 260°C                     |

| Junction Temperature <sup>(6)</sup>      | 150°C                     |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

- (3) All limits are specified by testing or statistical analysis.

- (4) Applies to both single-supply and split-supply operation. Continuous short circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of 150°C. Output currents in excess of  $\pm 30$  mA may adversely affect reliability.

- (5) Limiting input pin current is only necessary for input voltages which exceed the absolute maximum input voltage rating.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

**Operating Ratings <sup>(1)</sup>**

|                                                          |                                |

|----------------------------------------------------------|--------------------------------|

| Supply Voltage                                           | 2.7 $\leq$ $V_{CC}$ $\leq$ 15V |

| Temperature Range <sup>(2)</sup><br>LMC7221AI, LMC7221BI | -40°C to +85°C                 |

| Thermal Resistance ( $\theta_{JA}$ )<br>8-Pin SOIC       | 180°C/W                        |

| 5-Pin SOT-23                                             | 325°C/W                        |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured. For ensured specifications and the test conditions, see the Electrical Characteristics.

- (2) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A) / \theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

**2.7V Electrical Characteristics**

Unless otherwise specified, all limits ensured for  $T_J = 25^\circ\text{C}$ ,  $V^+ = 2.7\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{CM} = V_O = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Parameter  |                                        | Test Conditions                          | Typ <sup>(1)</sup> | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units                        |

|------------|----------------------------------------|------------------------------------------|--------------------|--------------------------------|--------------------------------|------------------------------|

| $V_{OS}$   | Input Offset Voltage                   |                                          | 3                  | 5                              | 15                             | mV                           |

| $TCV_{OS}$ | Input Offset Voltage Temperature Drift |                                          | 1.0                |                                |                                | $\mu\text{V}/^\circ\text{C}$ |

|            | Input Offset Voltage Average Drift     | <sup>(3)</sup>                           | 3.3                |                                |                                | $\mu\text{V}/\text{Month}$   |

| $I_B$      | Input Current                          |                                          | 0.04               |                                |                                | pA                           |

| $I_{OS}$   | Input Offset Current                   |                                          | 0.02               |                                |                                | pA                           |

| CMRR       | Common Mode Rejection Ratio            | $0\text{V} \leq V_{CM} \leq 2.7\text{V}$ | 75                 |                                |                                | dB                           |

| PSRR       | Power Supply Rejection Ratio           | $2.7\text{V} \leq V^+ \leq 15\text{V}$   | 80                 |                                |                                | dB                           |

- (1) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (2) All limits are specified by testing or statistical analysis.

- (3)  $C_L$  includes the probe and test jig capacitance.

## 2.7V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for  $T_J = 25^\circ\text{C}$ ,  $V^+ = 2.7\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{\text{CM}} = V_{\text{O}} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Parameter       |                                 | Test Conditions                   | Typ <sup>(1)</sup> | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units         |

|-----------------|---------------------------------|-----------------------------------|--------------------|--------------------------------|--------------------------------|---------------|

| $A_V$           | Voltage Gain                    |                                   | 100                |                                |                                | dB            |

| CMVR            | Input Common-Mode Voltage Range | CMRR > 55 dB                      | 3.0                | 2.9                            | 2.9                            | V             |

|                 |                                 |                                   |                    | <b>2.7</b>                     | <b>2.7</b>                     | min           |

|                 |                                 | CMRR > 55 dB                      | -0.3               | -0.2                           | -0.2                           | V             |

|                 |                                 |                                   |                    | <b>0.0</b>                     | <b>0.0</b>                     | max           |

| $V_{\text{OL}}$ | Output Voltage Low              | $I_{\text{LOAD}} = 2.5\text{ mA}$ | 0.2                | 0.3                            | 0.3                            | V             |

|                 |                                 |                                   |                    | <b>0.4</b>                     | <b>0.4</b>                     | max           |

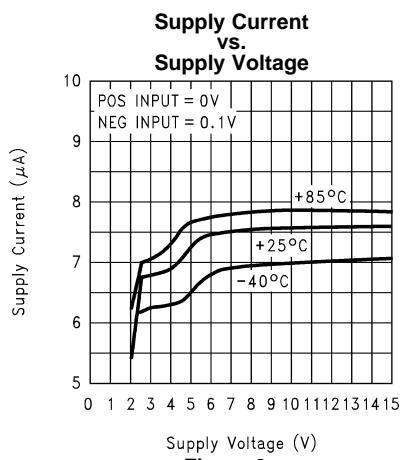

| $I_S$           | Supply Current                  | $V_{\text{OUT}} = \text{Low}$     | 7                  | 12                             | 12                             | $\mu\text{A}$ |

|                 |                                 |                                   |                    | <b>14</b>                      | <b>14</b>                      | max           |

## 5.0V and 15.0V Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_J = 25^\circ\text{C}$ ,  $V^+ = 5.0\text{V}$  and 15V,  $V^- = 0\text{V}$ ,  $V_{\text{CM}} = V_{\text{O}} = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Parameter          |                                        | Test Conditions                                       | Typ <sup>(1)</sup> | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units                        |

|--------------------|----------------------------------------|-------------------------------------------------------|--------------------|--------------------------------|--------------------------------|------------------------------|

| $V_{\text{os}}$    | Input Offset Voltage                   |                                                       | 3                  | 5                              | 15                             | mV                           |

| TC $V_{\text{os}}$ | Input Offset Voltage Temperature Drift | $V^+ = 5\text{V}$                                     | 1.0                |                                |                                | $\mu\text{V}/^\circ\text{C}$ |

|                    |                                        | $V^+ = 15\text{V}$                                    | 4.0                |                                |                                |                              |

|                    | Input Offset Voltage Average Drift     | $V^+ = 5\text{V}$ <sup>(3)</sup>                      | 3.3                |                                |                                | $\mu\text{V}/\text{Month}$   |

|                    |                                        | $V^+ = 15\text{V}$ <sup>(3)</sup>                     | 4.0                |                                |                                |                              |

| $I_B$              | Input Current                          |                                                       | 0.04               |                                |                                | pA                           |

| $I_{\text{os}}$    | Input Offset Current                   |                                                       | 0.02               |                                |                                | pA                           |

| CMRR               | Common Mode Rejection Ration           | $V^+ = 5.0\text{V}$                                   | 75                 |                                |                                | dB                           |

|                    |                                        | $V^+ = 15.0\text{V}$                                  | 82                 |                                |                                | dB                           |

| PSRR               | Power Supply Rejection Ratio           | $5\text{V} \leq V^+ \leq 10\text{V}$                  | 80                 |                                |                                | dB                           |

| $A_V$              | Voltage Gain                           |                                                       | 100                |                                |                                | dB                           |

| CMVR               | Input Common-Mode Voltage Range        | $V^+ = 5.0\text{V}$<br>CMRR > 55 dB                   | 5.3                | 5.2                            | 5.2                            | V                            |

|                    |                                        |                                                       |                    | <b>5.0</b>                     | <b>5.0</b>                     | min                          |

|                    |                                        | $V^+ = 5.0\text{V}$<br>CMRR > 55 dB                   | -0.3               | -0.2                           | -0.2                           | V                            |

|                    |                                        |                                                       |                    | <b>0.0</b>                     | <b>0.0</b>                     | max                          |

|                    |                                        | $V^+ = 15.0\text{V}$<br>CMRR > 55 dB                  | 15.3               | 15.2                           | 15.2                           | V                            |

|                    |                                        |                                                       |                    | <b>15.0</b>                    | <b>15.0</b>                    | min                          |

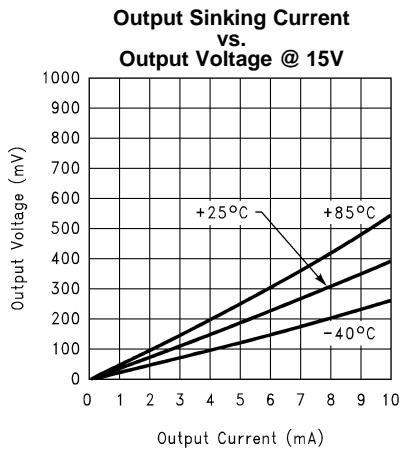

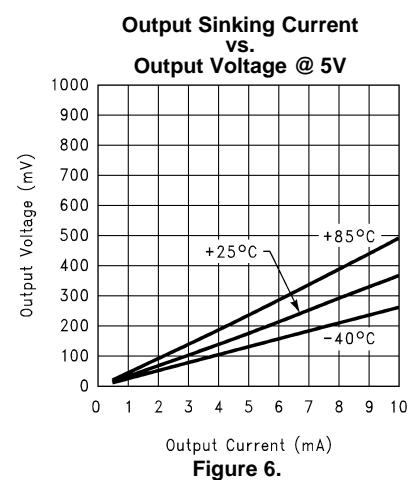

| $V_{\text{OL}}$    | Output Voltage Low                     | $V^+ = 5\text{V}$<br>$I_{\text{LOAD}} = 5\text{ mA}$  | 0.2                | 0.40                           | 0.40                           | mV                           |

|                    |                                        |                                                       |                    | <b>0.55</b>                    | <b>0.55</b>                    | max                          |

|                    |                                        | $V^+ = 15\text{V}$<br>$I_{\text{LOAD}} = 5\text{ mA}$ | 0.2                | 0.40                           | 0.40                           | mV                           |

|                    |                                        |                                                       |                    | <b>0.55</b>                    | <b>0.55</b>                    | max                          |

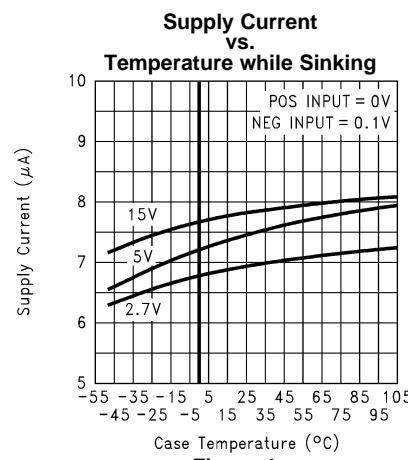

| $I_S$              | Supply Current                         | $V_{\text{OUT}} = \text{Low}$                         | 7                  | 14                             | 14                             | $\mu\text{A}$                |

|                    |                                        |                                                       |                    | <b>18</b>                      | <b>18</b>                      | max                          |

- (1) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

- (2) All limits are specified by testing or statistical analysis.

- (3)  $C_L$  includes the probe and test jig capacitance.

## 5.0V and 15.0V Electrical Characteristics (continued)

Unless otherwise specified, all limits ensured for  $T_J = 25^\circ\text{C}$ ,  $V^+ = 5.0\text{V}$  and  $15\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{CM} = V_O = V^+/2$ . **Boldface** limits apply at the temperature extremes.

| Parameter | Test Conditions       | Typ <sup>(1)</sup>     | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units |

|-----------|-----------------------|------------------------|--------------------------------|--------------------------------|-------|

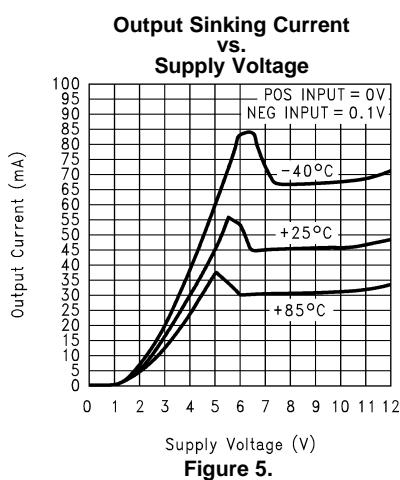

| $I_{SC}$  | Short Circuit Current | Sinking <sup>(4)</sup> | 45                             |                                | mA    |

(4) Limiting input pin current is only necessary for input voltages which exceed the absolute maximum input voltage rating.

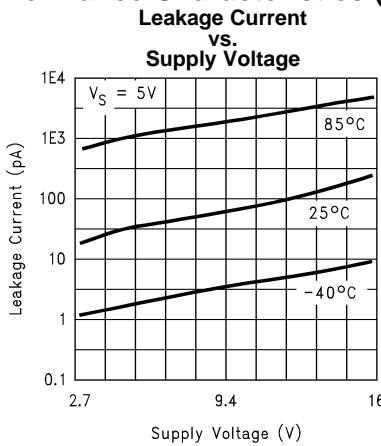

## Leakage Characteristics

$T_J = 25^\circ\text{C}$

| Parameter     | Test Conditions                                                                                                                 | Typ <sup>(1)</sup> | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units |

|---------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------|--------------------------------|-------|

| $I_{LEAKAGE}$ | Output Leakage Current<br>$V^+ = 2.7\text{V}$<br>$V_{IN(+)} = 0.5\text{V}$<br>$V_{IN(-)} = 0\text{V}$<br>$V_{OUT} = 15\text{V}$ | 0.1                | 500                            | 500                            | nA    |

(1) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(2) All limits are specified by testing or statistical analysis.

## AC Electrical Characteristics

Unless otherwise specified, all limits ensured for  $T_J = 25^\circ\text{C}$ ,  $V^+ = 5\text{V}$ ,  $V^- = 0\text{V}$ ,  $V_{CM} = V_O = V^+/2$ . **Boldface** limits apply at the temperature extreme.

| Parameter  | Test Conditions                                                                                                                    | Typ <sup>(1)</sup>                                                                       | LMC7221AI Limit <sup>(2)</sup> | LMC7221BI Limit <sup>(2)</sup> | Units         |

|------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------|--------------------------------|---------------|

| $t_{rise}$ | Rise Time<br>$f = 10\text{ kHz}$ , $C_L = 50\text{ pF}$ , <sup>(3)</sup><br>Overdrive = $10\text{ mV}$ , $5\text{ k}\Omega$ Pullup | 0.3                                                                                      |                                |                                | $\mu\text{s}$ |

| $t_{fall}$ | Fall Time<br>$f = 10\text{ kHz}$ , $C_L = 50\text{ pF}$ , <sup>(3)</sup><br>Overdrive = $10\text{ mV}$ , $5\text{ k}\Omega$ Pullup | 0.3                                                                                      |                                |                                | $\mu\text{s}$ |

| $t_{PHL}$  | Propagation Delay<br>(High to Low) <sup>(4)</sup>                                                                                  | $f = 10\text{ kHz}$ , $C_L = 50\text{ pF}$ ,<br>$5\text{ k}\Omega$ Pullup <sup>(3)</sup> | 10 mV                          | 10                             | $\mu\text{s}$ |

|            |                                                                                                                                    |                                                                                          | 100 mV                         | 4                              |               |

|            | $V^+ = 2.7\text{V}$ , $f = 10\text{ kHz}$ ,<br>$C_L = 50\text{ pF}$ , $5\text{ k}\Omega$ Pullup <sup>(3)</sup>                     | 10 mV                                                                                    | 10                             | $\mu\text{s}$                  |               |

|            |                                                                                                                                    |                                                                                          | 100 mV                         | 4                              |               |

| $t_{PLH}$  | Propagation Delay<br>(Low to High) <sup>(4)</sup>                                                                                  | $f = 10\text{ kHz}$ , $C_L = 50\text{ pF}$ ,<br>$5\text{ k}\Omega$ Pullup <sup>(3)</sup> | 10 mV                          | 6                              | $\mu\text{s}$ |

|            |                                                                                                                                    |                                                                                          | 100 mV                         | 4                              |               |

|            | $V^+ = 2.7\text{V}$ , $f = 10\text{ kHz}$ ,<br>$C_L = 50\text{ pF}$ , $5\text{ k}\Omega$ Pullup <sup>(3)</sup>                     | 10 mV                                                                                    | 7                              | $\mu\text{s}$                  |               |

|            |                                                                                                                                    |                                                                                          | 100 mV                         | 4                              |               |

(1) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

(2) All limits are specified by testing or statistical analysis.

(3) Do not short circuit the output to  $V^+$  when  $V^+$  is greater than  $12\text{V}$  or reliability will be adversely affected.

(4) Input offset voltage average drift is calculated by dividing the accelerated operating life  $V_{OS}$  drift by the equivalent operational time. This represents worst case input conditions and includes the first 30 days of drift.

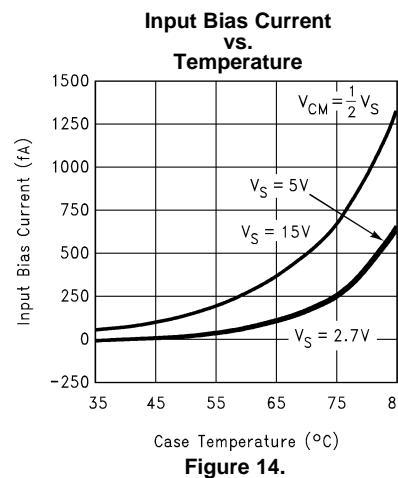

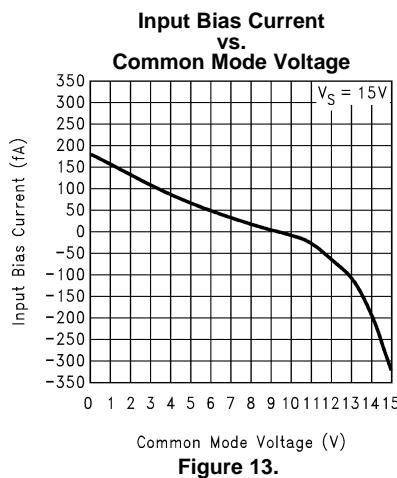

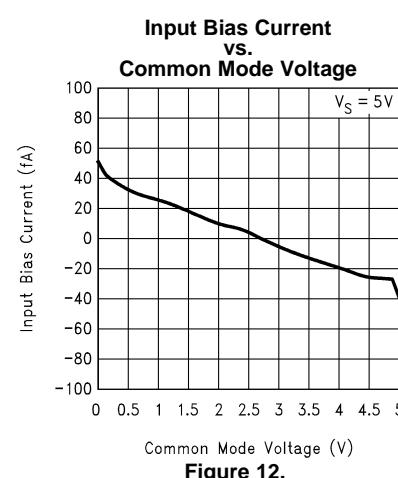

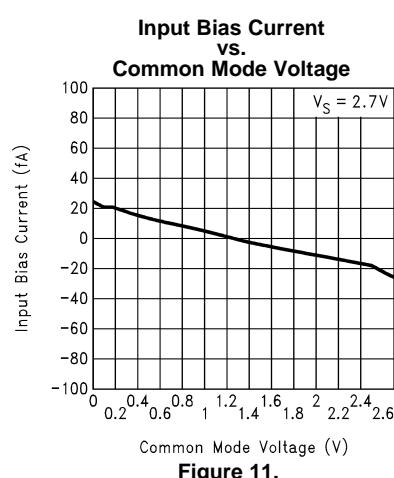

### Typical Performance Characteristics

**Typical Performance Characteristics (continued)****Figure 15.****APPLICATION INFORMATION****BENEFITS OF THE LMC7221 TINY COMPARATOR****Size**

The small footprint of the 5-Pin SOT-23 packaged Tiny Comparator, (0.120 x 0.118 inches, 3.05 x 3.00 mm) saves space on printed circuit boards, and enable the design of smaller electronic products. Because they are easier to carry, many customers prefer smaller and lighter products.

**Height**

The height (0.056 inches, 1.43 mm) of the Tiny Comparator makes it possible to use it in PCMCIA type III cards.

**Simplified Board Layout**

The Tiny Comparator can simplify board layout in several ways. First, by placing a comparator where comparators are needed, instead of routing signals to a dual or quad device, long pc traces may be avoided.

By using multiple Tiny Comparators instead of duals or quads, complex signal routing and possibly crosstalk can be reduced.

**Low Supply Current**

The typical 7  $\mu$ A supply current of the LMC7221 extends battery life in portable applications, and may allow the reduction of the size of batteries in some applications.

**Wide Voltage Range**

The LMC7221 is characterized at 15V, 5V and 2.7V. Performance data is provided at these popular voltages. This wide voltage range makes the LMC7221 a good choice for devices where the voltage may vary over the life of the batteries.

**Digital Outputs Representing Signal Level**

Comparators provide a high or low digital output depending on the voltage levels of the (+) and (-) inputs. This makes comparators useful for interfacing analog signals to microprocessors and other digital circuits. The LMC7221 can be thought of as a one-bit a/d converter.

**Open Drain Output**

The open drain output is like the open collector output of a logic gate. This makes the LMC7221 very useful for mixed voltage systems.

## Driving LEDs (Light Emitting Diodes)

With a 5 volt power supply, the LMC7221's output sinking current can drive small, high efficiency LEDs for indicator and test point circuits. The small size of the Tiny package makes it easy to find space to add this feature to even compact designs.

## Input range to Beyond Rail to Rail

The input common mode range of the LMC7221 is slightly larger than the actual power supply range. This wide input range means that the comparator can be used to sense signals close to the power supply rails. This wide input range can make design easier by eliminating voltage dividers, amplifiers, and other front end circuits previously used to match signals to the limited input range of earlier comparators. This is useful to power supply monitoring circuits which need to sense their own power supply, and compare it to a reference voltage which is close to the power supply voltage. The wide input range can also be useful for sensing the voltage drop across a current sense resistor for battery chargers.

## Zero Crossing Detector

Since the LMC7221's common mode input range extends below ground even when powered by a single positive supply, it can be used with large input resistors as a zero crossing detector.

## Low Input Currents and High Input Impedance

These characteristics allow the LMC7221 to be used to sense high impedance signals from sensors. They also make it possible to use the LMC7221 in timing circuits built with large value resistors. This can reduce the power dissipation of timing circuits. For very long timing circuits, using high value resistors can reduce the size and cost of large value capacitors for the same R-C time constant.

## Direct Sensor Interfacing

The wide input voltage range and high impedance of the LMC7221 may make it possible to directly interface to a sensor without the use of amplifiers or bias circuits. In circuits with sensors which can produce outputs in the tens to hundreds of millivolts, the LMC7221 can compare the sensor signal with an appropriately small reference voltage. This may be done close to ground or the positive supply rail. Direct sensor interfacing may eliminate the need for an amplifier for the sensor signal. Eliminating the amplifier can save cost, space, and design time.

## LOW VOLTAGE OPERATION

Comparators are the common devices by which analog signals interface with digital circuits. The LMC7221 has been designed to operate at supply voltages of 2.7V without sacrificing performance to meet the demands of 3V digital systems.

At supply voltages of 2.7V, the common-mode voltage range extends 200 mV (ensured) below the negative supply. This feature, in addition to the comparator being able to sense signals near the positive rail, is extremely useful in low voltage applications.

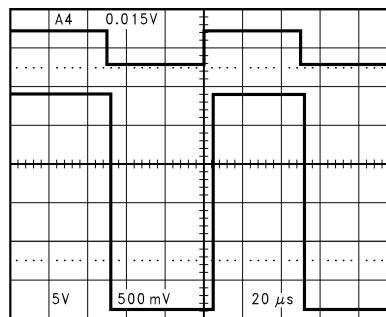

**Figure 16. Even at Low-Supply Voltage of 2.7V, an Input Signal which Exceeds the Supply Voltages Produces No Phase Inversion at the Output**

At  $V^+ = 2.7V$  propagation delays are  $t_{PLH} = 4 \mu s$  and  $t_{PHL} = 4 \mu s$  with overdrives of 100 mV.

Please refer to the performance curves for more extensive characterization.

## OPEN DRAIN OUTPUT

### Output Stage

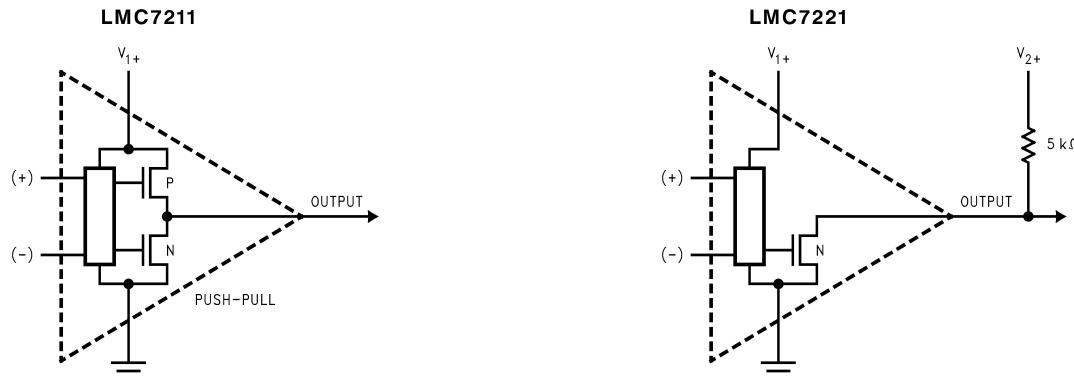

**Figure 17. Output Stage**

Figure 17 shows the difference between push-pull output and open drain output.

Push pull outputs will have a conventional high or low digital output, the same as a logic gate. Low will be the negative supply rail (usually ground) and high will be the positive supply rail.

This is useful if the chips you are interfacing to run on the same supply voltage as the comparator. An example would be an all +5V system.

Open drain outputs will only pull low—for the high output they depend on an external pull-up resistor. This can pull up to a voltage higher or lower than the comparator supply voltage. This voltage can be as high as 15V. This makes the open drain parts useful in mixed voltage systems. An example would be where the comparator runs at 5V and the logic circuits are at 3.3V. The pull-up resistor would go to the 3.3V supply.

Open drain outputs are the CMOS equivalent of open collector outputs.

### OUTPUT SHORT CIRCUIT CURRENT

The LMC7221 has short circuit protection of 40 mA. However, it is not designed to withstand continuous short circuits, transient voltage or current spikes, or shorts to any voltage beyond the supplies. A resistor in series with the output should reduce the effect of shorts. For outputs which send signals off PC boards additional protection devices, such as diodes to the supply rails, and varistors may be used.

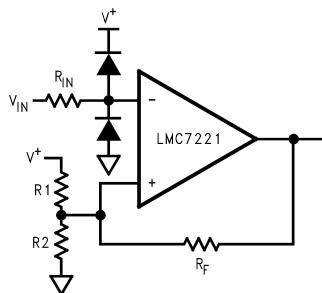

### INPUT PROTECTION

If input signals are likely to exceed the common mode range of the LMC7221, or it is likely that signals may be present when power is off, damage to the LMC7221 may occur. Large value (100 kΩ to MΩ) input resistors may reduce the likelihood of damage by limiting the input currents. Since the LMC7221 has very low input leakage currents, the effect on accuracy will be small. Additional protection may require the use of diodes, as shown in Figure 18. Note that diode leakage current may affect accuracy during normal operation.

The R-C time constant of  $R_{IN}$  and the diode capacitance may also slow response time.

Figure 18.

## LAYOUT CONSIDERATIONS

The LMC7221 is not an especially fast comparator, so high speed design practices are not required. The LMC7221 is capable of operating with very high impedance inputs, so precautions should be taken to reduce noise pickup with high impedance ( $\sim 100\text{ k}\Omega$  and greater) designs and in electrically noisy environments.

Keeping high value resistors close to the LMC7221 and minimizing the size of the input nodes is a good practice. With multilayer designs, try to avoid long loops which could act as inductors (coils). Sensors which are not close to the comparator may need twisted pair or shielded connections to reduce noise.

## PUSH-PULL OUTPUTS, DUAL VERSIONS

The LMC7211 is a comparator similar to the LMC7221, but with push-pull outputs which can source current.

The performance of the LMC7221 is available in a dual device. Please see the LMC6772 datasheet. For a dual device with push-pull outputs, please see the LMC6762 datasheet.

### Rail-to-Rail Input Low Power Comparators—

| Push-Pull Output  |                          |        |

|-------------------|--------------------------|--------|

| LMC7221           | 5-Pin SOT-23, 8-Pin SOIC | Single |

| LMC6762           | 8-Pin SOIC               | Dual   |

| Open Drain Output |                          |        |

| LMC7221           | 5-Pin SOT-23, 8-Pin SOIC | Single |

| LMC6772           | 8-Pin SOIC               | Dual   |

## ADDITIONAL 5-Pin SOT-23 TINY DEVICES

TI has additional parts available in the space saving SOT-23 Tiny package, including amplifiers, voltage references, and voltage regulators, including the following:

|         |                                                                                                                                                                        |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMC7101 | 1 MHz gain-bandwidth rail-to-rail input and output amplifier—high input impedance and high gain 700 $\mu\text{A}$ typical current 2.7V, 3V, 5V and 15V specifications. |

| LMC7111 | Low power 50 kHz gain-bandwidth rail-to-rail input and output amplifier with 25 $\mu\text{A}$ typical current specified at 2.7V, 3.0V, 3.3V, 5V and 10V.               |

| LM7131  | Tiny Video amp with 70 MHz gain bandwidth 3V, 5V and $\pm 5\text{V}$ specifications.                                                                                   |

| LP2980  | Micropower SOT 50 mA Ultra Low-Dropout Regulator.                                                                                                                      |

| LM4040  | Precision micropower shunt voltage reference. Fixed voltages of 2.500V, 4.096V, 5.000V, 8.192V and 10.000V.                                                            |

| LM4041  | Precision micropower shunt voltage reference 1.225V and adjustable.                                                                                                    |

| LM385   | Low current voltage reference. Fixed Voltages of 1.2V and 2.5V.                                                                                                        |

Contact your TI representative for the latest information.

### **SPICE MACROMODEL**

A Spice Macromodel is available for the LMC7221 comparator on the TI Amplifier Macromodel disk. Contact your TI representative to obtain the latest version.

## REVISION HISTORY

| Changes from Revision D (March 2013) to Revision E         | Page |

|------------------------------------------------------------|------|

| • Changed layout of National Data Sheet to TI format ..... | 11   |

**PACKAGING INFORMATION**

| Orderable Device  | Status<br>(1) | Package Type | Package Drawing | Pins | Package Qty | Eco Plan<br>(2)  | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples                 |

|-------------------|---------------|--------------|-----------------|------|-------------|------------------|--------------------------------------|----------------------|--------------|-------------------------|-------------------------|

| LMC7221AIM/NOPB   | ACTIVE        | SOIC         | D               | 8    | 95          | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | LMC7221AIM              | <a href="#">Samples</a> |

| LMC7221AIM5       | ACTIVE        | SOT-23       | DBV             | 5    | 1000        | Non-RoHS & Green | Call TI                              | Level-1-260C-UNLIM   | -40 to 85    | C01A                    | <a href="#">Samples</a> |

| LMC7221AIM5/NOPB  | ACTIVE        | SOT-23       | DBV             | 5    | 1000        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | C01A                    | <a href="#">Samples</a> |

| LMC7221AIM5X/NOPB | ACTIVE        | SOT-23       | DBV             | 5    | 3000        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | C01A                    | <a href="#">Samples</a> |

| LMC7221AIMX/NOPB  | ACTIVE        | SOIC         | D               | 8    | 2500        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | LMC7221AIM              | <a href="#">Samples</a> |

| LMC7221BIM        | ACTIVE        | SOIC         | D               | 8    | 95          | Non-RoHS & Green | Call TI                              | Level-1-235C-UNLIM   | -40 to 85    | LMC7221BIM              | <a href="#">Samples</a> |

| LMC7221BIM/NOPB   | ACTIVE        | SOIC         | D               | 8    | 95          | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | LMC7221BIM              | <a href="#">Samples</a> |

| LMC7221BIM5       | ACTIVE        | SOT-23       | DBV             | 5    | 1000        | Non-RoHS & Green | Call TI                              | Level-1-260C-UNLIM   | -40 to 85    | C01B                    | <a href="#">Samples</a> |

| LMC7221BIM5/NOPB  | ACTIVE        | SOT-23       | DBV             | 5    | 1000        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | C01B                    | <a href="#">Samples</a> |

| LMC7221BIM5X/NOPB | ACTIVE        | SOT-23       | DBV             | 5    | 3000        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | C01B                    | <a href="#">Samples</a> |

| LMC7221BIMX       | ACTIVE        | SOIC         | D               | 8    | 2500        | Non-RoHS & Green | Call TI                              | Level-1-235C-UNLIM   | -40 to 85    | LMC7221BIM              | <a href="#">Samples</a> |

| LMC7221BIMX/NOPB  | ACTIVE        | SOIC         | D               | 8    | 2500        | RoHS & Green     | SN                                   | Level-1-260C-UNLIM   | -40 to 85    | LMC7221BIM              | <a href="#">Samples</a> |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBsolete:** TI has discontinued the production of the device.

(2) **RoHS:** TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

**Green:** TI defines "Green" to mean the content of Chlorine (Cl) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

(6) Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

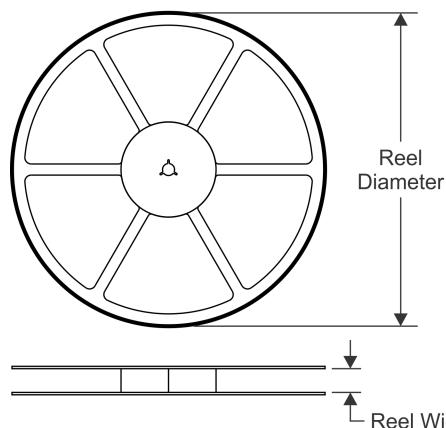

**TAPE AND REEL INFORMATION**

**REEL DIMENSIONS**

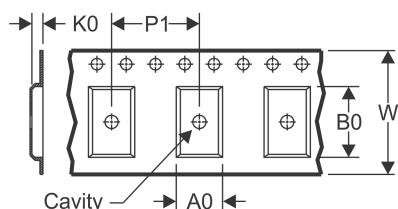

**TAPE DIMENSIONS**

|    |                                                           |

|----|-----------------------------------------------------------|

| A0 | Dimension designed to accommodate the component width     |

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

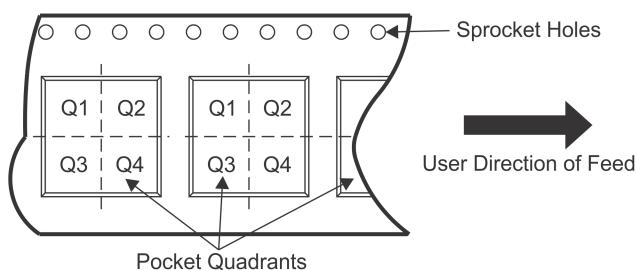

**QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE**

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Reel Diameter (mm) | Reel Width W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin1 Quadrant |

|-------------------|--------------|-----------------|------|------|--------------------|--------------------|---------|---------|---------|---------|--------|---------------|

| LMC7221AIM5       | SOT-23       | DBV             | 5    | 1000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221AIM5/NOPB  | SOT-23       | DBV             | 5    | 1000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221AIM5X/NOPB | SOT-23       | DBV             | 5    | 3000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221AIMX/NOPB  | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LMC7221BIM5       | SOT-23       | DBV             | 5    | 1000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221BIM5/NOPB  | SOT-23       | DBV             | 5    | 1000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221BIM5X/NOPB | SOT-23       | DBV             | 5    | 3000 | 178.0              | 8.4                | 3.2     | 3.2     | 1.4     | 4.0     | 8.0    | Q3            |

| LMC7221BIMX       | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

| LMC7221BIMX/NOPB  | SOIC         | D               | 8    | 2500 | 330.0              | 12.4               | 6.5     | 5.4     | 2.0     | 8.0     | 12.0   | Q1            |

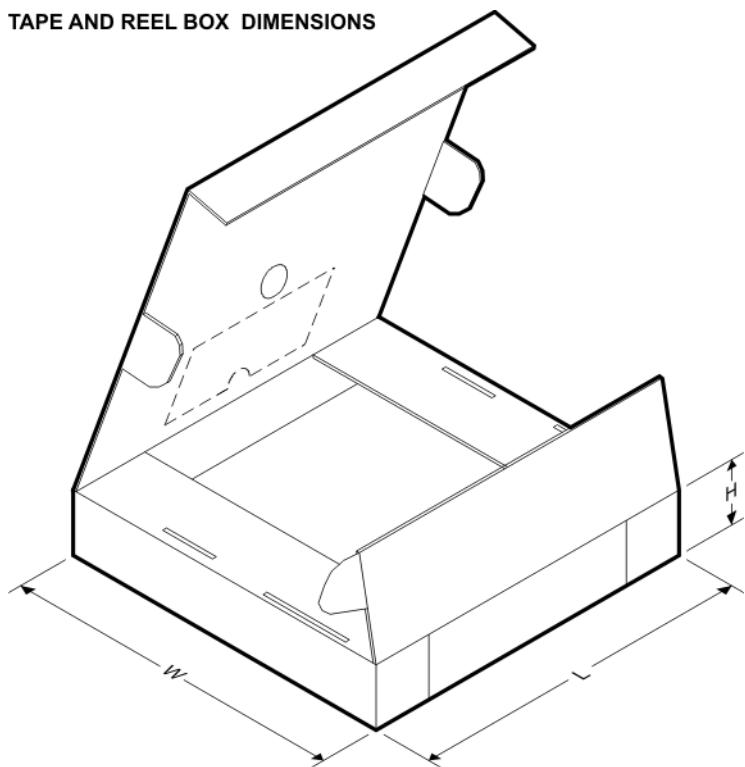

**TAPE AND REEL BOX DIMENSIONS**

\*All dimensions are nominal

| Device            | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| LMC7221AIM5       | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMC7221AIM5/NOPB  | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMC7221AIM5X/NOPB | SOT-23       | DBV             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LMC7221AIMX/NOPB  | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LMC7221BIM5       | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMC7221BIM5/NOPB  | SOT-23       | DBV             | 5    | 1000 | 208.0       | 191.0      | 35.0        |

| LMC7221BIM5X/NOPB | SOT-23       | DBV             | 5    | 3000 | 208.0       | 191.0      | 35.0        |

| LMC7221BIMX       | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| LMC7221BIMX/NOPB  | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

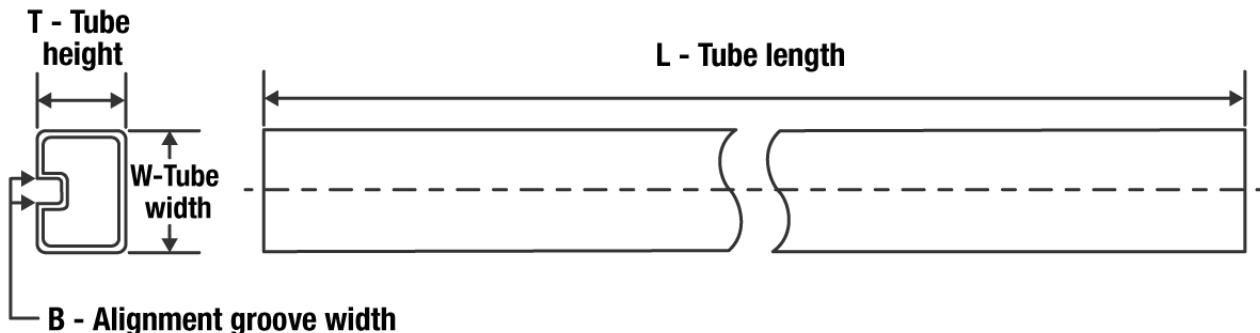

**TUBE**

\*All dimensions are nominal

| Device          | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (μm) | B (mm) |

|-----------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| LMC7221AIM/NOPB | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LMC7221BIM      | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LMC7221BIM      | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

| LMC7221BIM/NOPB | D            | SOIC         | 8    | 95  | 495    | 8      | 4064   | 3.05   |

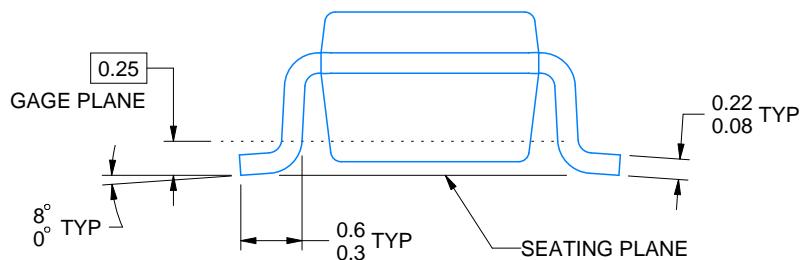

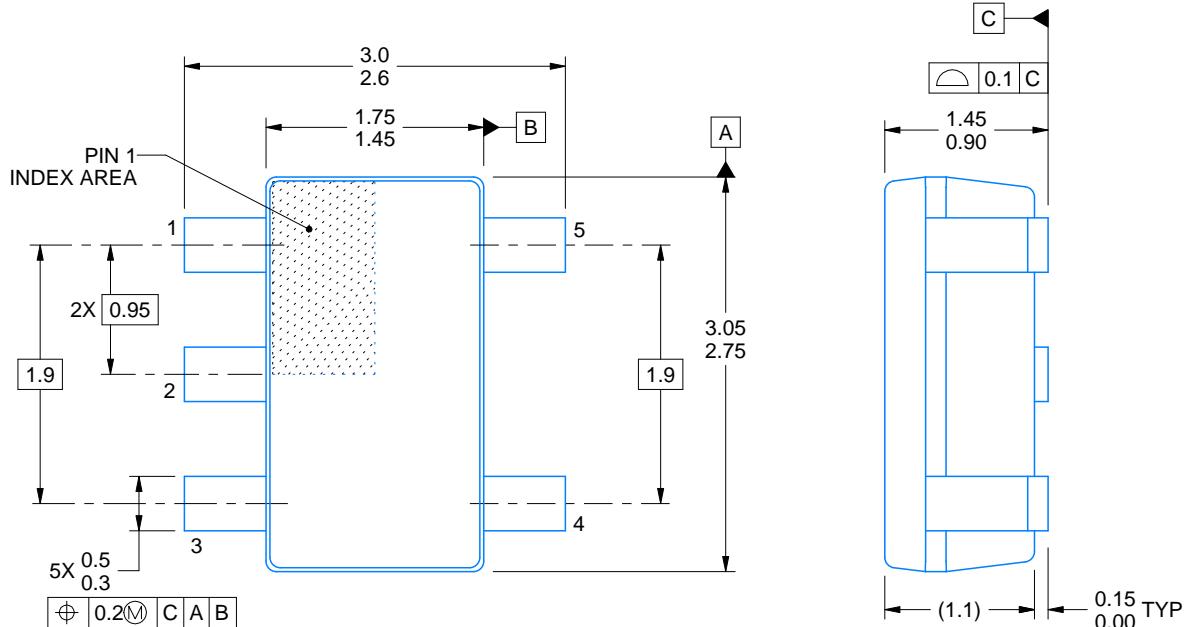

## PACKAGE OUTLINE

DBV0005A

## **SOT-23 - 1.45 mm max height**

## SMALL OUTLINE TRANSISTOR

4214839/F 06/2021

## NOTES:

1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. Reference JEDEC MO-178.

4. Body dimensions do not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.25 mm per side.

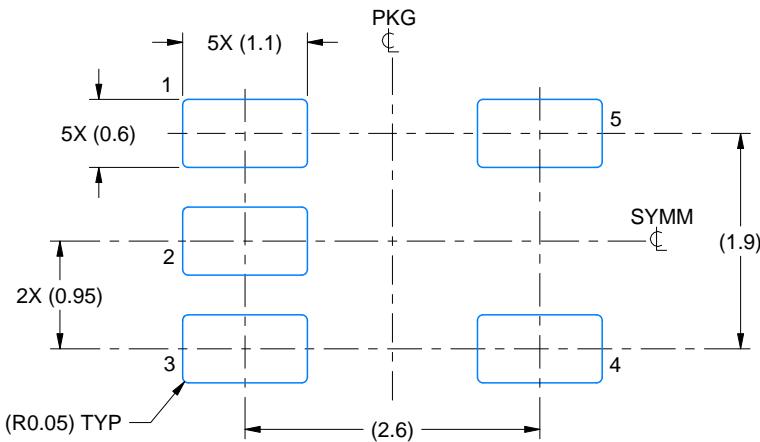

# EXAMPLE BOARD LAYOUT

DBV0005A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:15X

SOLDER MASK DETAILS

4214839/F 06/2021

NOTES: (continued)

5. Publication IPC-7351 may have alternate designs.

6. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

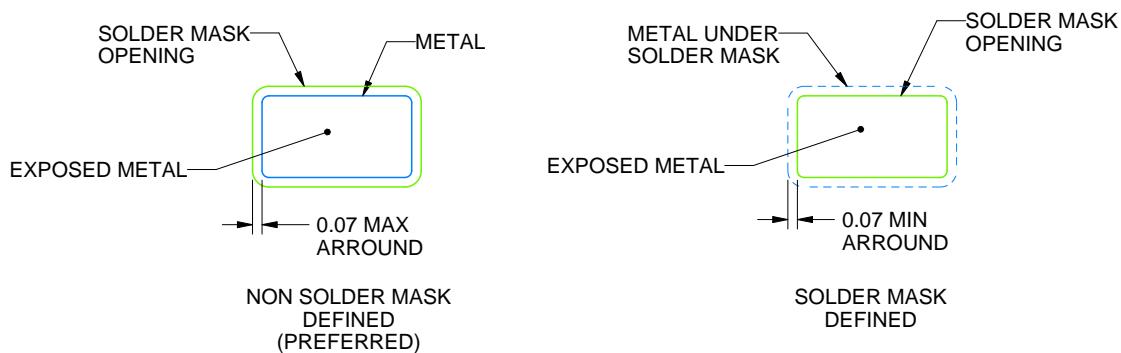

# EXAMPLE STENCIL DESIGN

DBV0005A

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

SOLDER PASTE EXAMPLE

BASED ON 0.125 mm THICK STENCIL

SCALE:15X

4214839/F 06/2021

NOTES: (continued)

7. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

8. Board assembly site may have different recommendations for stencil design.

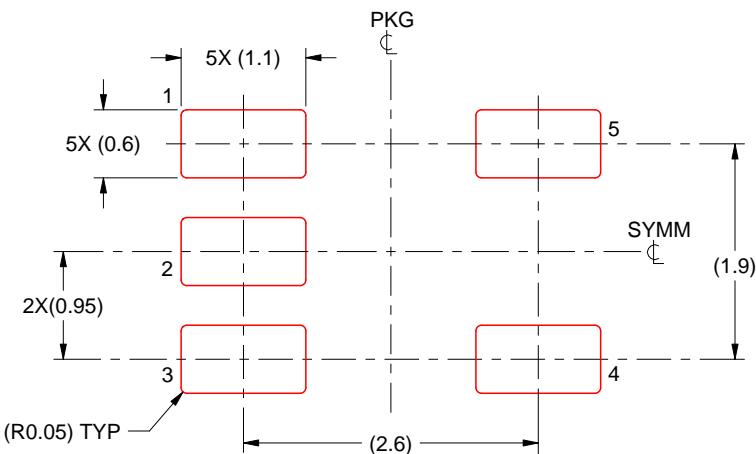

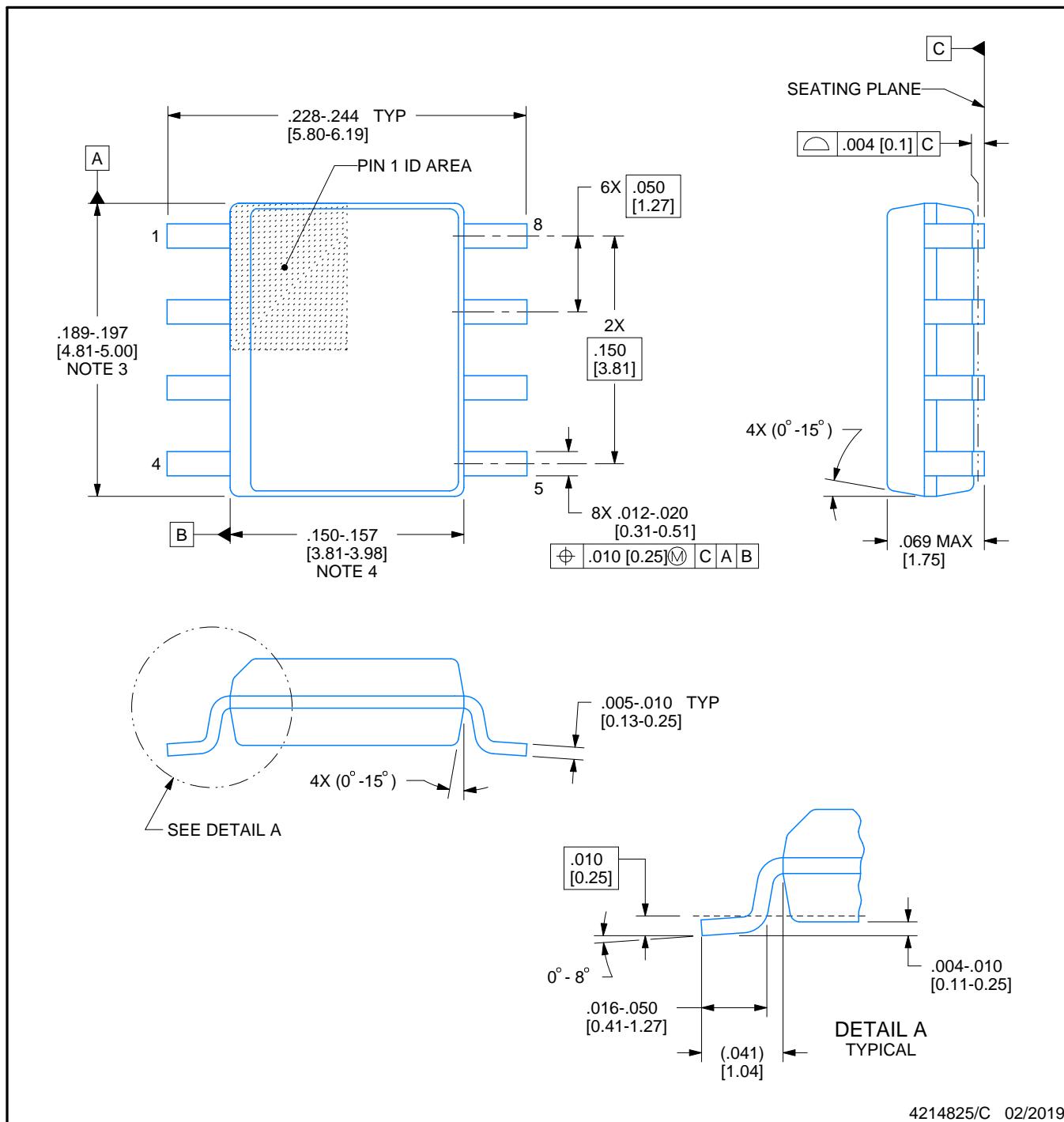

# PACKAGE OUTLINE

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

## NOTES:

1. Linear dimensions are in inches [millimeters]. Dimensions in parenthesis are for reference only. Controlling dimensions are in inches. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed .006 [0.15] per side.

4. This dimension does not include interlead flash.

5. Reference JEDEC registration MS-012, variation AA.

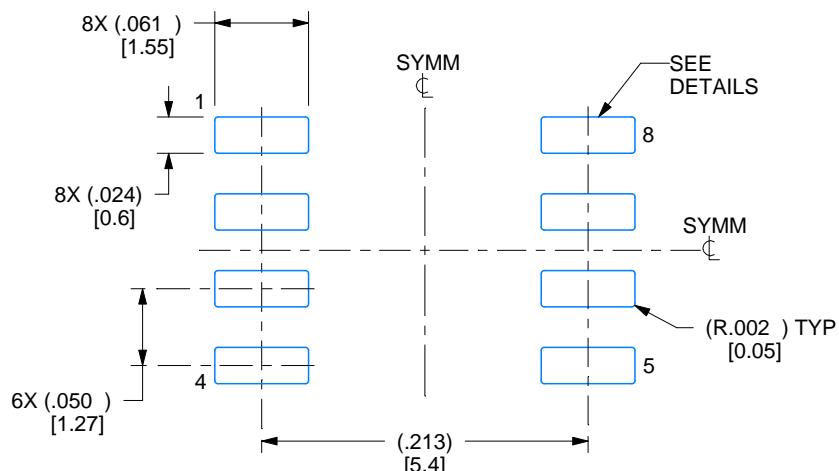

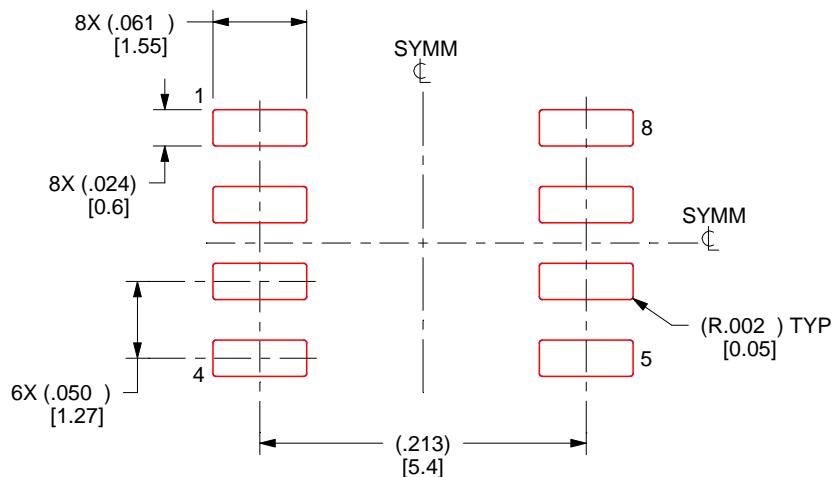

# EXAMPLE BOARD LAYOUT

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

LAND PATTERN EXAMPLE

EXPOSED METAL SHOWN

SCALE:8X

SOLDER MASK DETAILS

4214825/C 02/2019

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

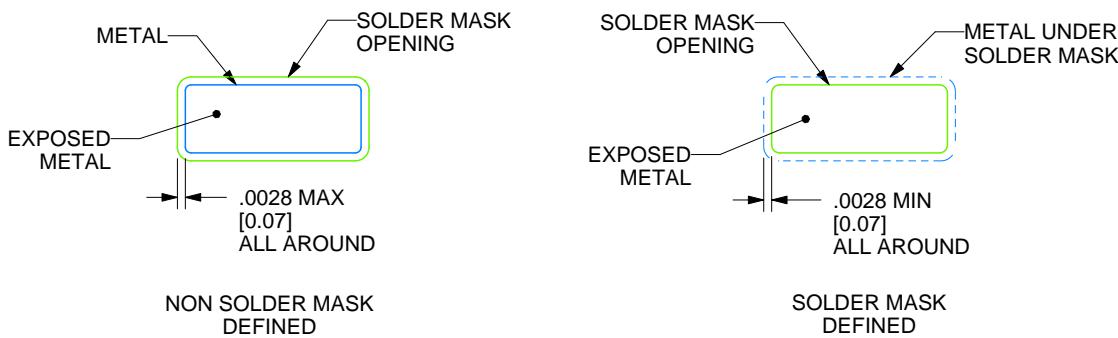

# EXAMPLE STENCIL DESIGN

D0008A

SOIC - 1.75 mm max height

SMALL OUTLINE INTEGRATED CIRCUIT

SOLDER PASTE EXAMPLE

BASED ON .005 INCH [0.125 MM] THICK STENCIL

SCALE:8X

4214825/C 02/2019

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to [TI's Terms of Sale](#) or other applicable terms available either on [ti.com](#) or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2022, Texas Instruments Incorporated