ISO1410, ISO1412, ISO1430, ISO1432 ISO1450, ISO1452

ZHCSID5E -APRIL 2018-REVISED SEPTEMBER 2019

# EMC 性能优异的 ISO14xx 5kV<sub>RMS</sub> 隔离式 RS-485/RS-422 收发器

## 1 特性

- 符合 TIA/EIA-485-A 标准

- 在 5V 总线侧电源下与 PROFIBUS 兼容

- 总线 I/O 保护

- ±30kV HBM

- ±16kV IEC 61000-4-2 接触放电

- ±4kV IEC 61000-4-4 电气快速瞬变

- 低 EMI 500kbps、12Mbps 和 50Mbps 数据速率

- 1.71V 至 5.5V 逻辑侧电源 (V<sub>CC1</sub>), 3V 至 5.5V 总 线侧电源 (V<sub>CC2</sub>)

- 失效防护接收器(总线开路、短路和空闲)

- 1/8 单位负载: 多达 256 个总线节点

- 100kV/µs(典型值)高共模瞬态抗扰度

- 扩展温度范围为 -40°C 至 +125°C

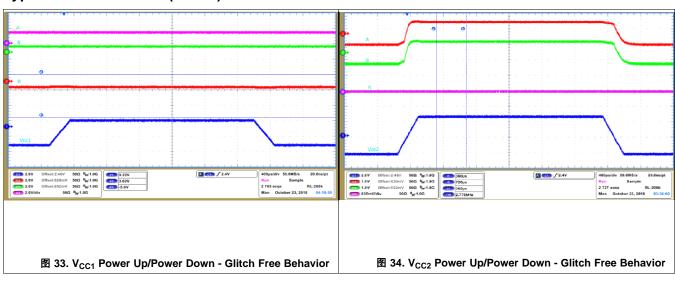

- 适用于热插拔功能的无干扰加电和断电

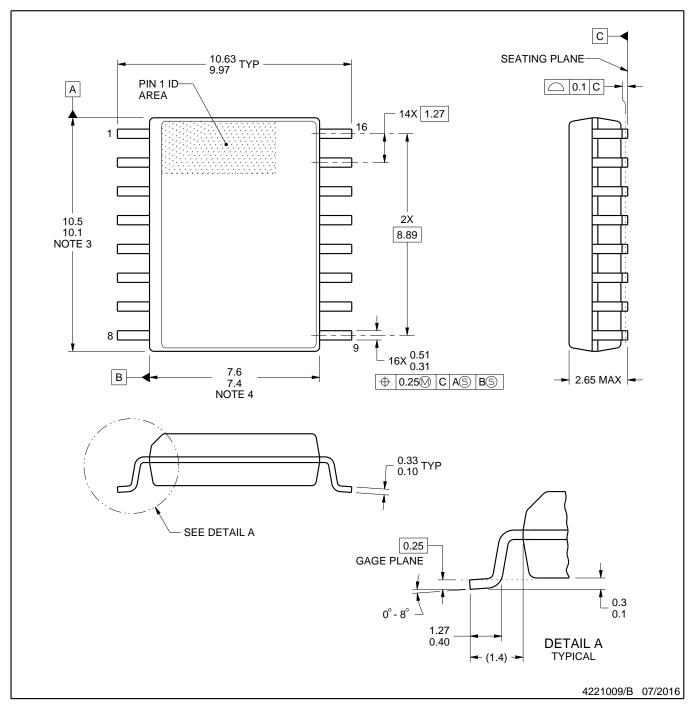

- 宽体 SOIC-16 封装

- 引脚兼容大多数隔离式 RS-485 收发器

- 安全相关认证:

- 符合 DIN VDE V 0884-11:2017-01 标准的 7071V<sub>PK</sub> V<sub>IOTM</sub> 和 1500V<sub>PK</sub> V<sub>IORM</sub> (增强型和基本型选项)

- UL 1577 标准下,长达 1 分钟的 5000V<sub>RMS</sub> 隔

- IEC 60950-1、IEC 62368-1、IEC 60601-1 和 IEC 61010-1 认证

- CQC、TUV 和 CSA 认证

- VDE(增强型)、UL、CQC 和 TUV 认证完成; VDE(基本型)和 CSA 审批正在处理中

#### 2 应用

- 电网基础设施

- 光伏逆变器

- 工厂自动化与控制

- 电机驱动器

- HVAC 系统和楼宇自动化

#### 3 说明

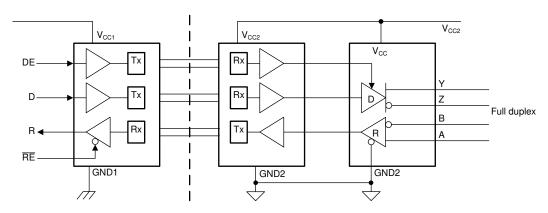

ISO14xx 器件是适用于 TIA/EIA RS-485 和 RS-422 应用的电隔离差分线路收发器。这些抗噪声收发器设计用于恶劣的工业环境。这些器件的总线引脚可承受高级别的 IEC 静电放电 (ESD) 和 IEC 电子快速瞬变 (EFT)事件,无需在总线上使用额外组件进行系统级保护。这些器件提供有基础型和增强型隔离可供选择(请参阅增强型和基础型隔离选项)。

#### 器件信息(1)

| 器件型号             | 封装        | 封装尺寸 (标称值)       |

|------------------|-----------|------------------|

| ISO1410、ISO1410B |           |                  |

| ISO1412、ISO1412B |           |                  |

| ISO1430、ISO1430B | SOIC (16) | 10.30mm x 7.50mm |

| ISO1432、ISO1432B | 3010 (16) | 10.30mm x 7.30mm |

| ISO1450、ISO1450B |           |                  |

| ISO1452、ISO1452B |           |                  |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

#### 增强型和基础型隔离选项

| 特性            | ISO14xx                                       | ISO14xxB                                      |

|---------------|-----------------------------------------------|-----------------------------------------------|

| 保护级别          | 加强版                                           | 基础版                                           |

| VDE 标准的浪涌测试电压 | 10000V <sub>PK</sub>                          | 6000V <sub>PK</sub>                           |

| UL 标准的隔离等级    | 5000V <sub>RMS</sub>                          | 5000V <sub>RMS</sub>                          |

| VDE 标准的工作电压   | 1060V <sub>RMS</sub> /<br>1500V <sub>PK</sub> | 1060V <sub>RMS</sub> /<br>1500V <sub>PK</sub> |

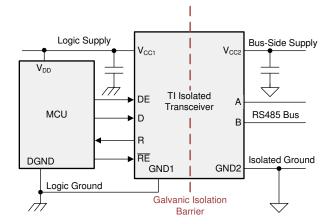

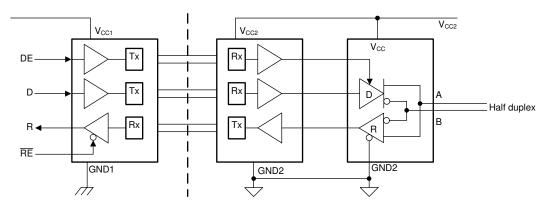

#### 简化应用电路原理图

| 1 | 特性 1                                                               |     | 8.16 Typical Characteristics      | 17 |

|---|--------------------------------------------------------------------|-----|-----------------------------------|----|

| 2 | 应用1                                                                | 9   | Parameter Measurement Information | 23 |

| 3 | 说明 1                                                               | 10  | Detailed Description              | 26 |

| 4 | 修订历史记录 2                                                           |     | 10.1 Overview                     | 26 |

| 5 | 说明(续)4                                                             |     | 10.2 Functional Block Diagram     | 26 |

| 6 | Device Options 4                                                   |     | 10.3 Feature Description          | 27 |

| 7 | Pin Configuration and Functions5                                   |     | 10.4 Device Functional Modes      | 28 |

| 8 | <del>-</del>                                                       | 11  | Application and Implementation    | 31 |

| 0 | Specifications                                                     |     | 11.1 Application Information      |    |

|   | 8.1 Absolute Maximum Ratings                                       |     | 11.2 Typical Application          | 32 |

|   | 8.2 ESD Ratings                                                    | 12  | Power Supply Recommendations      |    |

|   | 8.3 Recommended Operating Conditions                               | 13  | Layout                            |    |

|   | 8.4 Thermal Information                                            |     | 13.1 Layout Guidelines            |    |

|   | 8.5 Power Ratings                                                  |     | 13.2 Layout Example               |    |

|   | 8.6 Insulation Specifications                                      | 14  | 器件和文档支持                           |    |

|   | 8.7 Safety-Related Certifications                                  | 17  | 14.1 文档支持                         |    |

|   | 8.8 Safety Limiting Values                                         |     | 14.2 相关链接                         |    |

|   | 8.9 Electrical Characteristics: Driver                             |     | 14.3 接收文档更新通知                     |    |

|   | 8.10 Electrical Characteristics: Receiver                          |     | 14.3 接収文档史制通知                     |    |

|   | 8.11 Supply Current Characteristics: Side 1 (I <sub>CC1</sub> ) 13 |     | 14.5 商标                           |    |

|   | 8.12 Supply Current Characteristics: Side 2 (I <sub>CC2</sub> ) 14 |     |                                   |    |

|   | 8.13 Switching Characteristics: Driver                             |     | 14.6 静电放电警告                       |    |

|   | 8.14 Switching Characteristics: Receiver                           | 4.5 | 14.7 Glossary                     |    |

|   | 8.15 Insulation Characteristics Curves                             | 15  | 机械、封装和可订购信息                       | 38 |

|   |                                                                    |     |                                   |    |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| CI       | hanges from Revision D (May 2019) to Revision E                                                     | Page     |

|----------|-----------------------------------------------------------------------------------------------------|----------|

| •        | Added footnote to Pin functions table for NC pins                                                   | 5        |

| •        | Changed certification information in Safety related certifications table                            | 10       |

| •        | Changed the Vth+ spec in Electrical characteristics: Receiver for -15 ≤ VCM ≤ 15 V from -20 mV to - | 10 mV 11 |

| <u>•</u> | Added 1 line item for Vth+ in Electrical characteristics: Receiver for -7 ≤ VCM ≤ 12 V              | 11       |

| CI       | hanges from Revision C (April 2019) to Revision D                                                   | Page     |

| •        | 已添加 在整个数据表中添加了 B 器件编号                                                                               | 1        |

| CI       | hanges from Revision B (November 2018) to Revision C                                                | Page     |

| •        | 已更改 将整个数据表中引用的 ISO141x 更改为 ISO14xx                                                                  | 1        |

| •        | 已添加 在"器件信息"表中添加了 ISO1430、ISO1432、ISO1450、ISO1452                                                    | 1        |

| •        | Changed the position of Device Features tabels                                                      | 4        |

| •        | Added footnote to Pin Functions: Full-Duplex Device                                                 | 5        |

| •        | Added footnote to Pin Functions: Half-Duplex Device                                                 | 6        |

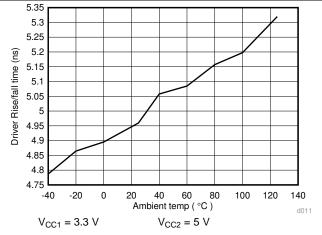

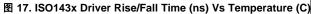

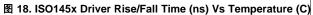

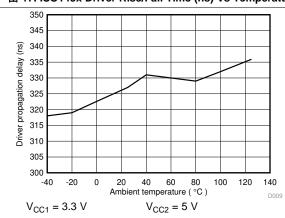

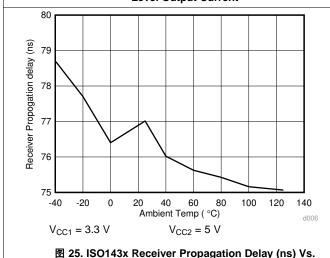

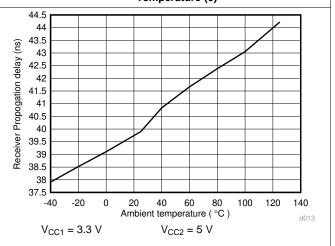

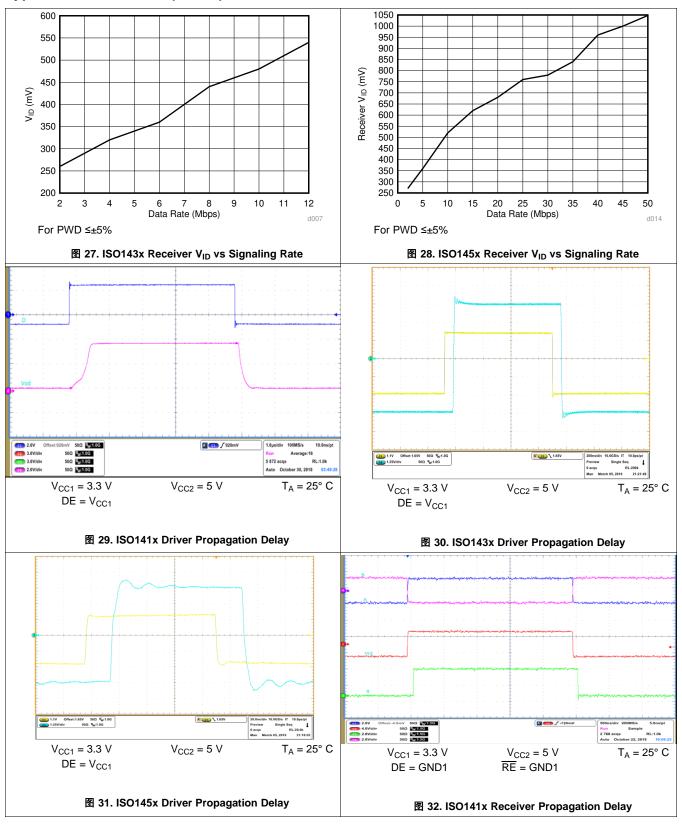

| •        | 已添加 Typical curves for ISO143x and ISO145x in <i>Typical Characteristics</i>                        | 17       |

| _        | 已添加 Section 11.2.3 Application Curves and Section 11.2.3.1 Insulation Lifetime                      | 33       |

| Cr | nanges from Revision A (August 2018) to Revision B                                                                                                                                                                                    | Page           |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| •  | 已更改 将状态更改为生产数据                                                                                                                                                                                                                        | 1              |

| Cł | nanges from Original (July 2018) to Revision A                                                                                                                                                                                        | Page           |

| •  | Changed the designator of common mode voltage in Recommended operating condition to V <sub>1</sub>                                                                                                                                    | <mark>7</mark> |

| •  | Added test condition for CMTI in Electrical characteristics: Driver                                                                                                                                                                   | 11             |

| •  | Added test condition for CMTI in Electrical characteristics: Receiver                                                                                                                                                                 | 12             |

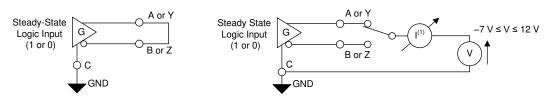

| •  | 已更改 V <sub>TEST</sub> to V <sub>CM</sub> in the <i>Common Mode Transient Immunity (CMTI)—Full Duplex</i> and <i>Common Mode Transient Immunity (CMTI)—Half Duplex</i> figures in the <i>Parameter Measurement Information</i> section | 23             |

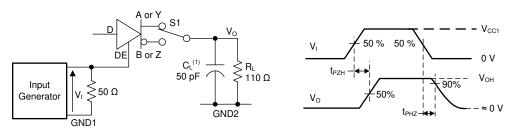

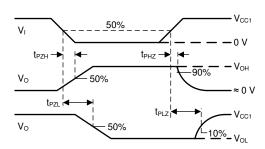

| •  | 已更改 t <sub>PLH</sub> to t <sub>PZH</sub> and t <sub>PLZ</sub> to t <sub>PHZ</sub> in the first <i>Driver Enable and Disable Times</i> timing diagram in the <i>Parameter Measurement Information</i> section                          | 24             |

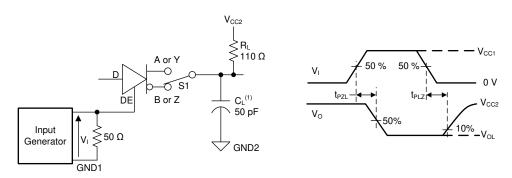

| •  | 已添加 t <sub>PHZ</sub> to the first <i>Receiver Enable and Disable Time</i> s timing diagram in the <i>Parameter Measurement Information</i> section                                                                                    | 25             |

## 5 说明 (续)

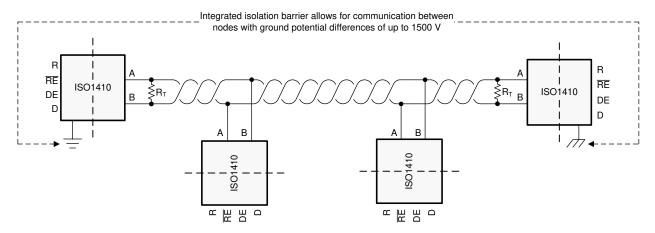

这些器件用于长距离通信。隔离会破坏通信节点之间的接地回路,从而获得更大的共模电压范围。经测试,每个器件的对称隔离栅可在总线收发器和逻辑电平接口之间按照 UL 1577 标准提供为时 1 分钟的 5000V <sub>RMS</sub> 隔离。

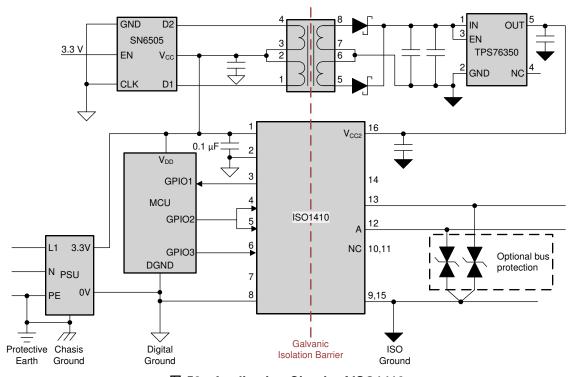

ISO14xx 器件可由 1 侧的 1.71V 至 5.5V 电压供电运行,此电压范围使器件能够与低压 FPGA 和 ASIC 连接。2 侧上具有 3V 至 5.5V 的宽电源电压范围,因此无需在隔离侧提供稳压电源。这些器件支持 -40℃ 至 +125℃ 的宽工作环境温度范围。

## 6 Device Options

Table 1 shows an overview of the options available for this family of devices.

**Table 1. Device Features**

| PART NUMBER       | ISOLATION         | DUPLEX | DATA RATE | PACKAGE   |

|-------------------|-------------------|--------|-----------|-----------|

| ISO1410, ISO1410B | Reinforced, Basic | Half   | 500 Kbps  | 16-pin DW |

| ISO1412, ISO1412B |                   | Full   | 500 Kbps  | 16-pin DW |

| ISO1430, ISO1430B |                   | Half   | 12 Mbps   | 16-pin DW |

| ISO1432, ISO1432B |                   | Full   | 12 Mbps   | 16-pin DW |

| ISO1450, ISO1450B |                   | Half   | 50 Mbps   | 16-pin DW |

| ISO1452, ISO1452B |                   | Full   | 50 Mbps   | 16-pin DW |

## 7 Pin Configuration and Functions

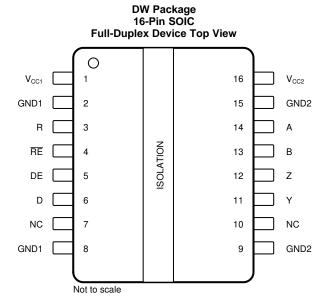

#### Pin Functions: Full-Duplex Device

| F                   | PIN |     | Turiodiono: Turi Bupiox Bovios                                                                                     |  |

|---------------------|-----|-----|--------------------------------------------------------------------------------------------------------------------|--|

| NAME                | NO. | I/O | DESCRIPTION                                                                                                        |  |

| Α                   | 14  | I   | Receiver non-inverting input on the bus side                                                                       |  |

| В                   | 13  | I   | Receiver inverting input on the bus side                                                                           |  |

| D                   | 6   | I   | Driver input                                                                                                       |  |

| DE                  | 5   | 1   | Driver enable. This pin enables the driver output when high and disables the driver output when low or open.       |  |

| GND1 <sup>(1)</sup> | 2   | _   | Ground connection for V <sub>CC1</sub>                                                                             |  |

| GND1 <sup>(1)</sup> | 8   | _   | Ground connection for V <sub>CC1</sub>                                                                             |  |

| GND2 <sup>(1)</sup> | 9   | _   | Ground connection for V <sub>CC2</sub>                                                                             |  |

| GND2 <sup>(1)</sup> | 15  | _   | Ground connection for V <sub>CC2</sub>                                                                             |  |

| NC <sup>(2)</sup>   | 7   | _   | No internal connection                                                                                             |  |

| NC <sup>(2)</sup>   | 10  | _   | No internal connection                                                                                             |  |

| R                   | 3   | 0   | Receiver output                                                                                                    |  |

| RE                  | 4   | 1   | Receiver enable. This pin disables the receiver output when high or open and enables the receiver output when low. |  |

| V <sub>CC1</sub>    | 1   | _   | Logic-side power supply                                                                                            |  |

| V <sub>CC2</sub>    | 16  | _   | Transceiver-side power supply                                                                                      |  |

| Υ                   | 11  | 0   | Driver non-inverting output                                                                                        |  |

| Z                   | 12  | 0   | Driver inverting output                                                                                            |  |

- (1) For Logic side, both Pin 2 and Pin 8 must be connected to GND1. For Bus side, both Pin 9 and Pin 15 must be connected to GND2.

- (2) Device functionality is not affected if NC pins are connected to supply or ground on PCB

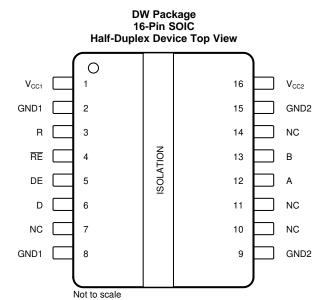

#### Pin Functions: Half-Duplex Device

|                     | Till Tulictions. Hall-Duplex Device |     |                                                                                                                    |  |  |  |

|---------------------|-------------------------------------|-----|--------------------------------------------------------------------------------------------------------------------|--|--|--|

| PIN I/O             |                                     | 1/0 | DESCRIPTION                                                                                                        |  |  |  |

| NAME                | NO.                                 | 1/0 | DESCRIPTION                                                                                                        |  |  |  |

| Α                   | 12                                  | I/O | Transceiver non-inverting input or output (I/O) on the bus side                                                    |  |  |  |

| В                   | 13                                  | I/O | Transceiver inverting input or output (I/O) on the bus side                                                        |  |  |  |

| D                   | 6                                   | I   | Driver input                                                                                                       |  |  |  |

| DE                  | 5                                   | ı   | Driver enable. This pin enables the driver output when high and disables the driver output when low or open.       |  |  |  |

| GND1 <sup>(1)</sup> | 2                                   | _   | Ground connection for V <sub>CC1</sub>                                                                             |  |  |  |

| GND1 <sup>(1)</sup> | 8                                   | _   | Ground connection for V <sub>CC1</sub>                                                                             |  |  |  |

| GND2 <sup>(1)</sup> | 9                                   | _   | Ground connection for V <sub>CC2</sub>                                                                             |  |  |  |

| GND2 <sup>(1)</sup> | 15                                  | _   | Ground connection for V <sub>CC2</sub>                                                                             |  |  |  |

| NC (2)              | 7                                   | _   | No internal connection                                                                                             |  |  |  |

| NC <sup>(2)</sup>   | 10                                  | _   | No internal connection                                                                                             |  |  |  |

| NC <sup>(2)</sup>   | 11                                  | _   | No internal connection                                                                                             |  |  |  |

| NC <sup>(2)</sup>   | 14                                  | _   | No internal connection                                                                                             |  |  |  |

| R                   | 3                                   | 0   | Receiver output                                                                                                    |  |  |  |

| RE                  | 4                                   | 1   | Receiver enable. This pin disables the receiver output when high or open and enables the receiver output when low. |  |  |  |

| V <sub>CC1</sub>    | 1                                   | _   | Logic-side power supply                                                                                            |  |  |  |

| V <sub>CC2</sub>    | 16                                  | _   | Transceiver-side power supply                                                                                      |  |  |  |

|                     |                                     |     |                                                                                                                    |  |  |  |

- (1) For Logic side, both Pin 2 and Pin 8 must be connected to GND1. For Bus side, both Pin 9 and Pin 15 must be connected to GND2.

- (2) Device functionality is not affected if NC pins are connected to supply or ground on PCB

## 8 Specifications

## 8.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)  $^{(1)(2)}$

|                  |                                             | MIN  | MAX                                  | UNIT |

|------------------|---------------------------------------------|------|--------------------------------------|------|

| V <sub>CC1</sub> | Supply voltage, side 1                      | -0.5 | 6                                    | V    |

| V <sub>CC2</sub> | Supply voltage, side 2                      | -0.5 | 6                                    | V    |

| V <sub>IO</sub>  | Logic voltage level (D, DE, RE, R)          | -0.5 | V <sub>CC1</sub> +0.5 <sup>(3)</sup> | V    |

| Io               | Output current on R pin                     | -15  | 15                                   | mA   |

| $V_{BUS}$        | Voltage on bus pins (A, B, Y, Z w.r.t GND2) | -18  | 18                                   | V    |

| $T_{J}$          | Junction temperature                        | -40  | 150                                  | °C   |

| T <sub>STG</sub> | Storage temperature                         | -65  | 150                                  | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 8.2 ESD Ratings

|                    |                                                                                               |                                                                 | VALUE  | UNIT |

|--------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--------|------|

| V <sub>(ESD)</sub> | Contact Discharge, per IEC 61000-4-2                                                          | Pins Bus terminals and GND2                                     | ±16000 | V    |

| V <sub>(ESD)</sub> | Contact Discharge, per IEC 61000-4-2                                                          | ISO141x, Pins Bus terminals and GND1 (across isolation barrier) | ±8000  | V    |

| V <sub>(ESD)</sub> | Contact Discharge, per IEC 61000-4-2                                                          | ISO143x, Pins Bus terminals and GND1 (across isolation barrier) | ±8000  | V    |

|                    | Electrostatic discharge                                                                       | All pins except bus pins <sup>(1)</sup>                         | ±6000  | V    |

| V <sub>(ESD)</sub> | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001                                            | Bus terminals to GND2 <sup>(1)</sup>                            | ±30000 |      |

|                    | Electrostatic discharge<br>Charged device model (CDM), per<br>JEDEC specification JESD22-C101 | All pins (2)                                                    | ±1500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

|                   |                                                          | MIN      | MAX      | UNIT |

|-------------------|----------------------------------------------------------|----------|----------|------|

| V                 | Supply Voltage, Side 1, 1.8-V operation                  | 1.71     | 1.89     | V    |

| V <sub>CC1</sub>  | Supply Voltage, Side 1, 2.5-V, 3.3-V and 5.5-V operation | 2.25     | 5.5      | V    |

| V <sub>CC2</sub>  | Supply Voltage, Side 2                                   | 3        | 5.5      | V    |

| VI                | Common Mode voltage at any bus terminal: A or B          | -7       | 12       | V    |

| V <sub>IH</sub>   | High-level input voltage (D, DE, RE inputs)              | 0.7*Vcc1 | Vcc1     | V    |

| V <sub>IL</sub>   | Low-level input voltage (D, DE, RE inputs)               | 0        | 0.3*Vcc1 | V    |

| V <sub>ID</sub>   | Differential input voltage, A with respect to B          | -15      | 15       | V    |

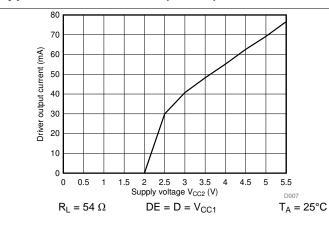

| Io                | Output current, Driver                                   | -60      | 60       | mA   |

| I <sub>OR</sub>   | Output current, Receiver                                 | -4       | 4        | mA   |

| $R_L$             | Differential load resistance                             | 54       |          | Ω    |

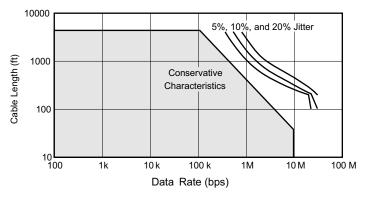

| 1/t <sub>UI</sub> | Signaling rate ISO141x                                   |          | 500      | kbps |

| 1/t <sub>UI</sub> | Signaling Rate ISO143x                                   |          | 12       | Mbps |

| 1/t <sub>UI</sub> | Signaling rate ISO145x                                   |          | 50       | Mbps |

| T <sub>A</sub>    | Operating ambient temperature                            | -40      | 125      | °C   |

<sup>(2)</sup> All voltage values except differential I/O bus voltages are with respect to the local ground terminal (GND1 or GND2) and are peak voltage values.

<sup>(3)</sup> Maximum voltage must not exceed 6 V

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 8.4 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                | ISO14xx<br>DW (SOIC) | UNIT  |

|----------------------|----------------------------------------------|----------------------|-------|

|                      | THERMAL METRIC                               | 16 PINS              | Oldin |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 67.9                 | °C/W  |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 27.7                 | °C/W  |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 29.4                 | °C/W  |

| ΨЈТ                  | Junction-to-top characterization parameter   | 12.9                 | °C/W  |

| ΨЈВ                  | Junction-to-board characterization parameter | 28.8                 | °C/W  |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | _                    | °C/W  |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 8.5 Power Ratings

|                 | PARAMETER                              | TEST CONDITIONS                                                                                                  | MIN | TYP | MAX | UNIT |

|-----------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| ISO14           | 10_ISO1412                             |                                                                                                                  |     |     |     |      |

| $P_D$           | Maximum power dissipation (both sides) | V <sub>CC1</sub> = V <sub>CC2</sub> = 5.5 V, T <sub>J</sub> = 150°C, A-B                                         |     |     | 556 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | pad = 54 Ω   50pF, Load on R=15pF                                                                                |     |     | 28  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side-2)     | Input a 250kHz 50% duty cycle square wave to D pin with V <sub>DE</sub> =V <sub>CC1,</sub> V <sub>RE</sub> =GND1 |     |     | 528 | mW   |

| ISO14           | 30_ISO1432                             |                                                                                                                  |     |     |     |      |

| $P_D$           | Maximum power dissipation (both sides) | $V_{CC1} = V_{CC2} = 5.5 \text{ V}, T_J = 150^{\circ}\text{C}, A-B$                                              |     |     | 352 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | load = 54 Ω   50pF, Load on R=15pF<br>Input a 6MHz 50% duty cycle square                                         |     |     | 33  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side-2)     | wave to D pin with  V <sub>DE</sub> =V <sub>CC1</sub> , V <sub>RE</sub> =GND1                                    |     |     | 319 | mW   |

| ISO14           | 50_ISO1452                             |                                                                                                                  | •   |     |     |      |

| $P_D$           | Maximum power dissipation (both sides) | $V_{CC1} = V_{CC2} = 5.5 \text{ V}, T_J = 150^{\circ}\text{C}, A-B$                                              |     |     | 588 | mW   |

| P <sub>D1</sub> | Maximum power dissipation (side-1)     | load = 54 Ω   50pF, Load on R=15pF<br>Input a 25MHz 50% duty cycle square                                        |     |     | 49  | mW   |

| P <sub>D2</sub> | Maximum power dissipation (side-2)     | wave to D pin with  V <sub>DE</sub> =V <sub>CC1</sub> , V <sub>RE</sub> =GND1                                    |     |     | 539 | mW   |

## 8.6 Insulation Specifications

|                   | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                                                                            | SPECIFICATIONS DW-16 | UNIT      |

|-------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|

| IEC 6066          | 64-1                                                    |                                                                                                                                                                                                                                            |                      |           |

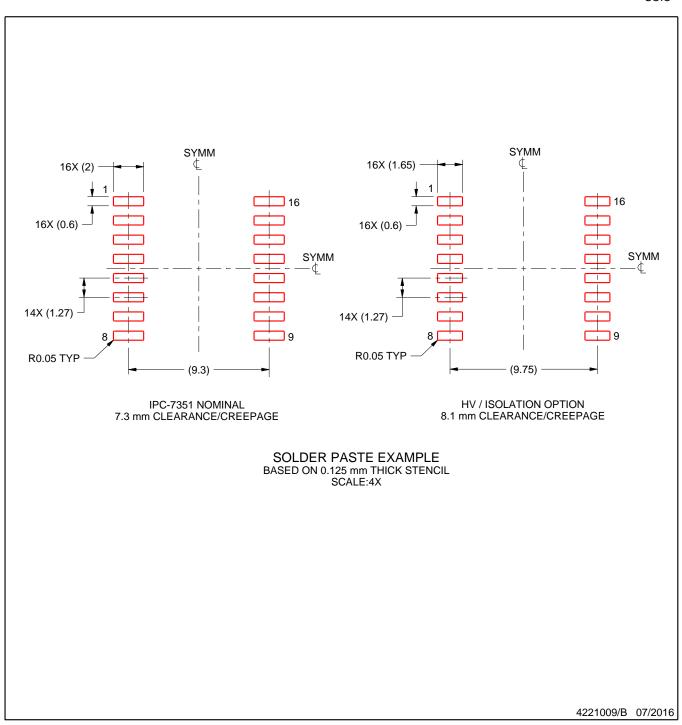

| CLR               | External clearance (1)                                  | Side 1 to side 2 distance through air                                                                                                                                                                                                      | >8                   | mm        |

| CPG               | External creepage (1)                                   | Side 1 to side 2 distance across package surface                                                                                                                                                                                           | >8                   | mm        |

| DTI               | Distance through the insulation                         | Minimum internal gap (internal clearance)                                                                                                                                                                                                  | >17                  | μm        |

| СТІ               | Comparative tracking index                              | IEC 60112; UL 746A                                                                                                                                                                                                                         | >600                 | V         |

|                   | Material Group                                          | According to IEC 60664-1                                                                                                                                                                                                                   | I                    |           |

|                   | 0 11 1                                                  | Rated mains voltage ≤ 600 V <sub>RMS</sub>                                                                                                                                                                                                 | I-IV                 |           |

|                   | Overvoltage category                                    | Rated mains voltage ≤ 1000 V <sub>RMS</sub>                                                                                                                                                                                                | 1-111                |           |

| DIN VDE           | V 0884-11:2017-01 <sup>(2)</sup>                        |                                                                                                                                                                                                                                            | 1                    |           |

| V <sub>IORM</sub> | Maximum repetitive peak isolation voltage               | AC voltage (bipolar)                                                                                                                                                                                                                       | 1500                 | $V_{PK}$  |

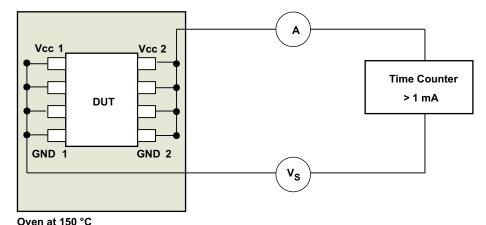

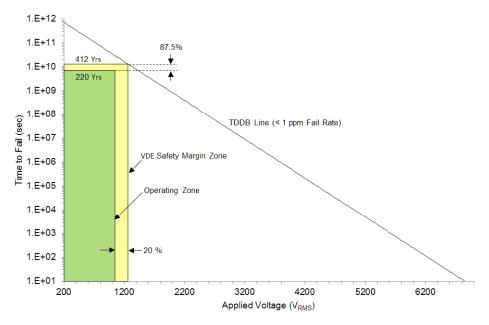

| $V_{IOWM}$        | Maximum working isolation voltage                       | AC voltage (sine wave); time-dependent dielectric breakdown (TDDB) test; see 图 56                                                                                                                                                          | 1060                 | $V_{RMS}$ |

|                   |                                                         | DC voltage                                                                                                                                                                                                                                 | 1500                 | $V_{DC}$  |

| V <sub>IOTM</sub> | Maximum transient isolation voltage                     | $V_{TEST} = V_{IOTM}$ , $t = 60$ s (qualification); $V_{TEST} = 1.2 \times V_{IOTM}$ , $t = 1$ s (100% production)                                                                                                                         | 7071                 | $V_{PK}$  |

| V                 | Maximum surge isolation voltage ISO141x <sup>(3)</sup>  | Test method per IEC 62368-1, 1.2/50 $\mu$ s waveform, V <sub>TEST</sub> = 1.6 $\times$ V <sub>IOSM</sub> = 10000 V <sub>PK</sub> (qualification)                                                                                           | 6250                 | $V_{PK}$  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage ISO141xB <sup>(3)</sup> | Test method per IEC 62368-1, 1.2/50 $\mu$ s waveform, V <sub>TEST</sub> = 1.3 $\times$ V <sub>IOSM</sub> = 6000 V <sub>PK</sub> (qualification)                                                                                            | 4615                 | $V_{PK}$  |

|                   |                                                         | Method a: After I/O safety test subgroup 2/3, $V_{ini}$ = $V_{IOTM}$ , $t_{ini}$ = 60 s; $V_{pd(m)}$ = 1.2 x $V_{IORM}$ , $t_m$ = 10 s                                                                                                     | ≤ 5                  |           |

| q <sub>pd</sub>   | Apparent charge <sup>(4)</sup>                          | Method a: After environmental tests subgroup 1, $V_{ini} = V_{IOTM}$ , $t_{ini} = 60$ s; ISO14xx: $V_{pd(m)} = 1.6 \times V_{IORM}$ , $t_m = 10$ s ISO14xxB: $V_{pd(m)} = 1.2 \times V_{IORM}$ , $t_m = 10$ s                              | ≤ 5                  | рС        |

|                   |                                                         | Method b1: At routine test (100% production) and preconditioning (type test), $V_{ini} = V_{IOTM}$ , $t_{ini} = 1$ s; ISO14xx: $V_{pd(m)} = 1.875 \times V_{IORM}$ , $t_m = 1$ s ISO14xxB: $V_{pd(m)} = 1.5 \times V_{IORM}$ , $t_m = 1$ s | ≤ 5                  |           |

| C <sub>IO</sub>   | Barrier capacitance, input to output (5)                | $V_{IO} = 0.4 \times \sin(2 \pi ft), f = 1 MHz$                                                                                                                                                                                            | 1                    | pF        |

|                   |                                                         | V <sub>IO</sub> = 500 V, T <sub>A</sub> = 25°C                                                                                                                                                                                             | > 10 <sup>12</sup>   |           |

| R <sub>IO</sub>   | Insulation resistance, input to output (5)              | V <sub>IO</sub> = 500 V, 100°C ≤ T <sub>A</sub> ≤ 150°C                                                                                                                                                                                    | > 10 <sup>11</sup>   | Ω         |

|                   |                                                         | V <sub>IO</sub> = 500 V at T <sub>S</sub> = 150°C                                                                                                                                                                                          | > 10 <sup>9</sup>    |           |

|                   | Pollution degree                                        |                                                                                                                                                                                                                                            | 2                    |           |

|                   | Climatic category                                       |                                                                                                                                                                                                                                            | 40/125/<br>21        |           |

| UL 1577           |                                                         |                                                                                                                                                                                                                                            | ·                    |           |

| V <sub>ISO</sub>  | Withstand isolation voltage                             | V <sub>TEST</sub> = V <sub>ISO</sub> , t = 60 s (qualification);<br>V <sub>TEST</sub> = 1.2 × V <sub>ISO</sub> , t = 1 s (100% production)                                                                                                 | 5000                 | $V_{RMS}$ |

<sup>(1)</sup> Creepage and clearance requirements should be applied according to the specific equipment isolation standards of an application. Care should be taken to maintain the creepage and clearance distance of a board design to ensure that the mounting pads of the isolator on the printed-circuit board do not reduce this distance. Creepage and clearance on a printed-circuit board become equal in certain cases. Techniques such as inserting grooves, ribs, or both on a printed circuit board are used to help increase these specifications.

<sup>(2)</sup> ISO14xx is suitable for safe electrical insulation and ISO14xxB is suitable for basic electrical insulation only within the safety ratings. Compliance with the safety ratings shall be ensured by means of suitable protective circuits.

<sup>(3)</sup> Testing is carried out in air or oil to determine the intrinsic surge immunity of the isolation barrier.

<sup>(4)</sup> Apparent charge is electrical discharge caused by a partial discharge (pd).

<sup>(5)</sup> All pins on each side of the barrier tied together creating a two-pin device.

#### 8.7 Safety-Related Certifications

| VDE                                                                                                                                                                                                                                                                                    | CSA                                                                                                                                                                                                                                                                                                                                                                                                         | UL                                                           | CQC                                                                                                      | TUV                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certified according to DIN VDE V 0884-11:2017- 01                                                                                                                                                                                                                                      | Plan to certify according<br>to IEC 60950-1, IEC<br>62368-1 and IEC 60601-1                                                                                                                                                                                                                                                                                                                                 | Recognized under UL<br>1577 Component<br>Recognition Program | Certified according to GB4943.1-2011                                                                     | Certified according to EN<br>61010-1:2010/A1:2019,<br>EN 60950-<br>1:2006/A2:2013 and EN<br>62368-1:2014                                                                                                                                                                                                                                                 |

| Maximum transient isolation voltage, 7071 V <sub>PK</sub> ; Maximum repetitive peak isolation voltage, 1500 V <sub>PK</sub> ; Maximum surge isolation voltage, ISO141x, ISO143x, ISO145x: 6250 V <sub>PK</sub> (Reinforced) ISO141xB, ISO143xB, ISO145xB: 4600 V <sub>PK</sub> (Basic) | CSA 60950-1-07+A1+A2 and IEC 60950-1 2nd Ed., for pollution degree 2, material group I ISO141x, ISO143x, ISO145x: 800 V <sub>RMS</sub> reinforced isolation ISO141xB, ISO143xB, ISO145xB: 800 V <sub>RMS</sub> basic isolation CSA 60601- 1:14 and IEC 60601-1 Ed. 3.1, ISO141x, ISO143x, ISO145x: 2 MOPP (Means of Patient Protection) 250 V <sub>RMS</sub> (354 V <sub>PK</sub> ) maximum working voltage | Single protection,<br>5000 V <sub>RMS</sub>                  | Reinforced insulation, Altitude ≤ 5000 m, Tropical Climate, 700 V <sub>RMS</sub> maximum working voltage | EN 61010- 1:2010 /A1:2019 ISO141x, ISO143x, ISO145x: 600 V <sub>RMS</sub> reinforced isolation ISO141xB, ISO143xB, ISO145xB: 1000 V <sub>RMS</sub> basic isolation EN 60950- 1:2006/A2:2013 and EN 62368-1:2014 ISO141x, ISO143x, ISO145x: 800 V <sub>RMS</sub> reinforced isolation ISO141xB, ISO143xB, ISO145xB: 1060 V <sub>RMS</sub> basic isolation |

| Reinforced<br>Certificate:40040142<br>Basic certificate planned                                                                                                                                                                                                                        | Certificate planned                                                                                                                                                                                                                                                                                                                                                                                         | File number: E181974                                         | Certificate number:<br>CQC15001121716                                                                    | Client ID number: 77311                                                                                                                                                                                                                                                                                                                                  |

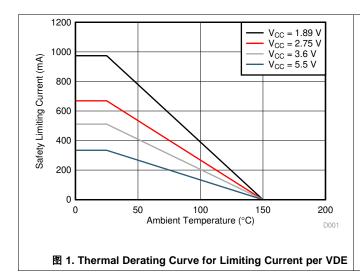

## 8.8 Safety Limiting Values

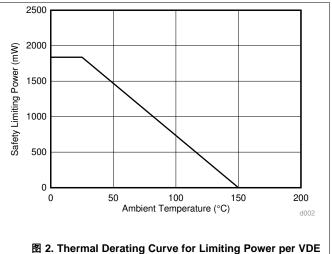

Safety limiting<sup>(1)</sup> intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

|                | PARAMETER                               | TEST CONDITIONS                                                                                                                                                      | MIN | TYP MA | X UNIT  |

|----------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|---------|

| DW-16 P        | ACKAGE                                  |                                                                                                                                                                      |     |        |         |

|                |                                         | $R_{\theta JA} = 67.9$ °C/W, $V_I = 5.5$ V, $T_J = 150$ °C, $T_A = 25$ °C, see 🕄 1                                                                                   |     | 33     | 4       |

|                |                                         | $R_{\theta JA} = 67.9^{\circ}\text{C/W}, V_I = 3.6 \text{ V}, T_J = 150^{\circ}\text{C}, T_A = 25^{\circ}\text{C}, \text{ see } \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \$ |     | 51     |         |

| Is             | Safety input, output, or supply current | $R_{\theta JA} = 67.9^{\circ}C/W, V_{I} = 2.75 \text{ V}, T_{J} = 150^{\circ}C, T_{A} = 25^{\circ}C, \text{ see } \boxed{\$} 1$                                      |     | 66     | mA<br>9 |

|                |                                         | $R_{\theta JA} = 67.9^{\circ}C/W, V_I = 1.89 V, T_J = 150^{\circ}C, T_A = 25^{\circ}C, see 2 1$                                                                      |     | 97     | 4       |

| Ps             | Safety input, output, or total power    | $R_{\theta JA} = 67.9$ °C/W, $T_J = 150$ °C, $T_A = 25$ °C, see $2$                                                                                                  |     | 183    | 7 mW    |

| T <sub>S</sub> | Maximum safety temperature              |                                                                                                                                                                      |     | 15     | 0 °C    |

<sup>(1)</sup> The maximum safety temperature,  $T_S$ , has the same value as the maximum junction temperature,  $T_J$ , specified for the device. The  $I_S$  and  $P_S$  parameters represent the safety current and safety power respectively. The maximum limits of  $I_S$  and  $P_S$  should not be exceeded. These limits vary with the ambient temperature, TA.

The junction-to-air thermal resistance, R<sub>6JA</sub>, in the table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.  $T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

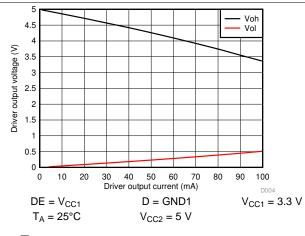

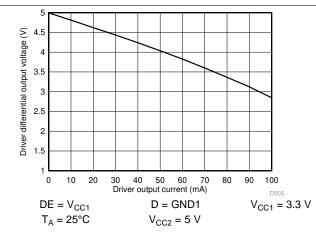

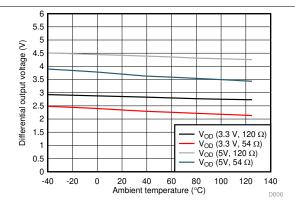

#### 8.9 Electrical Characteristics: Driver

All typical specs are at  $V_{CC1}$ =3.3V,  $V_{CC2}$ =5V,  $T_A$ =27°C, (Min/Max specs are over recommended operating conditions unless otherwise noted)

|                     | PARAMETER                                                            | TEST CONDITIONS                                                                                                                  | MIN  | TYP                    | MAX              | UNIT  |

|---------------------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------------------|-------|

|                     |                                                                      | Open circuit voltage, unloaded bus, 3 V ≤ V <sub>CC2</sub> ≤ 5.5 V                                                               | 1.5  | 5                      | V <sub>CC2</sub> | V     |

|                     |                                                                      | $R_L$ = 60 Ω, −7 V ≤ V <sub>TEST</sub> ≤ 12 V (see $≅$ 35), 3 V ≤ V <sub>CC2</sub> ≤ 3.6 V, T <sub>A</sub> <100C                 | 1.5  | 2.3                    |                  | V     |

|                     |                                                                      | $R_L$ = 60 Ω, -7 V ≤ V <sub>TEST</sub> ≤ 12 V (see $\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                        | 1.5  | 2.3                    |                  |       |

| V <sub>OD</sub>     | Driver differential-output voltage magnitude                         | R <sub>L</sub> = 60 $\Omega$ , -7 V ≤ V <sub>TEST</sub> ≤ 12 V,<br>4.5 V < V <sub>CC2</sub> < 5.5 V (see 🖁 35)                   | 2.1  | 3.7                    |                  | V     |

|                     |                                                                      | R <sub>L</sub> = 100 Ω (see <b>图 36</b> ), RS-422 load                                                                           | 2    | 4.2                    |                  | V     |

|                     |                                                                      | R <sub>L</sub> = 54 $\Omega$ (see $\Xi$ 36), RS-485 load, V <sub>CC2</sub> = 3 V to 3.6 V                                        | 1.5  | 2.3                    |                  | V     |

|                     |                                                                      | $R_L$ = 54 $\Omega$ (see $\Xi$ 36), RS-485 load,<br>4.5 V < V <sub>CC2</sub> < 5.5 V                                             | 2.1  | 3.7                    |                  | V     |

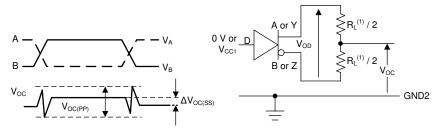

| $\Delta  V_{OD} $   | Change in differential output voltage between two states             | $R_L$ = 54 $\Omega$ or $R_L$ = 100 $\Omega$ , see $2$ 36                                                                         | -200 |                        | 200              | mV    |

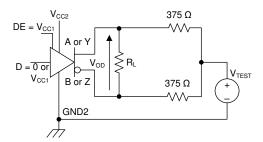

| V <sub>oc</sub>     | Common-mode output voltage                                           | $R_L$ = 54 $\Omega$ or $R_L$ = 100 $\Omega$ , see $2$ 36                                                                         | 1    | 0.5 × V <sub>CC2</sub> | 3                | V     |

| $\Delta V_{OC(SS)}$ | change in steady-state common-mode output voltage between two states | $R_L$ = 54 $\Omega$ or $R_L$ = 100 $\Omega$ , see $\blacksquare$ 36                                                              | -200 |                        | 200              | mV    |

|                     | Chart siza it autaut aureat                                          | $V_D = V_{CC1} \text{ or } V_D = V_{GND1}, V_{DE} = V_{CC1}, V_{CC2} = 3.3 \text{V} \pm 10\%$<br>-7 V \le V \le 12 V, see \le 45 | -250 |                        | 250              | mA    |

| l <sub>os</sub>     | Short-circuit output current                                         | $V_D = V_{CC1}$ or $V_D = V_{GND1}$ , $V_{DE} = V_{CC1}$ , $V_{CC2} = 5V \pm 10\%$<br>-7 V \le V \le 12 V, see \le 45            |      | 250                    |                  | mA    |

| li                  | Input current                                                        | $V_D$ and $V_{DE} = 0$ V or $V_D$ and $V_{DE} = V_{CC1}$                                                                         | -10  |                        | 10               | μΑ    |

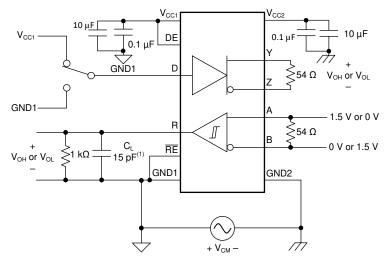

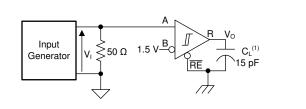

| CMTI                | Common-mode transient immunity                                       | $V_D = V_{CC1}$ or GND1, $V_{CC1} = 1.71$ V to 5.5 V, $V_{CM} = 1200$ V, ISO141x, See $\blacksquare$ 38                          | 85   | 100                    |                  | kV/μs |

| CMTI                | Common-mode transient immunity                                       | $V_D = V_{CC1}$ or GND1, $V_{CC1} = 1.71$ V to 5.5 V, $V_{CM} = 1200$ V, ISO143x, See $\ 38$                                     | 85   | 100                    |                  | kV/μs |

| CMTI                | Common-mode transient immunity                                       | V <sub>D</sub> =V <sub>CC1</sub> or GND1, V <sub>CC1</sub> = 2.25 V to 5.5 V, V <sub>CM</sub> = 1200 V, ISO145x, See 图 38        | 85   | 100                    |                  | kV/µs |

## 8.10 Electrical Characteristics: Receiver

All typical specs are at  $V_{CC1}$ =3.3V,  $V_{CC2}$ =5V,  $T_A$ =27°C, (Min/Max specs are over recommended operating conditions unless otherwise noted)

|                   | PARAMETER                                               | TEST CONDITIONS                                                                                                                                                                      | MIN                    | TYP  | MAX     | UNIT |

|-------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|---------|------|

| I <sub>i1</sub>   | Bus input current                                       | $V_{DE} = 0 \text{ V}, V_{CC2} = 0 \text{ V or } V_{CC2} = 5.5 \text{ V}, 500\text{-kbps}$ devices, $V_I = -7 \text{ V or } V_I = 12 \text{ V}, \text{ other input at } 0 \text{ V}$ | -100                   |      | 125     | μA   |

| I <sub>i1</sub>   | Bus input current                                       | $V_{DE}=0$ V, $V_{CC2}=0$ V or $V_{CC2}=5.5$ V, 12-Mbps and 50-Mbps devices, $V_{I}=-7$ V or $V_{I}=12$ V, other input at 0 V                                                        | -100                   |      | 125     | μΑ   |

| l <sub>i1</sub>   | Bus input current                                       | $V_{DE} = 0$ V, $V_{CC2} = 0$ V or $V_{CC2} = 5.5$ V, 500-kbps devices, $V_I = -15$ V or $V_I = 15$ V, other input at 0 V                                                            | -200                   |      | 125     | μΑ   |

| I <sub>i1</sub>   | Bus input current                                       | $V_{DE}=0\ V,\ V_{CC2}=0\ V$ or $V_{CC2}=5.5\ V,\ 12\text{-Mbps}$ and 50-Mbps devices, $V_I=-15\ V$ or $V_I=15\ V,$ other input at 0 V                                               | -200                   |      | 125     | μΑ   |

|                   | Danish and a second should be let us be a               | -15 V ≤ V <sub>CM</sub> ≤ 15 V                                                                                                                                                       | See (1)                | -100 | -10     | mV   |

| V <sub>TH+</sub>  | Positive-going input threshold voltage                  | -7 V ≤ V <sub>CM</sub> ≤ 12 V                                                                                                                                                        | See (1)                | -100 | -20     | mV   |

| V <sub>TH</sub> _ | Negative-going input threshold voltage                  | -15 V ≤ V <sub>CM</sub> ≤ 15 V                                                                                                                                                       | -200                   | -130 | See (1) | mV   |

| V <sub>hys</sub>  | Input hysteresis (V <sub>TH+</sub> – V <sub>TH-</sub> ) | -15 V ≤ V <sub>CM</sub> ≤ 15 V                                                                                                                                                       |                        | 30   |         | mV   |

|                   |                                                         | $V_{CC1}$ =5V ± 10%, $I_{OH}$ = -4 mA, $V_{ID}$ = 200 mV                                                                                                                             | V <sub>CC1</sub> - 0.4 |      |         | V    |

| V <sub>OH</sub>   | Output high voltage on the R pin                        | $V_{CC1}$ =3.3V ± 10%, $I_{OH}$ = -2 mA, $V_{ID}$ = 200 mV                                                                                                                           | V <sub>CC1</sub> - 0.3 |      |         | V    |

| ·OH               | Supering. Total go on the fit pin                       | $V_{\rm CC1}$ =2.5V ± 10%, 1.8V+/-5%, $I_{\rm OH}$ = -1 mA, $V_{\rm ID}$ = 200 mV                                                                                                    | V <sub>CC1</sub> - 0.2 |      |         | V    |

<sup>(1)</sup> Under any specific conditions,  $V_{TH+}$  is ensured to be at least  $V_{hys}$  higher than  $V_{TH-}$ .

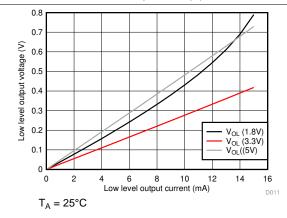

## **Electrical Characteristics: Receiver (continued)**

All typical specs are at  $V_{CC1}$ =3.3V,  $V_{CC2}$ =5V,  $T_A$ =27°C, (Min/Max specs are over recommended operating conditions unless otherwise noted)

|                 | PARAMETER                                       | TEST CONDITIONS                                                                                                   | MIN | TYP | MAX | UNIT  |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

|                 | V <sub>OI</sub> Output low voltage on the R pin | $V_{CC1}$ =5V ± 10%, $I_{OL}$ = 4 mA, $V_{ID}$ = -200 mV                                                          |     |     | 0.4 | V     |

| V <sub>OL</sub> |                                                 | $V_{CC1}$ =3.3V ± 10%, $I_{OL}$ = 2 mA, $V_{ID}$ = -200 mV                                                        |     |     | 0.3 | V     |

| - OL            | out particular and a second                     | $V_{CC1}$ =2.5V ± 10%, 1.8V ± 5%, $I_{OL}$ = 1 mA, $V_{ID}$ = -200 mV                                             |     |     | 0.2 | V     |

| I <sub>OZ</sub> | Output high-impedance current on the R pin      | $V_R = 0 \text{ V or } V_R = V_{CC1}, V_{\overline{RE}} = V_{CC1}$                                                | -1  |     | 1   | μΑ    |

| Ii              | Input current on the RE pin                     | $V_{\overline{RE}} = 0 \text{ V or } V_{\overline{RE}} = V_{CC1}$                                                 | -10 |     | 10  | μA    |

| CMTI            | Common-mode transient immunity                  | V <sub>CC1</sub> =1.71 V to 5.5 V, V <sub>ID</sub> = 1.5 V or -1.5 V, V <sub>CM</sub> = 1200 V, ISO141x, See 图 38 | 85  | 100 |     | kV/µs |

| CMTI            | Common-mode transient immunity                  | V <sub>CC1</sub> =1.71 V to 5.5 V, V <sub>ID</sub> = 1.5 V or -1.5 V, V <sub>CM</sub> = 1200 V, ISO143x, See 图 38 | 85  | 100 |     | kV/μs |

| CMTI            | Common-mode transient immunity                  | V <sub>CC1</sub> =2.25 V to 5.5 V, V <sub>ID</sub> = 1.5 V or -1.5 V, V <sub>CM</sub> = 1200 V, ISO145x, See 图 38 | 85  | 100 |     | kV/μs |

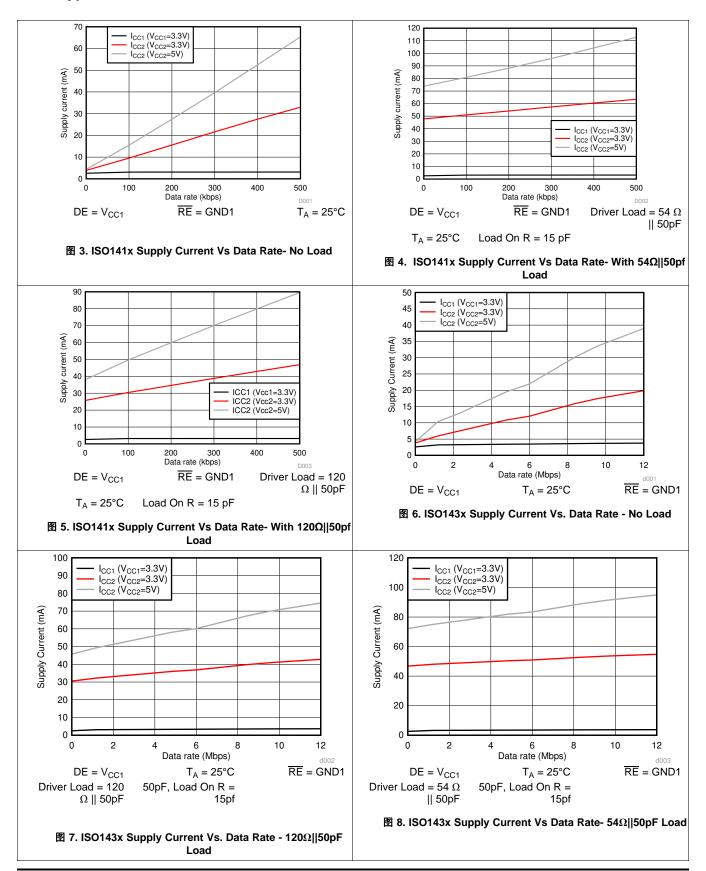

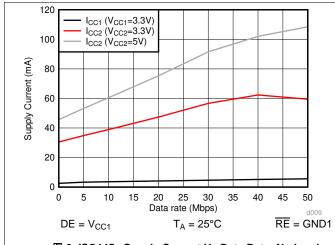

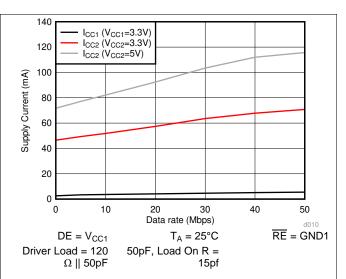

## 8.11 Supply Current Characteristics: Side 1 (I<sub>CC1</sub>)

Bus loaded or unloaded (over recommended operating conditions unless otherwise noted)

| PARAMETER                 | TEST CONDITIONS                                                                                                                                                                               | MIN | TYP | MAX      | UNIT   |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|--------|

|                           | D, RECEIVER DISABLED                                                                                                                                                                          |     |     | 1117 171 | Oitiii |

| Logic-side supply current | $V_D = V_{CC1}, V_{CC1} = 5 \text{ V} \pm 10\%$                                                                                                                                               |     | 2.6 | 4.4      | mA     |

| Logic-side supply current | $V_D = V_{CC1}, V_{CC1} = 3.3 \text{ V} \pm 10\%$                                                                                                                                             |     | 2.6 | 4.4      | mA     |

| Logic-side supply current | ISO141x, D = 500-kbps square wave with 50% duty cycle, $V_{CC1}$ = 5 V $\pm$ 10%                                                                                                              |     | 3.2 | 5.1      | mA     |

| Logic-side supply current | ISO141x, D = 500-kbps square wave with 50% duty cycle, $V_{CC1}$ = 3.3 V $\pm$ 10%                                                                                                            |     | 3.2 | 5.1      | mA     |

| Logic-side supply current | ISO143x, D = 12-Mbps square wave with 50% duty cycle, $V_{CC1}$ = 5 V $\pm$ 10%                                                                                                               |     | 3.2 | 5.1      | mA     |

| Logic-side supply current | ISO143x, D = 12-Mbps square wave with 50% duty cycle, $V_{CC1}$ = 3.3 V $\pm$ 10%                                                                                                             |     | 3.2 | 5.1      | mA     |

| Logic-side supply current | ISO145x, D = 50-Mbps square wave with 50% duty cycle, $V_{CC1}$ = 5 V $\pm$ 10%                                                                                                               |     | 3.6 | 5.3      | mA     |

| Logic-side supply current | ISO145x, D = 50-Mbps square wave with 50% duty cycle, V <sub>CC1</sub> = 3.3 V ± 10%                                                                                                          |     | 3.4 | 5.2      | mA     |

|                           | D, RECEIVER ENABLED                                                                                                                                                                           |     |     |          |        |

| Logic-side supply current | $V_{\overline{RE}} = V_{GND1}$ , loopback if full-duplex device, $V_D = V_{CC1}$ , $V_{CC1} = 5 \text{ V} \pm 10\%$                                                                           |     | 2.6 | 4.4      | mA     |

| Logic-side supply current | $V_{\overline{RE}} = V_{GND1}$ , loopback if full-duplex device, $V_D = V_{CC1}$ , $V_{CC1} = 3.3 \text{ V} \pm 10\%$                                                                         |     | 2.6 | 4.4      | mA     |

| Logic-side supply current | ISO141x, $V_{RE} = V_{GND1}$ , loopback if full-duplex device, D = 500-kbps square wave with 50% duty cycle, $V_{CC1} = 5~V \pm 10\%$ , $C_{L(R)}^{(1)} = 15~pF$                              |     | 3.3 | 5.1      | mA     |

| Logic-side supply current | ISO141x, $V_{RE} = V_{GND1}$ , loopback if full-duplex device, D = 500-kbps square wave with 50% duty cycle, $V_{CC1} = 3.3~V \pm 10\%$ , $C_{L(R)}^{(1)} = 15~pF$                            |     | 3.2 | 5.1      | mA     |

| Logic-side supply current | ISO143x, $V_{RE} = V_{GND1}$ , loopback if full-duplex device, D = 12-Mbps square wave with 50% duty cycle, $V_{CC1} = 5~V \pm 10\%$ , $C_{L(R)}^{(1)} = 15~pF$                               |     | 4.1 | 6        | mA     |

| Logic-side supply current | ISO143x, $V_{\overline{RE}}$ = $V_{GND1}$ , loopback if full-duplex device, D= 12-Mbps square wave with 50% duty cycle, $V_{CC1}$ = 3.3 V ± 10%, $C_{L(R)}^{(1)}$ = 15 pF                     |     | 3.8 | 5.7      | mA     |

| Logic-side supply current | $ISO145x$ , $V_{\overline{RE}} = V_{GND1}$ , loopback if full-duplex device, D = 50-Mbps square wave with 50% duty cycle, $V_{CC1} = 5 \text{ V} \pm 10\%$ , $C_{L(R)}^{(1)} = 15 \text{ pF}$ |     | 6.3 | 8.9      | mA     |

| Logic-side supply current | ISO145x, $V_{RE} = V_{GND1}$ , loopback if full-duplex device, D= 50-Mbps square wave with 50% duty cycle, $V_{CC1} = 3.3~V \pm 10\%$ , $C_{L(R)}^{(1)} = 15~pF$                              |     | 5.3 | 7.8      | mA     |

| DRIVER DISABLE            | D, RECEIVER ENABLED                                                                                                                                                                           |     |     |          |        |

| Logic-side supply current | $V_{(A-B)} \ge 200 \text{ mV}, V_D = V_{CC1}, V_{CC1} = 5 \text{ V} \pm 10\%$                                                                                                                 |     | 1.6 | 3.1      | mA     |

| Logic-side supply current | $V_{(A-B)} \ge 200 \text{ mV}, V_D = V_{CC1}, V_{CC1} = 3.3 \text{ V} \pm 10\%$                                                                                                               |     | 1.6 | 3.1      | mA     |

| Logic-side supply current | ISO141x, (A-B) = 500-kbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 5$ V $\pm$ 10%, $C_{L(R)}^{(1)} = 15$ pF                                                              |     | 1.7 | 3.1      | mA     |

| Logic-side supply current | ISO141x, (A-B) = 500-kbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 3.3 \text{ V} \pm 10\%$ , $C_{L(R)}^{(1)} = 15 \text{ pF}$                                            |     | 1.6 | 3.1      | mA     |

| Logic-side supply current | ISO143x, (A-B) = 12-Mbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 5 \text{ V} \pm 10\%$ , $C_{L(R)}^{(1)} = 15 \text{ pF}$                                               |     | 2.6 | 4        | mA     |

| Logic-side supply current | ISO143x, (A-B) = 12-Mbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 3.3 \text{ V} \pm 10\%$ , $C_{L(R)}^{(1)} = 15 \text{ pF}$                                             |     | 2.2 | 3.7      | mA     |

| Logic-side supply current | ISO145x, (A-B) = 50-Mbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 5 \text{ V} \pm 10\%$ , $C_{L(R)}^{(1)} = 15 \text{ pF}$                                               |     | 4.7 | 6.7      | mA     |

| Logic-side supply current | ISO145x, (A-B) = 50-Mbps square wave with 50% duty cycle, $V_D = V_{CC1}$ , $V_{CC1} = 3.3 \text{ V} \pm 10\%$ , $C_{L(R)}{}^{(1)} = 15 \text{ pF}$                                           |     | 3.7 | 5.7      | mA     |

| DRIVER DISABLE            | ED, RECEIVER DISABLED                                                                                                                                                                         |     |     |          |        |

| Logic-side supply current | $V_{DE} = V_{GND1}, V_D = V_{CC1}, V_{CC1} = 5 \text{ V} \pm 10\%$                                                                                                                            |     | 1.6 | 3.1      | mA     |

| Logic-side supply current | $V_{DE} = V_{GND1}, V_D = V_{CC1}, V_{CC1} = 3.3 \text{ V} \pm 10\%$                                                                                                                          |     | 1.6 | 3.1      | mA     |

<sup>(1)</sup>  $C_{L(R)}$  is the load capacitance on the R pin.

## 8.12 Supply Current Characteristics: Side 2 (I<sub>CC2</sub>)

$V_{\overline{RE}} = V_{GND1}$  or  $V_{\overline{RE}} = V_{CC1}$  (over recommended operating conditions unless otherwise noted)

| PARAMETER               | TEST CONDITIONS                                                                                                                                 | MIN | TYP | MAX | UNIT |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| DRIVER ENABLE           | D, BUS UNLOADED                                                                                                                                 |     |     |     |      |

| Bus-side supply current | $V_D = V_{CC1}, V_{CC2} = 3.3 \text{ V} \pm 10\%$                                                                                               |     | 4   | 6.1 | mA   |

| Bus-side supply current | $V_D = V_{CC1}, V_{CC2} = 5 \text{ V} \pm 10\%$                                                                                                 |     | 4.5 | 6.6 | mA   |

| DRIVER ENABLE           | ED, BUS LOADED                                                                                                                                  |     |     |     |      |

| Bus-side supply current | $V_D = V_{CC1}, R_L = 54 \Omega, V_{CC2} = 3.3 V \pm 10\%$                                                                                      |     | 48  | 58  | mA   |

| Bus-side supply current | $V_D = V_{CC1}, R_L = 54 \Omega, V_{CC2} = 5 V \pm 10\%$                                                                                        |     | 74  | 88  | mA   |

| Bus-side supply current | ISO141x, D = 500-kbps square wave with 50% duty cycle, R <sub>L</sub> = 54 $\Omega$ , C <sub>L</sub> = 50 pF, V <sub>CC2</sub> = 3.3 V ± 10%    |     | 63  | 95  | mA   |

| Bus-side supply current | ISO141x, D = 500-kbps square wave with 50% duty cycle, $R_L$ = 54 $\Omega$ , $C_L$ = 50 pF, $V_{CC2}$ = 5 V ± 10%                               |     | 113 | 160 | mA   |

| Bus-side supply current | ISO143x, D = 12-Mbps square wave with 50% duty cycle, R <sub>L</sub> = 54 $\Omega$ , C <sub>L</sub> = 50 pF, V <sub>CC2</sub> = 3.3 V $\pm$ 10% |     | 56  | 75  | mA   |

| Bus-side supply current | ISO143x, D = 12-Mbps square wave with 50% duty cycle, R <sub>L</sub> = 54 $\Omega$ , C <sub>L</sub> = 50 pF, V <sub>CC2</sub> = 5 V $\pm$ 10%   |     | 97  | 122 | mA   |

| Bus-side supply current | ISO145x, D = 50-Mbps square wave with 50% duty cycle, R <sub>L</sub> = 54 $\Omega$ , C <sub>L</sub> = 50 pF, V <sub>CC2</sub> = 3.3 V $\pm$ 10% |     | 84  | 103 | mA   |

| Bus-side supply current | ISO145x, D = 50-Mbps square wave with 50% duty cycle, R <sub>L</sub> = 54 $\Omega$ , C <sub>L</sub> = 50 pF, V <sub>CC2</sub> = 5 V $\pm$ 10%   |     | 134 | 162 | mA   |

| DRIVER DISABLI          | ED, BUS LOADED OR UNLOADED                                                                                                                      |     |     | ·   |      |

| Bus-side supply current | $V_D = V_{CC1}, V_{CC2} = 3.3 \text{ V} \pm 10\%$                                                                                               |     | 2.6 | 4.3 | mA   |

| Bus-side supply current | $V_D = V_{CC1}, V_{CC2} = 5 \text{ V} \pm 10\%$                                                                                                 |     | 2.8 | 4.5 | mA   |

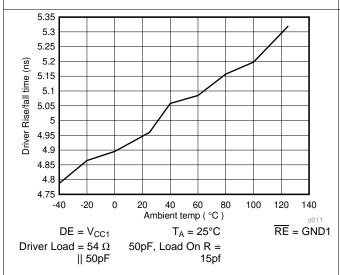

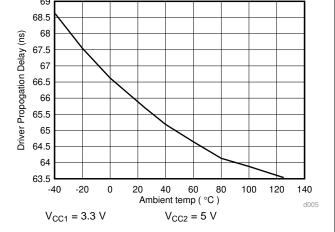

## 8.13 Switching Characteristics: Driver

All typical specs are at  $V_{CC1}$ =3.3V,  $V_{CC2}$ =5V,  $T_A$ =27°C, (Min/Max specs are over recommended operating conditions unless otherwise noted)

|                                     | PARAMETER                                                                    | TEST CONDITIONS                                                             | MIN | TYP | MAX  | UNIT |

|-------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|------|------|

| 500-kbps                            | DEVICES                                                                      |                                                                             |     |     |      |      |

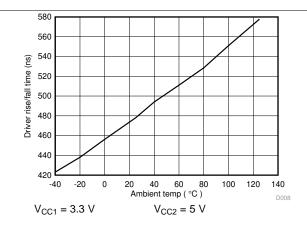

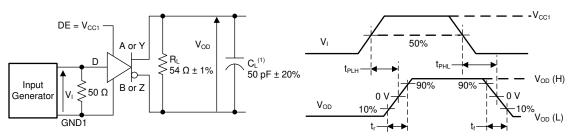

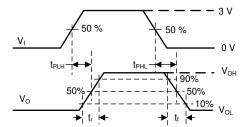

| t <sub>r</sub> , t <sub>f</sub>     | Differential output rise time and fall time                                  | $R_L$ = 54 Ω, $C_L$ = 50 pF, see 🛭 37                                       |     | 460 | 680  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay                                                            | $R_L = 54 \Omega$ , $C_L = 50 pF$ , see $37$                                |     | 310 | 570  | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup> ,  t <sub>PHL</sub> - t <sub>PLH</sub> | $R_L = 54 \Omega$ , $C_L = 50 pF$ , see $37$                                |     | 4   | 50   | ns   |

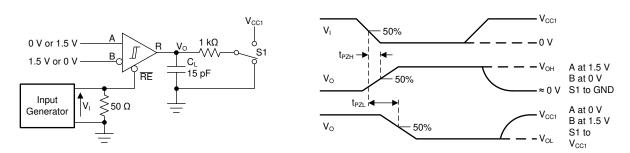

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Disable time                                                                 | See 图 40, and 图 41                                                          |     | 125 | 200  | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Enable time                                                                  | See 图 40, and 图 41                                                          |     | 160 | 600  | ns   |

| 12-Mbps                             | DEVICES                                                                      |                                                                             |     |     | ·    |      |

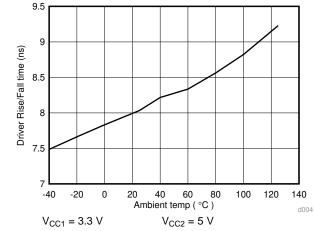

|                                     | Differential output via time and fall time                                   | $R_L$ = 54 Ω, $C_L$ = 50 pF, $V_{CC2}$ = 4.5 V to 5.5 V, see $37$           |     | 10  | 25   | ns   |

| t <sub>r</sub> , t <sub>f</sub>     | Differential output rise time and fall time                                  | $R_L$ = 54 Ω, $C_L$ = 50 pF, $V_{CC2}$ = 3 V to 3.6 V, see $37$             |     |     | 27.8 | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay                                                            | $R_L$ = 54 Ω, $C_L$ = 50 pF, see $37$                                       |     | 68  | 125  | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup> ,  t <sub>PHL</sub> - t <sub>PLH</sub> | $R_L$ = 54 Ω, $C_L$ = 50 pF, see 🛭 37                                       |     | 2   | 10   | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Disable time                                                                 | See 图 40, and 图 41                                                          |     | 75  | 125  | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Enable time                                                                  | See 图 40, and 图 41                                                          |     | 75  | 160  | ns   |

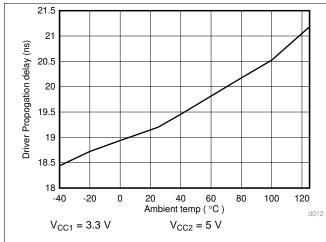

| 50-Mbps                             | DEVICES                                                                      |                                                                             |     |     | ·    |      |

|                                     | Differential output vice time and fall time                                  | $R_L$ = 54 Ω, $C_L$ = 50 pF, $V_{CC2}$ = 4.5 V to 5.5 V, see $\boxed{8}$ 37 |     | 4.7 | 6    | ns   |

| t <sub>r</sub> , t <sub>f</sub>     | Differential output rise time and fall time                                  | $R_L$ = 54 Ω, $C_L$ = 50 pF, $V_{CC2}$ = 3 V to 3.6 V, see $37$             |     |     | 7.8  | ns   |

| t <sub>PHL</sub> , t <sub>PLH</sub> | Propagation delay                                                            | $R_L$ = 54 Ω, $C_L$ = 50 pF, see $37$                                       |     | 19  | 41   | ns   |

| PWD                                 | Pulse width distortion <sup>(1)</sup> ,  t <sub>PHL</sub> - t <sub>PLH</sub> | $R_L$ = 54 Ω, $C_L$ = 50 pF, see $37$                                       |     | 1   | 6    | ns   |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Disable time                                                                 | See 图 40, and 图 41                                                          |     | 25  | 46   | ns   |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Enable time                                                                  | See 图 40, and 图 41                                                          |     | 32  | 78   | ns   |

<sup>(1)</sup> Also known as pulse skew.

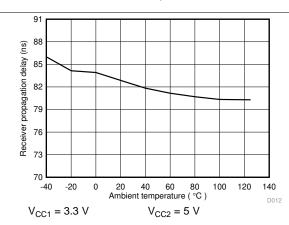

## 8.14 Switching Characteristics: Receiver