**TPS65186**

ZHCS462A - JULY 2011-REVISED AUGUST 2015

# TPS65186 面向 E Ink<sup>®</sup> Vizplex™电子纸显示屏的 PMIC

### 1 特性

- 面向

- E Ink® Vizplex™电子纸显示屏的单芯片电源管理解 决方案

- 通过单个低电压输入电源生成正负栅极和源级驱动 电压以及背板偏置电压

- 支持 9.7 英寸及以上的显示屏尺寸

- 输入电压范围: 3V 至 6V

- 用于正电源轨基 (Positive Rail Base) 的升压转换器

- 用于负电源轨基 (Negative Rail Base) 的反向降压-升压转换器

- 两个可调节的 LDO, 用于提供源级驱动电源

- LDO1: 15V, 120mA (VPOS)

- LDO2: -15V, 120mA (VNEG)

- 精确输出电压跟踪

- VPOS VNEG = ±50mV

- 两个电荷泵,用于提供栅极驱动电源

- CP1: 22V, 10mA (VDDH)

- CP2: -20V, 12mA (VEE)

- 可调节的 VCOM 驱动器,用于提供精确的面板背 板偏置电压

- 0V 至 -5.11V

- 精度为 ± 1.5% (±10mV)

- 9 位控制(标称步长为 10mV)

- 集成 10Ω、3.3V 电源开关(用于禁用 E-Ink 显示屏的系统电源轨)

### 2 应用

- 有源矩阵 E Ink Vizplex 显示屏的电源

- EPD 电源

- 电子书阅读器

- EPSON®S1D13522 (ISIS) 定时控制器

- EPSON<sup>®</sup>S1D13521 (宽幅印刷品) 定时控制器

- 具有集成型或软件定时控制器的应用处理器 (OMAP™)

#### 3 说明

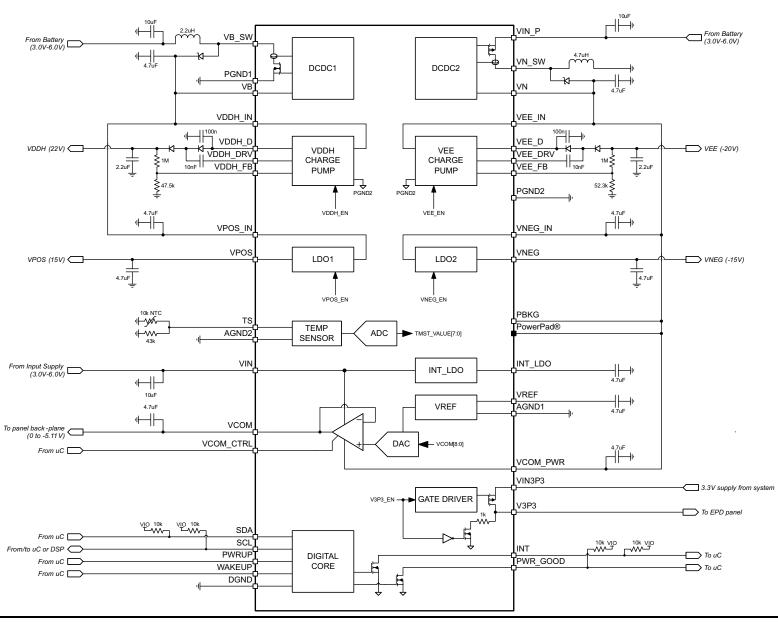

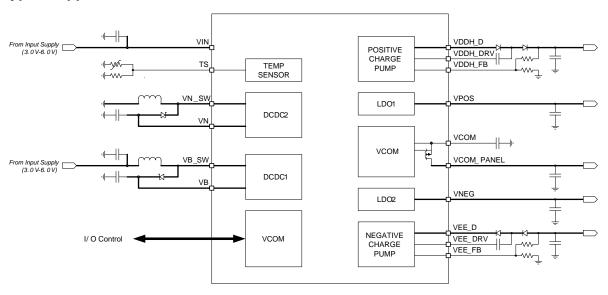

TPS65186 器件是一款单芯片电源,专为为便携式电子阅读器 应用中的 E Ink Vizplex 显示屏而设计。此器件支持 9.7 英寸及以上的显示屏尺寸。两个高效 DC-DC 升压转换器生成 ±16V 电压轨。这两个电压轨通过两个电荷泵分别升压至 22V 和 –20V,从而为 Vizplex显示屏提供栅极驱动电源。两个跟踪 LDO 生成 ±15V 源级驱动电源,最高支持 120mA 的输出电流。所有电压轨均可通过 I<sup>2</sup>C 接口进行调节,从而适应特定的显示屏要求。

#### 器件信息(1)

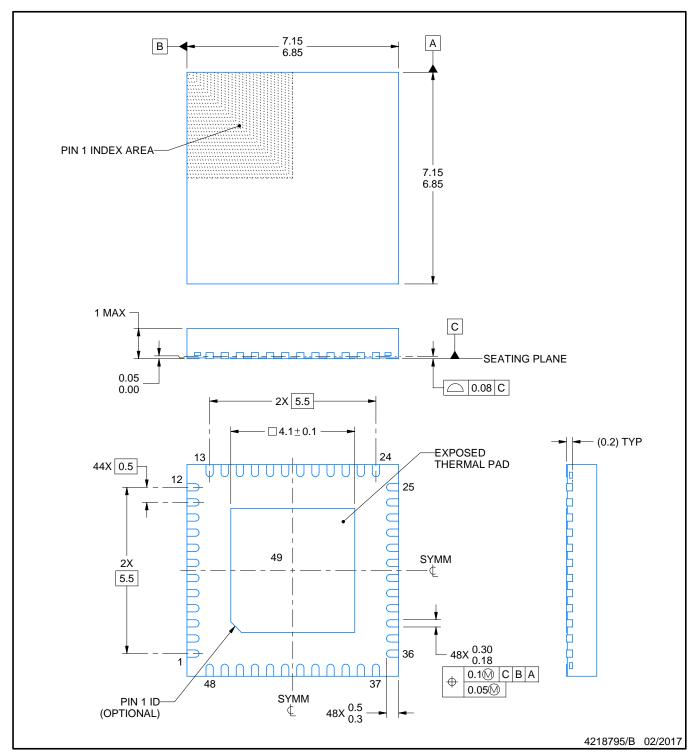

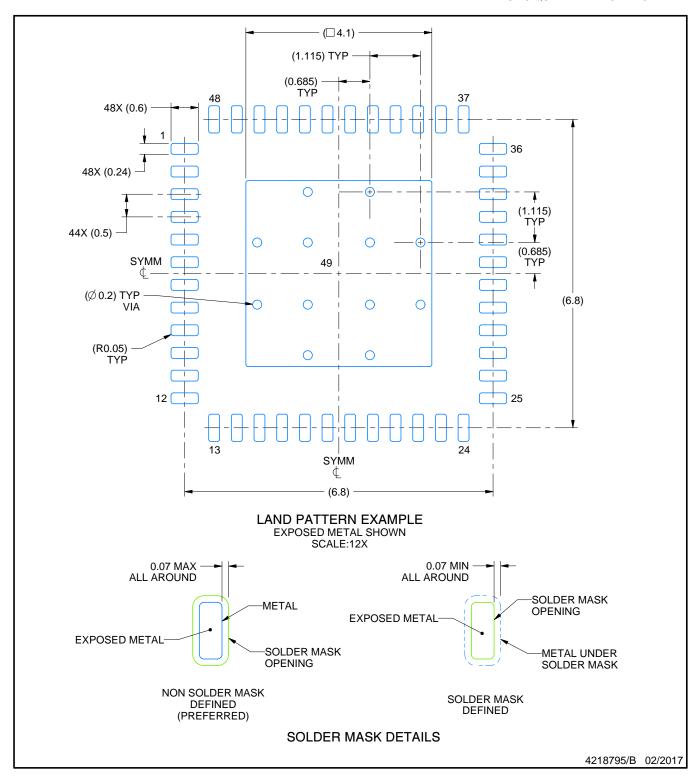

| 器件型号     | 封装        | 封装尺寸 (标称值)      |

|----------|-----------|-----------------|

| TPS65186 | VQFN (48) | 7.00mm x 7.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

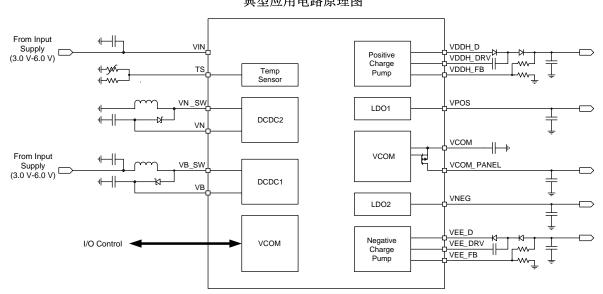

## 典型应用电路原理图

13 机械、封装和可订购信息......47

|   |                                            | 目录 |    |                                |    |

|---|--------------------------------------------|----|----|--------------------------------|----|

| 1 | 特性                                         |    |    | 8.4 Device Functional Modes    | 24 |

| 2 | 应用                                         |    |    | 8.5 Programming                | 26 |

| 3 |                                            |    |    | 8.6 Register Maps              | 27 |

| 4 | 修订历史记录                                     |    | 9  | Application and Implementation | 44 |

| 5 | 说明(续)                                      |    |    | 9.1 Application Information    | 44 |

| 6 | Pin Configuration and Functions            |    |    | 9.2 Typical Application        | 44 |

| - | 5                                          |    | 10 | Power Supply Recommendations   | 46 |

| 7 | Specifications                             |    | 11 | Layout                         | 46 |

|   | 7.1 Absolute Maximum Ratings               |    |    | 11.1 Layout Guidelines         | 46 |

|   | 7.3 Recommended Operating Conditions       |    |    | 11.2 Layout Example            | 46 |

|   | 7.4 Thermal Information                    |    | 12 | 器件和文档支持                        | 47 |

|   | 7.5 Electrical Characteristics 6           |    |    | 12.1 器件支持                      | 47 |

|   | 7.6 Timing Requirements: Data Transmission |    |    | 12.2 社区资源                      | 47 |

|   | 7.7 Typical Characteristics                |    |    | 12.3 商标                        | 47 |

|   | Potailed Description 15                    |    |    | 12.4 静电放电警告                    | 47 |

## 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

#### Changes from Original (July 2011) to Revision A

Detailed Description ...... 15

8.2 Functional Block Diagram ...... 16

**Page**

| • | Changed $R_{OUT}$ from "TBD" to "5 $\Omega$ ". |           |          |           |       |      | . 8 |

|---|------------------------------------------------|-----------|----------|-----------|-------|------|-----|

|   | 档支持部分以及机械、封装和可订购                               | 信息部分      |          |           |       |      | . 1 |

| • | 己添加 <i>ESD 额定值</i> 表,特性 描述部                    | 分,器件功能模式, | 应用和实施部分, | 电源相关建议部分, | 布局部分, | 器件和文 |     |

#### 5 说明 (续)

该器件通过线性放大器来提供精确的背板偏置电压,并通过串行接口对电压值进行 9 位控制,电压值可调节范围为 0V 至 -5.11V;并且具备灌/拉电流能力,能够适应不同的显示屏条件。TPS65186 支持自动显示屏跳变电压测量,免除了在生产线上手动进行 VCOM 校准的需要。测量结果会储存在非易失性存储器中,成为新的 VCOM 上电默认值。

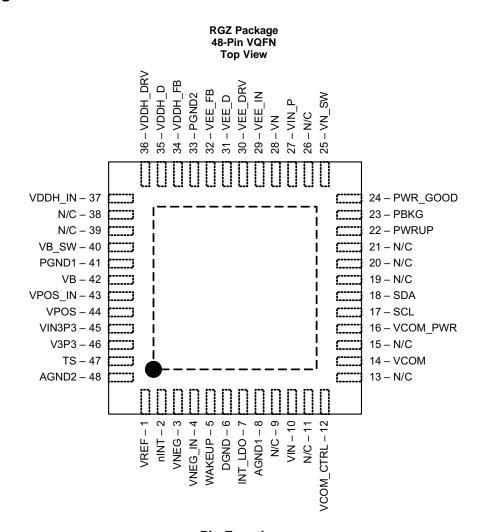

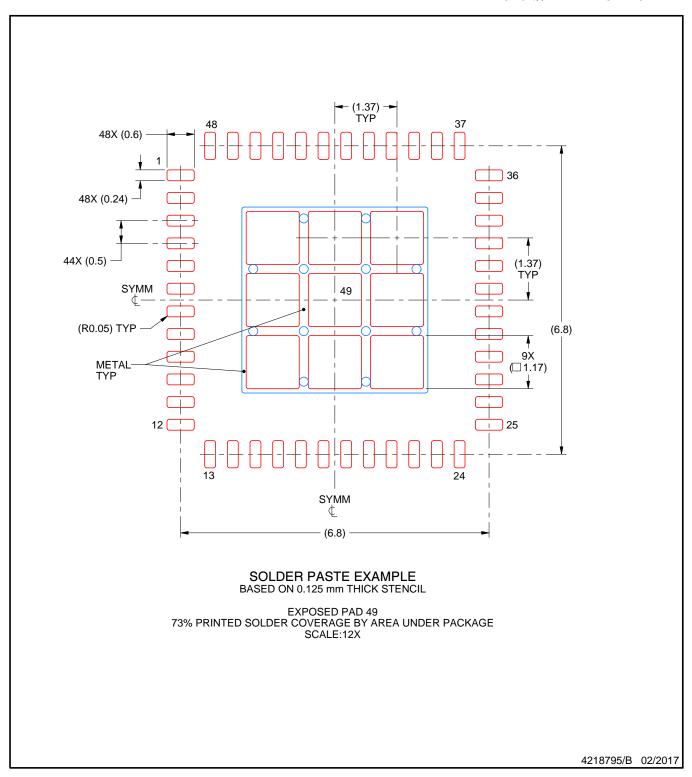

TPS65186 采用间距为 0.5mm 的 48 引脚 7mm x 7mm<sup>2</sup> VQFN 封装。

## 6 Pin Configuration and Functions

### **Pin Functions**

|         | 1 111 1 4114111111                          |     |                                                                   |  |  |  |  |

|---------|---------------------------------------------|-----|-------------------------------------------------------------------|--|--|--|--|

| PIN     |                                             | 1/0 | DECODIDATION                                                      |  |  |  |  |

| NAME    | NO.                                         | 1/0 | DESCRIPTION                                                       |  |  |  |  |

| AGND1   | 8                                           | _   | Analog ground for general analog circuitry                        |  |  |  |  |

| AGND2   | 48                                          | _   | Reference point to external thermistor and linearization resistor |  |  |  |  |

| DGND    | 6                                           | _   | Digital ground. Connect to ground plane.                          |  |  |  |  |

| INT_LDO | 7                                           | 0   | Filter pin for 2.7-V internal supply                              |  |  |  |  |

| nINT    | 2                                           | 0   | Open drain interrupt pin (active low)                             |  |  |  |  |

| N/C     | 9, 11, 13, 15,<br>19, 20, 21, 26,<br>38, 39 | _   | Not internally connected                                          |  |  |  |  |

#### Pin Functions (continued)

| PIN       | ı  | 1/0 | DESCRIPTION                                                                                                                                                                                                                   |  |  |

|-----------|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME NO.  |    | I/O | DESCRIPTION                                                                                                                                                                                                                   |  |  |

| PBKG      | 23 | _   | Die substrate. Connect to VN (–16 V) with short, wide trace. Wide copper trace will improve heat dissipation.                                                                                                                 |  |  |

| PGND1     | 41 | _   | Power ground for DCDC1                                                                                                                                                                                                        |  |  |

| PGND2     | 33 | _   | Power ground for CP1 (VDDH) and CP2 (VEE) charge pumps                                                                                                                                                                        |  |  |

| PWR_GOOD  | 24 | 0   | Open-drain power good output pin. Pin is pulled low when one or more rails are disabled or not in regulation. DCDC1, DCDC2, and VCOM have no effect on this pin. (1)                                                          |  |  |

| PWRUP     | 22 | 1   | Power-up pin. Pull this pin high to power up all output rails. (1)                                                                                                                                                            |  |  |

| SCL       | 17 | - 1 | Serial interface (I <sup>2</sup> C) clock input                                                                                                                                                                               |  |  |

| SDA       | 18 | I/O | Serial interface (I <sup>2</sup> C) data input/output                                                                                                                                                                         |  |  |

| TS        | 47 | 1   | Thermistor input pin. Connect a 10-k $\Omega$ NTC thermistor and a 43-k $\Omega$ linearization resistor between this pin and AGND.                                                                                            |  |  |

| V3P3      | 46 | 0   | Output pin of 3.3-V power switch                                                                                                                                                                                              |  |  |

| VB        | 42 | I   | Feedback pin for boost converter (DCDC1) and supply for VPOS LDO and VDDH charge pump                                                                                                                                         |  |  |

| VB_SW     | 40 | 0   | Boost converter switch out (DCDC1)                                                                                                                                                                                            |  |  |

| VCOM      | 14 | 1   | Filter pin for panel common-voltage driver                                                                                                                                                                                    |  |  |

| VCOM_CTRL | 12 | ı   | VCOM enable. Pull this pin high to enable the VCOM amplifier. When pin is pulled low and VN is enabled, VCOM discharge is enabled. (2)                                                                                        |  |  |

| VCOM_PWR  | 16 | 1   | Internal supply input pin to VCOM buffer. Connect to the output of DCDC2.                                                                                                                                                     |  |  |

| VDDH_D    | 35 | 0   | Base voltage output pin for positive charge pump (CP1)                                                                                                                                                                        |  |  |

| VDDH_DRV  | 36 | 0   | Driver output pin for positive charge pump (CP1)                                                                                                                                                                              |  |  |

| VDDH_FB   | 34 | 1   | Feedback pin for positive charge pump (CP1)                                                                                                                                                                                   |  |  |

| VDDH_IN   | 37 | I   | Input supply pin for positive charge pump (CP1)                                                                                                                                                                               |  |  |

| VEE_D     | 31 | I   | Base voltage output pin for negative charge pump (CP2)                                                                                                                                                                        |  |  |

| VEE_DRV   | 30 | 0   | Driver output pin for negative charge pump (CP2)                                                                                                                                                                              |  |  |

| VEE_FB    | 32 | I   | Feedback pin for negative charge pump (CP2)                                                                                                                                                                                   |  |  |

| VEE_IN    | 29 | 1   | Input supply pin for negative charge pump (CP2) (VEE)                                                                                                                                                                         |  |  |

| VIN       | 10 | I   | Input power supply to general circuitry                                                                                                                                                                                       |  |  |

| VIN3P3    | 45 | I   | Input pin to 3.3-V power switch                                                                                                                                                                                               |  |  |

| VIN_P     | 27 | I   | Input power supply to inverting buck-boost converter (DCDC2)                                                                                                                                                                  |  |  |

| VN        | 28 | 1   | Feedback pin for inverting buck-boost converter (DCDC2) and supply for VNEG LDO and VEE charge pump                                                                                                                           |  |  |

| VNEG      | 3  | 0   | Negative supply output pin for panel source drivers                                                                                                                                                                           |  |  |

| VNEG_IN   | 4  | 1   | Input pin for LDO2 (VNEG)                                                                                                                                                                                                     |  |  |

| VN_SW     | 25 | 0   | Inverting buck-boost converter switch out (DCDC2)                                                                                                                                                                             |  |  |

| VREF      | 1  | 0   | Filter pin for 2.25-V internal reference to ADC                                                                                                                                                                               |  |  |

| VPOS      | 44 | 0   | Positive supply output pin for panel source drivers                                                                                                                                                                           |  |  |

| VPOS_IN   | 43 | I   | Input pin for LDO1 (VPOS)                                                                                                                                                                                                     |  |  |

| WAKEUP    | 5  | I   | Wake-up pin (active high). Pull this pin high to wake up from sleep mode. IC accepts I <sup>2</sup> C commands after WAKEUP pin is pulled high but power rails remain disabled until PWRUP pin is pulled high. <sup>(3)</sup> |  |  |

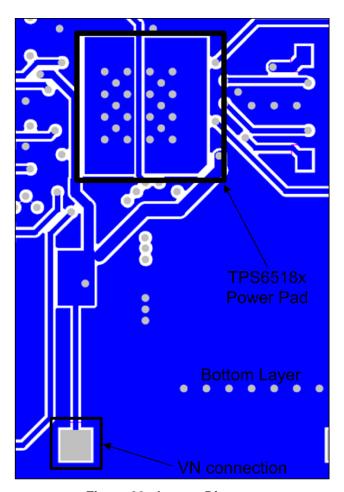

| PowerPad  | _  | _   | PowerPad, internally connected to PBKG. Connect to VN with short, wide trace. Wide copper trace will improve heat dissipation. PowerPad must not be connected to ground.                                                      |  |  |

<sup>(1)</sup> There will be 0-ns of deglitch for PWRx.

(2) There will be 62.52-µs of deglitch for VCOM\_CTRL.

(3) There will be 93.75-µs of deglitch for WAKEUP.

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                                                                                | MIN      | MAX        | UNIT |

|--------------------------------------------------------------------------------|----------|------------|------|

| Input voltage at VIN <sup>(2)</sup> , VIN_P, VIN3P3                            | -0.3     | 7          | V    |

| Ground pins to system ground                                                   | -0.3     | 0.3        | V    |

| Voltage at SDA, SCL, WAKEUP, PWRUP, VCOM_CTRL, VDDH_FB, VEE_FB, PWR_GOOD, nINT | -0.3     | 3.6        | V    |

| Voltage on VB, VB_SW, VPOS_IN, VDDH_IN                                         | -0.3     | 20         | V    |

| Voltage on VN, VEE_IN, VCOM_PWR, VNEG_IN                                       | -20      | 0.3        | V    |

| Voltage from VIN_P to VN_SW                                                    | -0.3     | 30         | V    |

| Peak output current                                                            | Internal | ly limited | mA   |

| Continuous total power dissipation                                             |          | 2          | W    |

| T <sub>J</sub> Operating junction temperature                                  | -10      | 125        | °C   |

| T <sub>A</sub> Operating ambient temperature <sup>(3)</sup>                    | -10      | 85         | °C   |

| T <sub>stg</sub> Storage temperature                                           | -65      | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions* is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                    | <u> </u>                |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

|                    | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                                                | MIN | NOM | MAX | UNIT |

|----------------|--------------------------------------------------------------------------------|-----|-----|-----|------|

|                | Input voltage at VIN, VIN_P, VIN3P3                                            | 3   | 3.7 | 6   | V    |

|                | Voltage at SDA, SCL, WAKEUP, PWRUP, VCOM_CTRL, VDDH_FB, VEE_FB, PWR_GOOD, nINT | 0   |     | 3.6 | V    |

| T <sub>A</sub> | Operating ambient temperature                                                  | -10 |     | 85  | °C   |

| $T_{J}$        | Operating junction temperature                                                 | -10 |     | 125 | °C   |

<sup>(2)</sup> All voltage values are with respect to network ground terminal.

<sup>(3)</sup> TI recommends that copper plane in proper size on board be in contact with die thermal pad to dissipate heat efficiently. Thermal pad is electrically connected to PBKG, which is supposed to be tied to the output of buck-boost converter. Thus wide copper trace in the buck-boost output will help heat dissipated efficiently.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 7.4 Thermal Information

|                      |                                              | TPS65186   |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | RGZ [VQFN] | UNIT |

|                      |                                              | 48 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 30         | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 15.6       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 6.6        | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 6.6        | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | 0.9        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 7.5 Electrical Characteristics

$V_{IN}$  = 3.7 V,  $T_A$  = -10°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                      | PARAMETER                                        | TEST CONDITIONS                    | MIN   | TYP                | MAX  | UNIT |

|----------------------|--------------------------------------------------|------------------------------------|-------|--------------------|------|------|

| INPUT VO             | LTAGE                                            |                                    | ,     |                    | '    |      |

| V <sub>IN</sub>      | Input voltage range                              |                                    | 3     | 3.7                | 6    | V    |

| $V_{UVLO}$           | Undervoltage lockout threshold                   | V <sub>IN</sub> falling            |       | 2.9                |      | V    |

| V <sub>HYS</sub>     | Undervoltage lockout hysteresis                  | V <sub>IN</sub> rising             |       | 400                |      | mV   |

| INPUT CU             | RRENT                                            |                                    |       |                    |      |      |

| IQ                   | Operating quiescent current into V <sub>IN</sub> | Device switching, no load          |       | 5.5                |      | mA   |

| I <sub>STD</sub>     | Operating quiescent current into V <sub>IN</sub> | Device in standby mode             |       | 130                |      | μA   |

| I <sub>SLEEP</sub>   | Shutdown current                                 | Device in sleep mode               |       | 3.5                | 10   | μΑ   |

| INTERNAL             | SUPPLIES                                         |                                    |       |                    |      |      |

| VI <sub>NT_LDO</sub> | Internal supply                                  |                                    |       | 2.7                |      | V    |

| C <sub>INT_LDO</sub> | Nominal output capacitor                         | Capacitor tolerance ±10%           | 1     | 4.7                |      | μF   |

| $V_{REF}$            | Internal supply                                  |                                    |       | 2.25               |      | V    |

| C <sub>REF</sub>     | Nominal output capacitor                         | Capacitor tolerance ±10%           | 3.3   | 4.7                |      | μF   |

| DCDC1 (P             | OSITIVE BOOST REGULATOR)                         |                                    |       |                    |      |      |

| V <sub>IN</sub>      | Input voltage range                              |                                    | 3     | 3.7                | 6    | V    |

| PG                   | Power good threshold                             | Fraction of nominal output voltage |       | 90%                |      |      |

| PG                   | Power good time-out                              | Not tested in production           |       | 50                 |      | ms   |

|                      | Output voltage range                             |                                    |       | 16                 |      | V    |

| V <sub>OUT</sub>     | DC set tolerance                                 |                                    | -4.5% |                    | 4.5% |      |

| I <sub>OUT</sub>     | Output current                                   |                                    |       |                    | 250  | mA   |

| R <sub>DS(ON)</sub>  | MOSFET ON-resistance                             | V <sub>IN</sub> = 3.7 V            |       | 350                |      | mΩ   |

|                      | Switch current limit                             |                                    |       | 1.5 <sup>(1)</sup> |      | Α    |

| I <sub>LIMIT</sub>   | Switch current accuracy                          |                                    | -30%  |                    | 30%  |      |

| $f_{SW}$             | Switching frequency                              |                                    |       | 1                  |      | MHz  |

| L <sub>DCDC1</sub>   | Inductor                                         |                                    |       | 2.2                |      | μΗ   |

| C <sub>DCDC1</sub>   | Nominal output capacitor                         | Capacitor tolerance ±10%           | 1     | 2 × 4.7            |      | μF   |

| ESR                  | Output capacitor ESR                             |                                    |       | 20                 |      | mΩ   |

<sup>(1)</sup> Contact TI for 1-A, 2-A, or 2.5-A option.

## **Electrical Characteristics (continued)**

$V_{IN}$  = 3.7 V,  $T_A$  = -10°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                       | PARAMETER                     | TEST CONDITIONS                                      | MIN   | TYP                | MAX    | UNIT |

|-----------------------|-------------------------------|------------------------------------------------------|-------|--------------------|--------|------|

| DCDC2 (IN             | VERTING BUCK-BOOST REGULA     | ATOR)                                                |       |                    |        |      |

| V <sub>IN</sub>       | Input voltage range           |                                                      | 3     | 3.7                | 6      | V    |

| PG                    | Power good threshold          | Fraction of nominal output voltage                   |       | 90%                |        |      |

| PG                    | Power good time-out           | Not tested in production                             |       | 50                 |        | ms   |

| V                     | Output voltage range          |                                                      |       | -16                |        | V    |

| V <sub>OUT</sub>      | DC set tolerance              |                                                      | -4.5% |                    | 4.5%   |      |

| I <sub>OUT</sub>      | Output current                |                                                      |       |                    | 250    | mA   |

| R <sub>DS(ON)</sub>   | MOSFET ON-resistance          | V <sub>IN</sub> = 3.7 V                              |       | 350                |        | mΩ   |

|                       | Switch current limit          |                                                      |       | 1.5 <sup>(1)</sup> |        | Α    |

| I <sub>LIMIT</sub>    | Switch current accuracy       |                                                      | -30%  |                    | 30%    |      |

| L <sub>DCDC1</sub>    | Inductor                      |                                                      |       | 4.7                |        | μΗ   |

| C <sub>DCDC1</sub>    | Nominal output capacitor      | Capacitor tolerance ±10%                             | 1     | 3x4.7              |        | μF   |

| ESR                   | Capacitor ESR                 |                                                      |       | 20                 |        | mΩ   |

| LDO1 (VPC             | OS)                           |                                                      |       |                    |        |      |

| V <sub>POS_IN</sub>   | Input voltage range           |                                                      | 15.2  | 16                 | 16.8   | V    |

| DO.                   | Power good threshold          | Fraction of nominal output voltage                   |       | 90%                |        |      |

| PG                    | Power good time-out           | Not tested in production                             |       | 50                 |        | ms   |

| V <sub>SET</sub>      | Output voltage set value      | V <sub>IN</sub> = 16 V,<br>VSET[2:0] = 0x3h to 0x6h  | 14.25 | 15                 | 15     | V    |

| V <sub>INTERVAL</sub> | Output voltage set resolution | V <sub>IN</sub> = 16 V                               |       | 250                |        | mV   |

| V <sub>OUTTOL</sub>   | Output tolerance              | V <sub>SET</sub> = 15 V, I <sub>LOAD</sub> = 20 mA   | -1%   |                    | 1%     |      |

| V <sub>DROPOUT</sub>  | Dropout voltage               | I <sub>LOAD</sub> = 120 mA                           |       |                    | 250    | mV   |

| V <sub>LOADREG</sub>  | Load regulation – DC          | I <sub>LOAD</sub> = 10% to 90%                       |       |                    | 1%     |      |

| I <sub>LOAD</sub>     | Load current range            |                                                      |       |                    | 120    | mA   |

| I <sub>LIMIT</sub>    | Output current limit          |                                                      | 120   |                    |        | mA   |

| C <sub>LDO1</sub>     | Nominal output capacitor      | Capacitor tolerance ±10%                             | 1     | 4.7                |        | μF   |

| LDO2 (VNI             | EG)                           |                                                      |       |                    |        |      |

| V <sub>NEG_IN</sub>   | Input voltage range           |                                                      | 16.8  | 16                 | -15.2  | V    |

| DC                    | Power good threshold          | Fraction of nominal output voltage                   |       | 90%                |        |      |

| PG                    | Power good time-out           | Not tested in production                             |       | 50                 |        | ms   |

| V <sub>SET</sub>      | Output voltage set value      | $V_{IN} = -16 \text{ V}$<br>VSET[2:0] = 0x3h to 0x6h | -15   | -15                | -14.25 | V    |

| V <sub>INTERVAL</sub> | Output voltage set resolution | V <sub>IN</sub> = -16 V                              |       | 250                |        | mV   |

| V <sub>OUTTOL</sub>   | Output tolerance              | V <sub>SET</sub> = -15 V, I <sub>LOAD</sub> = -20 mA | -1%   |                    | 1%     |      |

| V <sub>DROPOUT</sub>  | Dropout voltage               | I <sub>LOAD</sub> = 120 mA                           |       |                    | 250    | mV   |

| V <sub>LOADREG</sub>  | Load regulation – DC          | $I_{LOAD}$ = 10% to 90% of $I_{LOAD,MAX}$            |       |                    | 1%     |      |

| I <sub>LOAD</sub>     | Load current range            |                                                      |       |                    | 120    | mA   |

| I <sub>LIMIT</sub>    | Output current limit          |                                                      | 120   |                    |        | mA   |

| C <sub>LDO2</sub>     | Nominal output capacitor      | Capacitor tolerance ±10%                             | 1     | 4.7                |        | μF   |

## **Electrical Characteristics (continued)**

$V_{IN}$  = 3.7 V,  $T_A$  = -10°C to 85°C, Typical values are at  $T_A$  = 25°C (unless otherwise noted)

|                                                                                           | PARAMETER                        | TEST CONDITIONS                                                                                           | MIN   | TYP    | MAX   | UNIT      |

|-------------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------|-------|--------|-------|-----------|

| LD01 (POS                                                                                 | 6) AND LDO2 (VNEG) TRACKING      |                                                                                                           |       |        |       |           |

| $V_{DIFF}$                                                                                | Difference between VPOS and VNEG | $V_{SET} = \pm 15 \text{ V},$<br>$I_{LOAD} = \pm 20 \text{ mA}, 0^{\circ}\text{C to } 60^{\circ}\text{C}$ | -50   |        | 50    | mV        |

| VCOM DR                                                                                   | VER                              |                                                                                                           | ·     |        | ·     |           |

| I <sub>VCOM</sub>                                                                         | Drive current                    |                                                                                                           |       | 15     |       | mA        |

|                                                                                           | Allowed operating range          | Outside this range VCOM is shut down and VCOMF interrupt is set                                           | -5.5  |        | 1     | ٧         |

|                                                                                           | A                                | VCOM[8:0] = 0x07Dh<br>(-1.25 V), V <sub>IN</sub> = 3.4 V to 4.2 V, no load                                | -0.8% |        | 0.8%  |           |

| $V_{\text{COM}}$                                                                          | Accuracy                         | VCOM[8:0] = 0x07Dh<br>(-1.25 V), V <sub>IN</sub> = 3 V to 6 V, no load                                    | -1.5% |        | 1.5%  |           |

|                                                                                           | Output voltage range             |                                                                                                           | -5.11 |        | 0     | V         |

|                                                                                           | Resolution                       | 1LSB                                                                                                      |       | 10     |       | mV        |

| ROUT RIN CVCOM CP1 (VDDH) VDDH_IN PG VDDH_OUT LOAD TSW CD CCP2 (VEE) N                    | Max number of EEPROM writes      | V <sub>COM</sub> calibration                                                                              |       |        | 100   |           |

| R <sub>OUT</sub>                                                                          | Output impedance                 | VCOM_CTRL = high, Hi-Z = 0                                                                                |       | 5      |       | Ω         |

| R <sub>IN</sub>                                                                           | Input impedance, HiZ state       | HiZ = 1                                                                                                   | 150   |        |       | $M\Omega$ |

| C <sub>VCOM</sub>                                                                         | Nominal output capacitor         | Capacitor tolerance ±10%                                                                                  | 3.3   | 4.7    |       | μF        |

| CP1 (VDDI                                                                                 | H) CHARGE PUMP                   |                                                                                                           | •     |        |       |           |

| $V_{DDH_IN}$                                                                              | Input voltage range              |                                                                                                           | 15.2  | 16     | 16.8  | V         |

| C <sub>VCOM</sub> CP1 (VDDH) V <sub>DDH_IN</sub> PG V <sub>FB</sub> V <sub>DDH_OUT</sub>  | Power good threshold             | Fraction of nominal output voltage                                                                        |       | 90%    |       |           |

|                                                                                           | Power good time-out              | Not tested in production                                                                                  |       | 50     |       | ms        |

| PG<br>V <sub>FB</sub>                                                                     | Feedback voltage                 |                                                                                                           |       | 0.998  |       | V         |

| V <sub>FB</sub>                                                                           | Accuracy                         | I <sub>LOAD</sub> = 2 mA                                                                                  | -2%   |        | 2%    |           |

| V <sub>DDH_OUT</sub>                                                                      | Output voltage range             | V <sub>SET</sub> = 22 V, I <sub>LOAD</sub> = 2 mA                                                         | 21    | 22     | 23    | V         |

| _                                                                                         | Load current range               |                                                                                                           |       |        | 10    | mA        |

| f <sub>SW</sub>                                                                           | Switching frequency              |                                                                                                           |       | 560    |       | kHz       |

| C <sub>D</sub>                                                                            | Driver capacitor                 |                                                                                                           |       | 10     |       | nF        |

| Co                                                                                        | Output capacitor                 |                                                                                                           | 1     | 2.2    |       | μF        |

| CP2 (VEE)                                                                                 | NEGATIVE CHARGE PUMP             |                                                                                                           | *     |        |       |           |

| V <sub>EE_IN</sub>                                                                        | Input voltage range              |                                                                                                           | 16.8  | -16    | -15.2 | V         |

|                                                                                           | Power good threshold             | Fraction of nominal output voltage                                                                        |       | 90%    |       |           |

| PG                                                                                        | Power good time-out              | Not tested in production                                                                                  |       | 50     |       | ms        |

|                                                                                           | Feedback voltage                 |                                                                                                           |       | -0.994 |       | V         |

| CVCOM CP1 (VDDH) VDDH_IN PG VFB VDDH_OUT ILOAD CD CP2 (VEE) N VEE_IN PG VFB VEE_OUT ILOAD | Accuracy                         | I <sub>LOAD</sub> = 2 mA                                                                                  | -2%   |        | 2%    |           |

| V <sub>EE_OUT</sub>                                                                       | Output voltage range             | $V_{SET} = -20 \text{ V}, I_{LOAD} = 3 \text{ mA}$                                                        | -21   | -20    | -19   | V         |

|                                                                                           | Load current range               |                                                                                                           |       |        | 12    | mA        |

| f <sub>SW</sub>                                                                           | Switching frequency              |                                                                                                           |       | 560    |       | kHz       |

| C <sub>D</sub>                                                                            | Driver capacitor                 |                                                                                                           |       | 10     |       | nF        |

| Co                                                                                        | Nominal output capacitor         | Capacitor tolerance ±10%                                                                                  | 1     | 2.2    |       | μF        |

## **Electrical Characteristics (continued)**

$V_{IN} = 3.7 \text{ V}$ ,  $T_A = -10^{\circ}\text{C}$  to 85°C, Typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER             |                                    | TEST CONDITIONS                                                       | MIN  | TYP     | MAX                  | UNIT |

|-----------------------|------------------------------------|-----------------------------------------------------------------------|------|---------|----------------------|------|

| VIN3P3 TO             | V3P3 SWITCH                        | 1                                                                     |      |         |                      |      |

| D                     | MOSEET ON registence               | VIN3P3 = 3.3 V, I <sub>D</sub> = 10 mA<br>Over full temperature range |      | 10.5    |                      | 0    |

| R <sub>DS(ON)</sub>   | MOSFET ON-resistance               | VIN3P3 = 2.7 V, I <sub>D</sub> = 10 mA<br>Over full temperature range |      | 12.3    |                      | Ω    |

| $R_{\text{DIS}}$      | Discharge impedance to ground      | V3P3EN = 0                                                            | 800  | 1000    | 1200                 | Ω    |

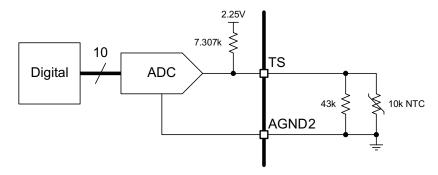

| THERMIST              | OR MONITOR <sup>(2)</sup>          |                                                                       |      |         |                      |      |

| A <sub>TMS</sub>      | Temperature to voltage ratio       | Not tested in production                                              |      | -0.0161 |                      | V/°C |

| Offset <sub>TMS</sub> | Offset                             | Temperature = 0°C                                                     |      | 1.575   |                      | V    |

| V <sub>TMS_HOT</sub>  | Temp hot trip voltage (T = 50°C)   | TEMP_HOT_SET = 0x8C                                                   |      | 0.768   |                      | V    |

| V <sub>TMS_COOL</sub> | Temp hot escape voltage (T = 45°C) | TEMP_COOL_SET = 0x82                                                  |      | 0.845   |                      | V    |

| V <sub>TMS_MAX</sub>  | Maximum input level                |                                                                       |      | 2.25    |                      | V    |

| R <sub>NTC_PU</sub>   | Internal pullup resistor           |                                                                       |      | 7.307   |                      | kΩ   |

| R <sub>LINEAR</sub>   | External linearization resistor    |                                                                       |      | 43      |                      | kΩ   |

| ADC <sub>RES</sub>    | ADC resolution                     | Not tested in production, 1 bit                                       |      | 16.1    |                      | mV   |

| ADC <sub>DEL</sub>    | ADC conversion time                | Not tested in production                                              |      | 19      |                      | μs   |

| TMST <sub>TOL</sub>   | Accuracy                           | Not tested in production                                              | -1   |         | 1                    | LSB  |

| LOGIC LEV             | /ELS AND TIMING CHARTERISTICS (    | SCL, SDA, nINT, PWR_GOOD, PWRUP                                       | )    |         |                      |      |

| V <sub>OL</sub>       | Output low threshold level         | I <sub>O</sub> = 3 mA, sink current<br>(SDA, nINT, PWR_GOOD)          |      |         | 0.4                  | V    |

| V <sub>IL</sub>       | Input low threshold level          |                                                                       |      |         | 0.4                  | V    |

| V <sub>IH</sub>       | Input high threshold level         |                                                                       | 1.2  |         |                      | V    |

| I <sub>(bias)</sub>   | Input bias current                 | V <sub>IO</sub> = 1.8 V                                               |      |         | 1                    | μA   |

|                       | Deglitch time, WAKEUP pin          | Not tested in production                                              |      | 500     |                      |      |

| t <sub>deglitch</sub> | Deglitch time, PWRUP pin           | Not tested in production                                              |      | 400     |                      | μs   |

| f <sub>SCL</sub>      | SCL clock frequency                |                                                                       |      |         | 400                  | kHz  |

|                       | I <sup>2</sup> C slave address     | 7-bit address                                                         |      | 0       | × 48h <sup>(3)</sup> |      |

| OSCILLAT              | OR                                 |                                                                       | 11.  |         |                      |      |

| f <sub>OSC</sub>      | Oscillator frequency               |                                                                       |      | 9       |                      | MHz  |

|                       | Frequency accuracy                 | $T_A = -40$ °C to 85°C                                                | -10% |         | 10%                  |      |

| THERMAL               | SHUTDOWN                           |                                                                       | !    |         |                      |      |

| T <sub>SHTDWN</sub>   | Thermal trip point                 |                                                                       |      | 150     |                      | °C   |

|                       | Thermal hysteresis                 |                                                                       |      | 20      |                      | °C   |

<sup>(2) 10-</sup>kΩ Murata NCP18XH103F03RB thermistor (1%) in parallel with a linearization resistor (43 kΩ, 1%) are used at TS pin for panel temperature measurement.

<sup>(3)</sup> Contact TI for alternate address of  $0 \times 68h$ .

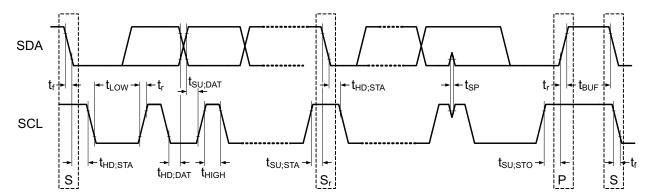

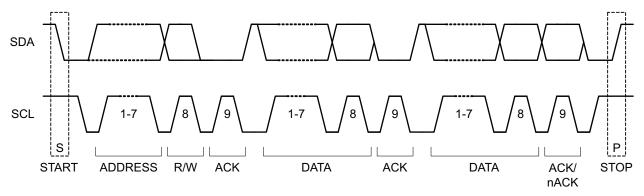

## 7.6 Timing Requirements: Data Transmission

$V_{BAT}$  = 3.6 V ±5%,  $T_A$  = 25°C,  $C_L$  = 100 pF (unless otherwise noted)

|                                       |                                                  |               | MIN | NOM | MAX  | UNIT |  |

|---------------------------------------|--------------------------------------------------|---------------|-----|-----|------|------|--|

| f <sub>(SCL)</sub>                    | Serial clock frequency                           |               | 100 |     | 400  | kHz  |  |

|                                       | Hold time (repeated) START condition. After this | SCL = 100 kHz | 4   |     |      | μs   |  |

| t <sub>HD;STA</sub>                   | period, the first clock pulse is generated.      | SCL = 400 kHz | 600 |     |      | ns   |  |

|                                       | LOW period of the SCL clock                      |               | 4.7 |     |      |      |  |

| $t_{LOW}$                             | LOW period of the SCL clock                      | SCL = 400 kHz | 1.3 |     |      | μs   |  |

|                                       | LUCII povied of the CCI plant                    | SCL = 100 kHz | 4   |     |      | μs   |  |

| t <sub>HIGH</sub>                     | HIGH period of the SCL clock                     | SCL = 400 kHz | 600 |     |      | ns   |  |

|                                       | Catura time for a remoted CTART and ities        | SCL = 100 kHz | 4.7 |     |      | μs   |  |

| t <sub>SU;STA</sub>                   | Setup time for a repeated START condition        | SCL = 400 kHz | 600 |     |      | ns   |  |

| t <sub>HD;DAT</sub> Data hold time    | Date hald time                                   | SCL = 100 kHz | 0   |     | 3.45 | μs   |  |

|                                       | Data noid time                                   | SCL = 400 kHz | 0   |     | 900  | ns   |  |

| , 5                                   | Data setup time                                  | SCL = 100 kHz | 250 |     |      |      |  |

| t <sub>SU;DAT</sub>                   |                                                  | SCL = 400 kHz | 100 |     |      | ns   |  |

|                                       | Dies tiese of both CDA and CCI signals           | SCL = 100 kHz |     |     | 1000 |      |  |

| t <sub>r</sub>                        | Rise time of both SDA and SCL signals            | SCL = 400 kHz |     |     | 300  | ns   |  |

|                                       | Fall time of hoth CDA and CCI simple             | SCL = 100 kHz |     |     | 300  |      |  |

| t <sub>f</sub>                        | Fall time of both SDA and SCL signals            | SCL = 400 kHz |     |     | 300  | ns   |  |

|                                       | Catura times for CTOD and dition                 | SCL = 100 kHz | 4   |     |      | μs   |  |

| t <sub>SU;STO</sub>                   | Setup time for STOP condition                    | SCL = 400 kHz | 600 |     |      | ns   |  |

|                                       | Due Free Time Between Other and Other Oracliffe  | SCL = 100 kHz | 4.7 |     |      |      |  |

| t <sub>BUF</sub> Bus Free Time Betwee | Bus Free Time Between Stop and Start Condition   | SCL = 400 kHz | 1.3 |     |      | μs   |  |

| . Pulse w                             | Pulse width of spikes that must be suppressed by | SCL = 100 kHz | n/a |     | n/a  |      |  |

| t <sub>SP</sub>                       | the input filter                                 | SCL = 400 kHz | 0   |     | 50   | ns   |  |

| ^                                     | Constitute lead for each has line                | SCL = 100 kHz |     |     | 400  |      |  |

| C <sub>b</sub>                        | Capacitive load for each bus line                | SCL = 400 kHz |     |     | 400  | pF   |  |

Figure 1. I<sup>2</sup>C Data Transmission Timing

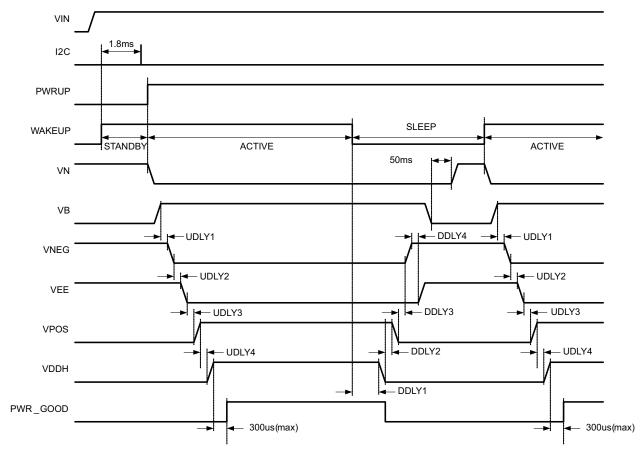

Minimum delay time between WAKEUP rising edge and IC ready to accept I<sup>2</sup>C transaction.

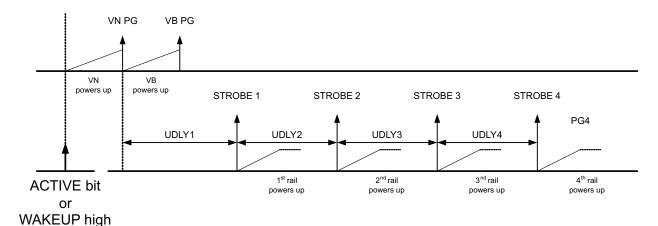

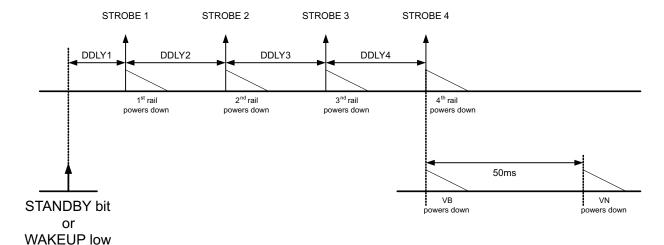

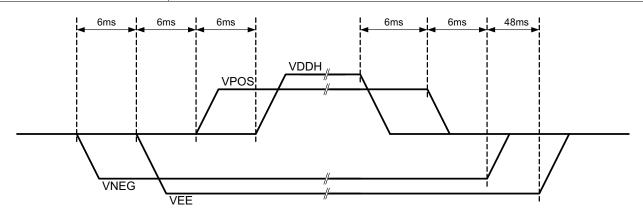

In this example, the first power-up sequence is started by pulling the PWRUP pin high (rising edge). Power-down is initiated by pulling the WAKEUP pin low (device enters sleep mode). The second power-up sequence is initiated by pulling the WAKEUP pin high while the PWRUP pin is also high (power up from sleep to active).

Figure 2. Power-Up and Power-Down Timing Diagram

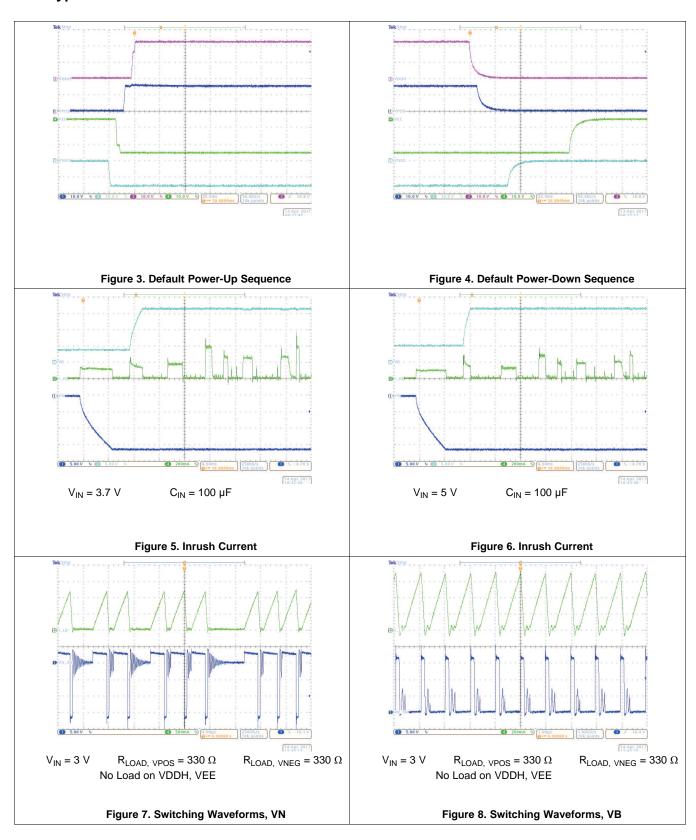

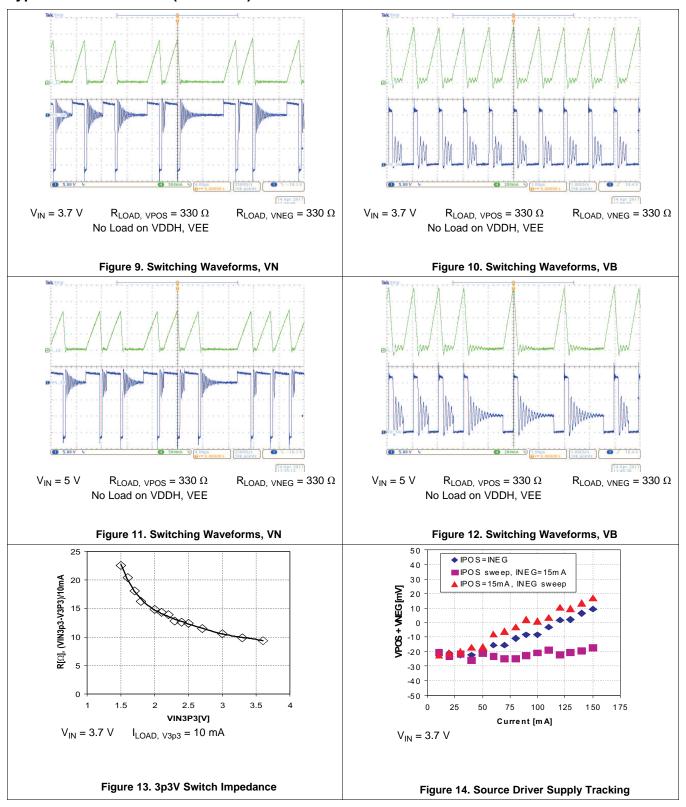

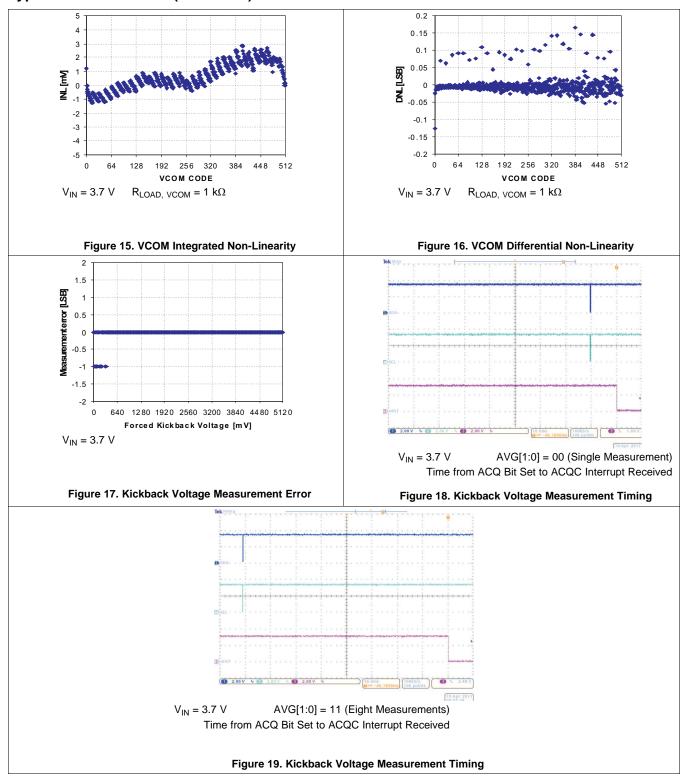

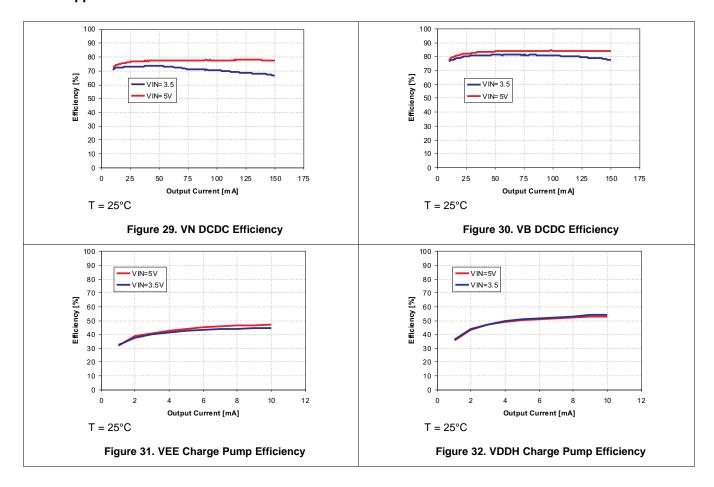

### 7.7 Typical Characteristics

### **Typical Characteristics (continued)**

### **Typical Characteristics (continued)**

## 8 Detailed Description

#### 8.1 Overview

The TPS65186 device provides two adjustable LDOs, inverting buck-boost converter, boost converter, thermistor monitoring, and flexible power-up and power-down sequencing. The system can be supplied by a regulated input voltage ranging from 3 V to 6 V. The device is characterized across a –10°C to 85°C temperature range, best suited for personal electronic applications.

The I<sup>2</sup>C interface provides comprehensive features for using the TPS65186. All rails can be enabled or disabled. Power-up and power-down sequences can also be programmed through the I<sup>2</sup>C interface, as well as thermistor configuration and interrupt configuration. Voltage adjustment can also be controlled by the I<sup>2</sup>C interface.

The adjustable LDOs can supply up to 120 mA of current. The default output voltages for each LDO can be adjusted through the I<sup>2</sup>C interface. LDO1 (VPOS) and LDO2 (VNEG) track each other in a way that they are of opposite sign but same magnitude. The sum of VLDO1 and VLOD2 is guaranteed to be less than 50 mV.

There are two charge pumps: VDDH and VEE 10 mA and 12 mA respectively. These charge pumps boost the DC-DC boost converters ±16-V rails to provide a gate channel supply.

The power good functionality is open-drain output, if any of the four power rails (CP1, CP2, LDO1, LDO2) are not in regulation, encounters a fault, or is disabled the pin is pulled low. PWR\_GOOD remains low if one of the rails is not enabled by the host and only after all rails are in regulation PWR\_GOOD is released to Hi-Z state (pulled up by external resistor).

The TPS65186 provides circuitry to bias and measure an external NTC to monitor the display panel temperature in a range from  $-10^{\circ}$ C to  $85^{\circ}$ C with and accuracy of  $\pm 1^{\circ}$ C from  $0^{\circ}$ C to  $50^{\circ}$ C. Temperature measurement are triggered by the controlling host and the last temperature reading is always stored in the TMST\_VALUE register. Interrupts are issued when the temperature exceeds the programmable HOT, or drops below the programmable COLD threshold, or when the temperature has changed by more than a user-defined threshold from the baseline value.

This device is offered in a 48-Pin, 0.5-mm Pitch, 7 mm × 7 mm × 0.9 mm (VQFN) RGZ package.

### 8.2 Functional Block Diagram

#### 8.3 Feature Description

#### 8.3.1 Wake-Up and Power-Up Sequencing

The power-up and power-down order and timing is defined by user register settings. The default settings support the E Ink Vizplex panel and typically do not need to be changed.

In SLEEP mode the TPS65186 is completely turned off, the I<sup>2</sup>C registers are reset, and the device does not accept any I<sup>2</sup>C transaction. Pull the WAKEUP pin high with the PWRUP pin low and the device enters STANDBY mode that enables the I<sup>2</sup>C interface. Write to the UPSEQ0 register to define the order in which the output rails are enabled at power-up and to the UPSEQ1 registers to define the power-up delays between rails. Finally, set the ACTIVE bit in the ENABLE register to 1 to execute the power-up sequence and bring up all power rails. Alternatively, pull the PWRUP pin high (rising edge).

After the ACTIVE bit has been set, the negative boost converter (VN) is powered up first, followed by the positive boost (VB). The positive boost enable is gated by the internal power-good signal of the negative boost. Once VB is in regulation, it issues an internal power-good signal and after delay time UDLY1 has expired, STROBE1 is issued. The rail assigned to STROBE1 will power up next and after its power-good signal has been asserted and delay time UDLY2 has expired, STROBE2 is issued. The sequence continues until STROBE4 has occurred and the last rail has been enabled.

To power down the device, set the STANDBY bit of the ENABLE register to 1 or pull the PWRUP pin low (falling edge) and the TPS65186 will power down in the order defined by DWNSEQx registers. The delay times DDLY2, DDLY3, and DDLY4 are weighted by a factor of DFCTR which allows the user to space out the power down of the rails to avoid crossing during discharge. DFCTR is located in register DWNSEQ1. The positive boost (VB) is shut down together with the last rail at STROBE4. However, the negative boost (VN) remains up and running for another 50 ms. Then VN is powered down and the device enters STANDBY or SLEEP mode, depending on the WAKEUP pin.

If either the ACTIVE bit is set or the PWRUP pin is pulled high while the device is powering down, the power-down sequence (STROBE1-4) is completed first, followed by a power-up sequence. VB and VN may or may not be powered down and depending on the relative timing of STROBE4 to the new power-up event.

During power-up, if the STANDBY bit is set or the PWRUP pin is pulled low, the power-up sequence is aborted and the power-down sequence starts immediately.

#### 8.3.2 Dependencies Between Rails

Charge pumps, LDOs, and VCOM driver are dependent on the positive and inverting buck-boost converters and several dependencies exist that affect the power-up sequencing. These dependencies are the following:

- Inverting buck-boost (DCDC2) must be in regulation before positive boost (DCDC1) can be enabled. Internally, DCDC1 enable is gated by DCDC2 power good.

- Positive boost (DCDC1) must be in regulation before LDO2 (VNEG) can be enabled. Internally LDO2 enable

is gated DCDC1 power good.

- Positive boost (DCDC1) must be in regulation before VCOM can be enabled. Internally VCOM enable is gated by DCDC1 power good.

- Positive boost (DCDC1) must be in regulation before negative charge pump (CP2) can be enabled. Internally CP2 enable is gated by DCDC1 power good.

- Positive boost (DCDC1) must be in regulation before positive charge pump (CP1) can be enabled. Internally CP1 enable is gated by DCDC1 power good.

- LDO2 must be in regulation before LDO1 can be enabled. Internally LDO1 enable is gated by LDO2 power good.

TOP: Power-up sequence is defined by assigning strobes to individual rails. STROBE1 is the first strobe to occur after ACTIVE bit is set and STROBE4 is the last event in the sequence. Strobes are assigned to rails in UPSEQ0 register and delays between STROBES are defined in UPSEQ1 register.

BOTTOM: Power-down sequence is independent of power-up sequence. Strobes and delay times for power down sequence are set in DWNSEQ0 and DWNSEQ1 register.

Figure 20. Power-Up and Power-Down Sequence

#### 8.3.3 Soft Start

TPS65186 supports soft start for all rails, that is, inrush current is limited during startup of DCDC1, DCDC2, LDO1, LDO2, CP1, and CP2. If DCDC1 or DCDC2 are unable to reach power-good status within 50 ms, the corresponding UV flag is set in the interrupt registers, the interrupt pin is pulled low, and the device enters STANDBY mode. LDO1, LDO2, positive and negative charge pumps also have a 50-ms power-good time-out limit. If either rail is unable to power up within 50 ms after it has been enabled, the corresponding UV flag is set and the interrupt pin is pulled low. However, the device will remain in ACTIVE mode in this case.

#### 8.3.4 VPOS/VNEG Supply Tracking

LDO1 (VPOS) and LDO2 (VNEG) track each other in a way that they are of opposite sign but same magnitude. The sum of VLDO1 and VLOD2 is guaranteed to be less than 50 mV.

#### 8.3.5 V3P3 Power Switch

The integrated power switch is used to cut the 3.3-V supply to the EPD panel and is controlled through the V3P3\_EN pin of the ENABLE register. In SLEEP mode the switch is automatically turned off and its output is discharged to ground. The default power-up state is OFF. To turn the switch ON, set the V3P3\_ENbit to 1.

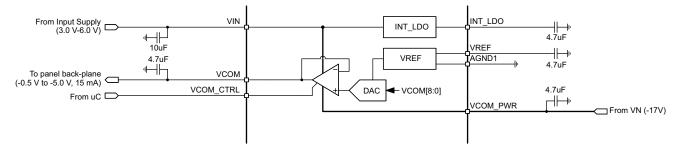

#### 8.3.6 VCOM Adjustment

VCOM is the output of a power-amplifier with an output voltage range of 0 V to -5.11 V, adjustable in 10-mV steps. In a typical application VCOM is connected to the VCOM terminal of the EPD panel and the amplifier is controlled through the VCOM\_CTRL pin. With VCOM\_CTRL high, the amplifier drives the VCOM pin to the voltage specified by the VCOM1 and VCOM2 register.

For ease of design, the VCOM\_CTRL pin may also be tied to the battery or IO supply. In this case, VCOM is enabled with STROBE4 during the power-up sequence and disabled on STROBE1 of the power-down sequence. Therefore VCOM is the last rail to be enabled and the first to be disabled.

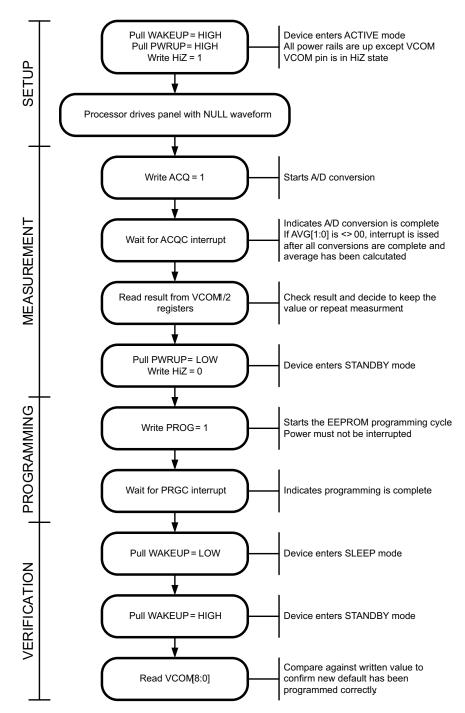

#### 8.3.6.1 Kick-Back Voltage Measurement

TPS65186 can perform a voltage measurement on the VCOM pin to deter87/mine the kick-back voltage of the panel. This allows in-system calibration of VCOM. To perform a kick-back voltage measurement, follow these steps:

- Pull the WAKEUP pin and the PWRUP pin high to enable all output rails.

- Set the Hi-Z bit in the VCOM2 register. This puts the VCOM pin in a high-impedance state.

- Drive the panel with the Null waveform. Refer to E-lnk specification for detail.

- Set the ACQ bit in the VCOM2 register to 1. This starts the measurement routine.

- When the measurement is complete, the ACQC (Acquisition Complete) bit in the INT1 register is set and the nINT pin is pulled low.

- The measurement result is stored in the VCOM[8:0] bits of the VCOM1 and VCOM2 register.

The measurement result is not automatically programmed into nonvolatile memory. Changing the power-up default is described in *Storing the VCOM Power-Up Default Value in Memory*.

#### 8.3.6.2 Storing the VCOM Power-Up Default Value in Memory

The power-up default value of VCOM can be user-set and programmed into nonvolatile memory. To do so, write the default value to the VCOM[8:0] bits of the VCOM1 and VCOM2 register, then set the PROG bit in VCOM2 register to 1. First, all power rails are shut down, then the VCOM[8:0] value is committed to nonvolatile memory such that it becomes the new power-up default. Once programming is complete, the PRGC bit in the INT1 register is set and the nINT pin is pulled low. To verify that the new value has been saved properly, first write the VCOM[8:0] bits to 0x000h, then pull the WAKEUP pin low. After the WAKEUP pin is pulled back high, read the VCOM[8:0] bits to verify that the new default value is correct.

Figure 21. Block Diagram of VCOM Circuit

Figure 22. VCOM Calibration Flow

#### 8.3.7 Fault Handling and Recovery

The TPS65186 monitors input/output voltages and die temperature; the device will take action if operating conditions are outside normal limits when the following are encountered:

- Thermal Shutdown (TSD)

- Positive Boost Undervoltage (VB UV)

- Inverting Buck-Boost Undervoltage (VN\_UV)

- Input Undervoltage Lockout (UVLO)

The TPS65186 shuts down all power rails and enters STANDBY mode. Shutdown follows the order defined by DWNSEQx registers. The exception is VCOM fault witch leads to immediate shutdown of all rails. Once a fault is detected, the PWR\_GOOD and nINT pins are pulled low and the corresponding interrupt bit is set in the interrupt register. Power rails cannot be re-enabled unless the interrupt bits have been cleared by reading the INT1 and INT2 register. Alternatively, toggling the WAKEUP pin also resets the interrupt bits. As the PWRUP input is edge sensitive, the host must toggle the PWRUP pin to re-enable the rails through GPIO control, that is, it must bring the PWRUP pin low before asserting it again. Alternatively rails can be re-enabled through the I<sup>2</sup>C interface.

Whenever the TPS65186 encounters undervoltage on VNEG (VNEG\_UV), VPOS (VPOS\_UV), VEE (VEE\_UV), or VDDH (VDDH\_UV), rails are not shut down but the PWR\_GOOD and nINT is pulled low with the corresponding interrupt bit set. The device remains in ACTIVE mode and recovers automatically once the fault has been removed.

#### 8.3.8 Power Good Pin

The power good pin (PWR\_GOOD) is an open-drain output that is pulled high (by an external pullup resistor) when all four power rails (CP1, CP2, LDO1, LDO2) are in regulation and is pulled low if any of the rails encounters a fault or is disabled. PWR\_GOOD remains low if one of the rails is not enabled by the host and only after all rails are in regulation PWR GOOD is released to Hi-Z state (pulled up by external resistor).

#### 8.3.9 Interrupt Pin

The interrupt pin (nINT) is an open-drain output that is pulled low whenever one or more of the INT1 or INT2 bits are set. The nINT pin is released (returns to Hi-Z state) and fault bits are cleared once the register with the set bit has been read by the host. If the fault persists, the nINT pin will be pulled low again after a maximum of 32 µs.

Interrupt events can be masked by re-setting the corresponding enable bit in the INT\_EN1 and INT\_EN2 register, that is, the user can determine which events cause the nINT pin to be pulled low. The status of the enable bits affects the nINT pin only and has no effect on any of the protection and monitoring circuits or the INT1/INT2 bits themselves.

Persisting faults such as thermal shutdown can cause the nINT pin to be pulled low for an extended period of time which can keep the host in a loop trying to resolve the interrupt. If this behavior is not desired, set the corresponding mask bit after receiving the interrupt and keep polling the INT1/INT2 register to see when the fault condition has disappeared. After the fault is resolved, unmask the interrupt bit again.

#### 8.3.10 Panel Temperature Monitoring

The TPS65186 provides circuitry to bias and measure an external Negative Temperature Coefficient Resistor (NTC) to monitor the display panel temperature in a range from –10°C to 85°C with and accuracy of ±1°C from 0°C to 50°C. Temperature measurement must be triggered by the controlling host and the last temperature reading is always stored in the TMST\_VALUE register. Interrupts are issued when the temperature exceeds the programmable HOT, or drops below the programmable COLD threshold, or when the temperature has changed by more than a user-defined threshold from the baseline value. Details are explained under *Hot, Cold, and Temperature-Change Interrupts*.

#### 8.3.10.1 NTC Bias Circuit

Figure 23 shows the block diagram of the NTC bias and measurement circuit. The NTC is biased from an internally generated 2.25-V reference voltage through an integrated 7.307-k $\Omega$  bias resistor. A 43-k $\Omega$  resistor is connected parallel to the NTC to linearize the temperature response curve. The circuit is designed to work with a nominal 10-k $\Omega$  NTC and achieves accuracy of ±1°C from 0°C to 50°C. The voltage drop across the NTC is digitized by a 10-bit SAR ADC and translated into an 8-bit two's complement by digital per Table 1.

**Table 1. ADC Output Value vs Temperature**

| TEMPERATURE | TMST_VALUE[7:0] |  |  |  |

|-------------|-----------------|--|--|--|

| < -10°C     | 1111 0110       |  |  |  |

| -10°C       | 1111 0110       |  |  |  |

| −9°C        | 1111 0111       |  |  |  |

|             |                 |  |  |  |

| -2°C        | 1111 1110       |  |  |  |

| −1°C        | 1111 1111       |  |  |  |

| 0°C         | 0000 0000       |  |  |  |

| 1°C         | 0000 0001       |  |  |  |

| 2°C         | 0000 0010       |  |  |  |

|             |                 |  |  |  |

| 25°C        | 0001 1001       |  |  |  |

|             |                 |  |  |  |

| 85°C        | 0101 0101       |  |  |  |

| > 85°C      | 0101 0101       |  |  |  |

Figure 23. NTC Bias and Measurement Circuit

A temperature measurement is triggered by setting the READ\_THERM bit of the TMST1 register to 1.During the A/D conversion the CONV\_END bit of the TMST1 register reads 0, otherwise it reads 1. At the end of the A/D conversion the EOC bit in the INT2 register is set and the temperature value is available in the TMST\_VALUE register.

#### 8.3.10.2 Hot, Cold, and Temperature-Change Interrupts

Each temperature acquisition is compared against the programmable TMST\_HOT and TMST\_COLD thresholds and to the baseline temperature, to determine if the display is within allowed operating temperature range and if the temperature has changed by more than a user-defined threshold since the last update. The first temperature reading after the WAKEUP pin has been pulled high automatically becomes the baseline temperature. Any subsequent reading is compared against the baseline temperature. If the difference is equal or greater than the threshold value, an interrupt is issued (DTX bit in register INT1 is set to 1) and the latest value becomes the new baseline. If the difference is less than the threshold value, no action is taken. The threshold value is defined by DT[1:0] bits in the TMST1 register and has a default value of ±2°C. In summary:

- When the temperature is equal or less than the TMST\_COLD[3:0] threshold, the TMST\_COLD interrupt bit of the INT1 register is set, and the nINT pin is pulled low.

- When the temperature is greater than TMST\_COLD but lower then TMST\_HOT, no action is taken.

- When the temperature is equal or greater than the TMST\_HOT[3:0] threshold, the TMST\_HOT interrupt bit of the INT1 register is set, and the nINT pin is pulled low.

- If the last temperature is different from the baseline temperature by ±2°C (default) or more, the DTX interrupt bit of the INT1 register is set. The latest temperature becomes the new baseline temperature. By default the DTX interrupt is disabled, that is, the nINT pin is not pulled low unless the DTX\_EN bit was previously set high.

- If the last temperature change is less than ±2°C (default), no action is taken.

#### 8.3.10.3 Typical Application of the Temperature Monitor

In a typical application the temperature monitor and interrupts are used in the following manner:

- After the WAKEUP pin has been pulled high, the Application Processor (AP) writes 0x80h to the TMST1 register (address 0x0Dh). This starts the temperature measurement.

- The AP waits for the EOC interrupt. Alternatively the AP can poll the CONV\_END bit in register TMST1. This will notify the AP that the A/D conversion is complete and the new temperature reading is available in the TMST\_VALUE register (address (0x00h).

- The AP reads the temperature value from the TMST\_VALUE register (address (0x00h).

- If the temperature changes by ±2°C (default) or more from the first reading, the processor is notified by the DTX interrupt. The A/P may or may not decide to select a different set of waveforms to drive the panel.

- If the temperature is outside the allowed operating range of the panel, the processor is notified by the THOT and TCOLD interrupts, respectively. The processor may or may not decide to continue with the page update.

- When an overtemperature or undertemperature has been detected, the AP must reset the TMST\_HOT\_EN or TMST\_COLD\_EN bits, respectively, to avoid the nINT pin to be continuously pulled low. The TMST\_HOT and TMST\_COLD interrupt bits then must be polled continuously, to determine when the panel temperature recovers to the normal operating range. Once the temperature has recovered, the TMST\_HOT\_EN or TMST\_COLD\_EN bits must be set to 1 again and normal operation can resume.

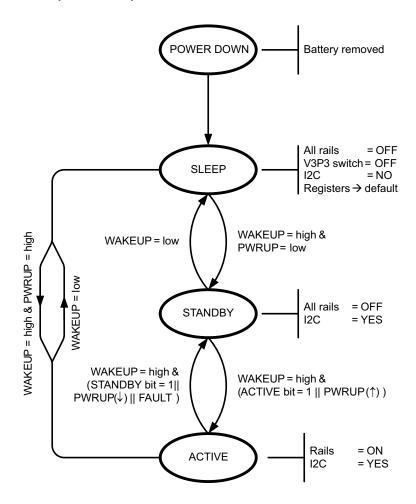

#### 8.4 Device Functional Modes

The TPS65186 has three modes of operation, SLEEP, STANDBY, and ACTIVE. SLEEP mode is the lowest-power mode in which all internal circuitry is turned off. In STANDBY, all power rails are shut down but the device is ready to accept commands through the I<sup>2</sup>C interface. In ACTIVE mode one or more power rails are enabled.

#### 8.4.1 SLEEP

This is the lowest power mode of operation. All internal circuitry is turned off, registers are reset to default values and the device does not respond to I<sup>2</sup>C communications. TPS65186 enters SLEEP mode whenever WAKEUP pin is pulled low.

#### 8.4.2 STANDBY

In STANDBY all internal support circuitry is powered up and the device is ready to accept commands through the I<sup>2</sup>C interface but none of the power rails are enabled. The device enters STANDBY mode when the WAKEUP pin is pulled high and either the PWRUP pin is pulled low or the STANDBY bit is set. The device also enters STANDBY mode if input undervoltage lockout (UVLO), positive boost undervoltage (VB\_UV), or inverting buckboost undervoltage (VN UV) is detected, thermal shutdown occurs, or the PROG bit is set (see Figure 22)

#### **8.4.3 ACTIVE**

The device is in ACTIVE mode when any of the output rails are enabled and no fault condition is present. This is the normal mode of operation while the device is powered up.

#### 8.4.4 Mode Transitions

#### 8.4.4.1 SLEEP → ACTIVE

WAKEUP pin is pulled high with PWRUP pin high. Rails come up in the order defined by the UPSEQx registers (OK to tie WAKEUP and PWRUP pin together).

#### 8.4.4.2 SLEEP → STANDBY

WAKEUP pin is pulled high with PWRUP pin low. Rails will remain powered down.

#### 8.4.4.3 STANDBY → ACTIVE

WAKEUP pin is high and PWRRUP pin is pulled high (rising edge) or the ACTIVE bit is set. Output rails will power up in the order defined by the UPSEQx registers.

#### 8.4.4.4 ACTIVE → STANDBY

WAKEUP pin is high and STANDBY bit is set or PWRUP pin is pulled low (falling edge). Rails are shut down in the order defined by DWNSEQx registers. Device also enters STANDBY in the event of thermal shutdown (TSD), undervoltage lockout (UVLO), positive boost or inverting buck-boost undervoltage (UV), VCOM fault (VCOMF), or when the PROG bit is set (see Figure 22).

#### 8.4.4.5 STANDBY → SLEEP

WAKEUP pin is pulled low while none of the output rails are enabled.

#### 8.4.4.6 ACTIVE → SLEEP

WAKEUP pin is pulled low while at least one output rail is enabled. Rails are shut down in the order defined by DWNSEQx registers.

### **Device Functional Modes (continued)**

#### NOTES:

||, & = logic OR, and AND.

$(\uparrow)$ ,  $(\downarrow)$  = rising edge, falling edge

UVLO = Undervoltage Lockout

TSD = Thermal Shutdown

UV = Undervoltage

FAULT = UVLO || TSD || BOOST UV || VCOM fault

Figure 24. Global State Diagram

#### 8.5 Programming

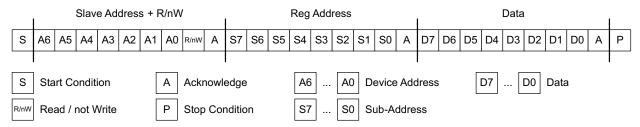

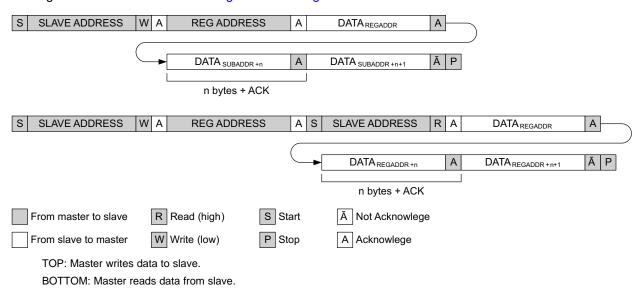

#### 8.5.1 I<sup>2</sup>C Bus Operation

The TPS65186 hosts a slave  $I^2C$  interface that supports data rates up to 400 kbit/s and auto-increment addressing and is compliant to  $I^2C$  standard 3.0.

Figure 25. Subaddress in I<sup>2</sup>C Transmission

The I<sup>2</sup>C Bus is a communications link between a controller and a series of slave terminals. The link is established using a two-wire bus consisting of a serial clock signal (SCL) and a serial data signal (SDA). The serial clock is sourced from the controller in all cases where the serial data line is bidirectional for data communication between the controller and the slave terminals. Each device has an open drain output to transmit data on the serial data line. An external pullup resistor must be placed on the serial data line to pull the drain output high during data transmission.

Data transmission is initiated with a start bit from the controller as shown in Figure 27. The start condition is recognized when the SDA line transitions from high to low during the high portion of the SCL signal. Upon reception of a start bit, the device will receive serial data on the SDA input and check for valid address and control information. If the appropriate slave address bits are set for the device, then the device will issue an acknowledge pulse and prepare to receive the register address. Depending on the R/nW bit, the next byte received from the master is written to the addressed register (R/nW = 0) or the device responds with 8-bit data from the register (R/nW = 1). Data transmission is completed by either the reception of a stop condition or the reception of the data word sent to the device. A stop condition is recognized as a low to high transition of the SDA input during the high portion of the SCL signal. All other transitions of the SDA line must occur during the low portion of the SCL signal. An acknowledge is issued after the reception of valid address, sub-address and data words. The I<sup>2</sup>C interfaces will auto-sequence through register addresses, so that multiple data words can be sent for a given I<sup>2</sup>C transmission. See Figure 26 and Figure 27 for details.

Figure 26. I<sup>2</sup>C Data Protocol

## **Programming (continued)**

Figure 27. I<sup>2</sup>C Start/Stop/Acknowledge Protocol

## 8.6 Register Maps

| REGISTER | ADDRESS (HEX) | NAME                                       | DESCRIPTION                         |

|----------|---------------|--------------------------------------------|-------------------------------------|

| 0        | 0x00          | TMST_VALUE                                 | Thermistor value read by ADC        |

| 1        | 0x01          | 0x01 ENABLE Enable/disable bits for regula |                                     |

| 2        | 0x02          | VADJ                                       | VPOS/VNEG voltage adjustment        |