# 具有集成眼图监视器和 4:1 输入多路复用器的 LMH0376 3 Gbps 高清/标清 (HD/SD) 串行数字接口 (SDI) 低功耗时钟恢复 器

查询样品: [LMH0376](#)

## 特性

- **SMPTE ST 424, SMPTE ST 292 和 SMPTE ST 259-C 兼容**

- 支持 **125Mbps, 270Mbps, 1.4835Gbps, 1.485Gbps, 2.967Gbps 和 2.97Gbps** 串行数据速率运行

- 在 **270Mbps** 时支持数字视频广播异步串口 (**DVB-ASI**)，在 **125Mbps** 时支持多通道音频数字接口 (**MADI**)

- **100mW** 典型功耗（启用两个输出驱动器时为 **145mW**）

- 集成型 **4:1** 复用输入，此输入具有 **0-60"FR4** 均衡器并且支持每个通道上的独立信号检测

- 两个具有恢复时钟选项的差分、时钟恢复输出

- 输出去加重来补偿高达 **40"** 的 **FR4** 迹线损耗

- **64 x 64** 点眼图张开监视器

- **27MHz** 外部基准或无基准运行

- 具有轨到轨输入共模电压的内部端接 **100Ω** 输入

- 具有可编程输出共模电压和摆动的内部端接 **100Ω** 低压差分信令 (**LVDS**) 输出

- 单个 **2.5V** 电源运行

- 具有器件断电控制的省电模式

- **48** 引脚超薄四方扁平无引线封装 (**WQFN**) (**7mm x 7mm**)

- 工业温度范围: **-40°C** 至 **+85°C**

- 与引脚模式中的 **LMH0356** 封装兼容

## 应用范围

- **SMPTE ST 424, SMPTE ST 292 和 SMPTE ST 259** 串行数字接口

- 广播视频路由器、交换机和信号分配放大器

## 说明

具有集成眼图监视器和 4:1 输入多路复用器的 LMH0376 3Gbps HD/SD SDI 低功耗时钟恢复器将串行数字视频数据重新定时为符合 SMPTE ST 424, SMPTE ST 292 和 SMPTE ST 259-C 标准的数据。时钟恢复器运行在 125Mbps, 270 Mbps, 1.4835Gbps, 1.485 Gbps, 2.967 Gbps 和 2.97Gbps 的串行数据速率上。

LMH0376 自动检测进入的数据速率，并且将此数据重定时以抑制累积抖动。此时钟恢复器将串行数据速率时钟恢复，并可选择将它作为一个输出提供。

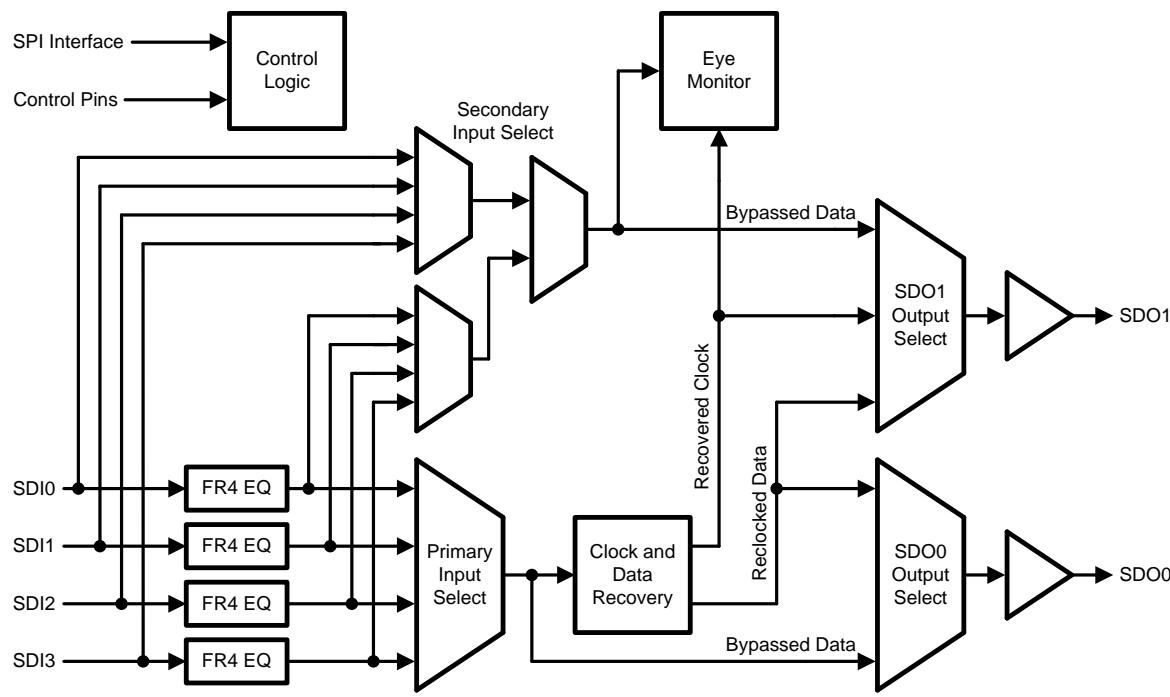

LMH0376 包括一个集成 4:1 输入多路复用器，选择四个输入数据流中的一个来进行重定时。四个输入中的每一个输入有一个能够均衡 0-60" FR4 迹线长度的 FR4 均衡器。每个输入还包括具有可编程阀值的独立信号检测。

LMH0376 具有两个差分串行数据输出，并且使用户能够从时钟恢复数据、恢复时钟、旁路数据或来自一个独立选中的输入通道的旁路数据之中灵活地选择输出信号。除了针对灵活对接的可编程共模电压和摆动，此输出驱动器提供针对高达 40"FR4 迹线损耗的可编程去加重。

LMH0376 提供一个用来分析进入信号眼图质量的 **64 x 64** 点眼图监视器。

LMH0376 支持两个运行模式。在引脚模式中，LMH0376 的运行状态由控制引脚设定，并且与 LMH0356 时钟恢复器封装兼容。在 SPI 模式下，一个可选 SPI 串行接口可被用来配置并且监视一个菊花链配置中的多个 LMH0376 器件。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

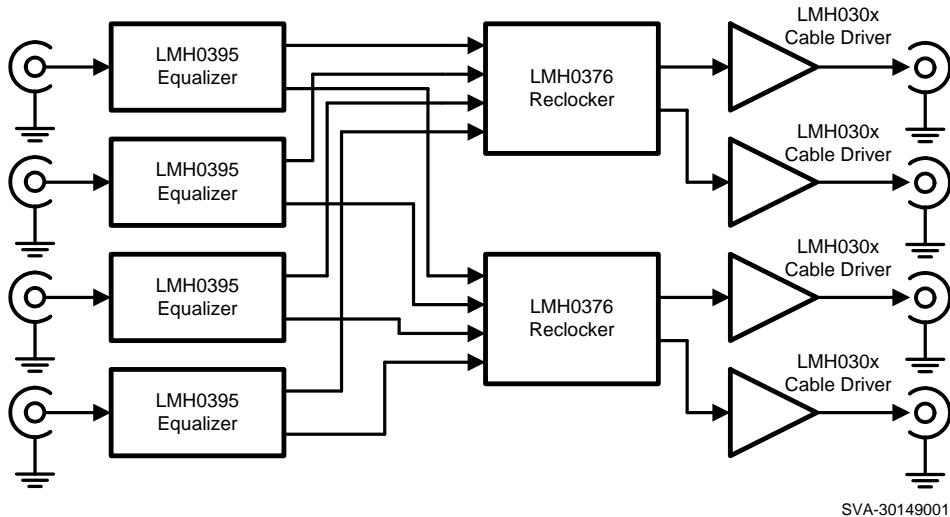

## Typical Application

## Block Diagram

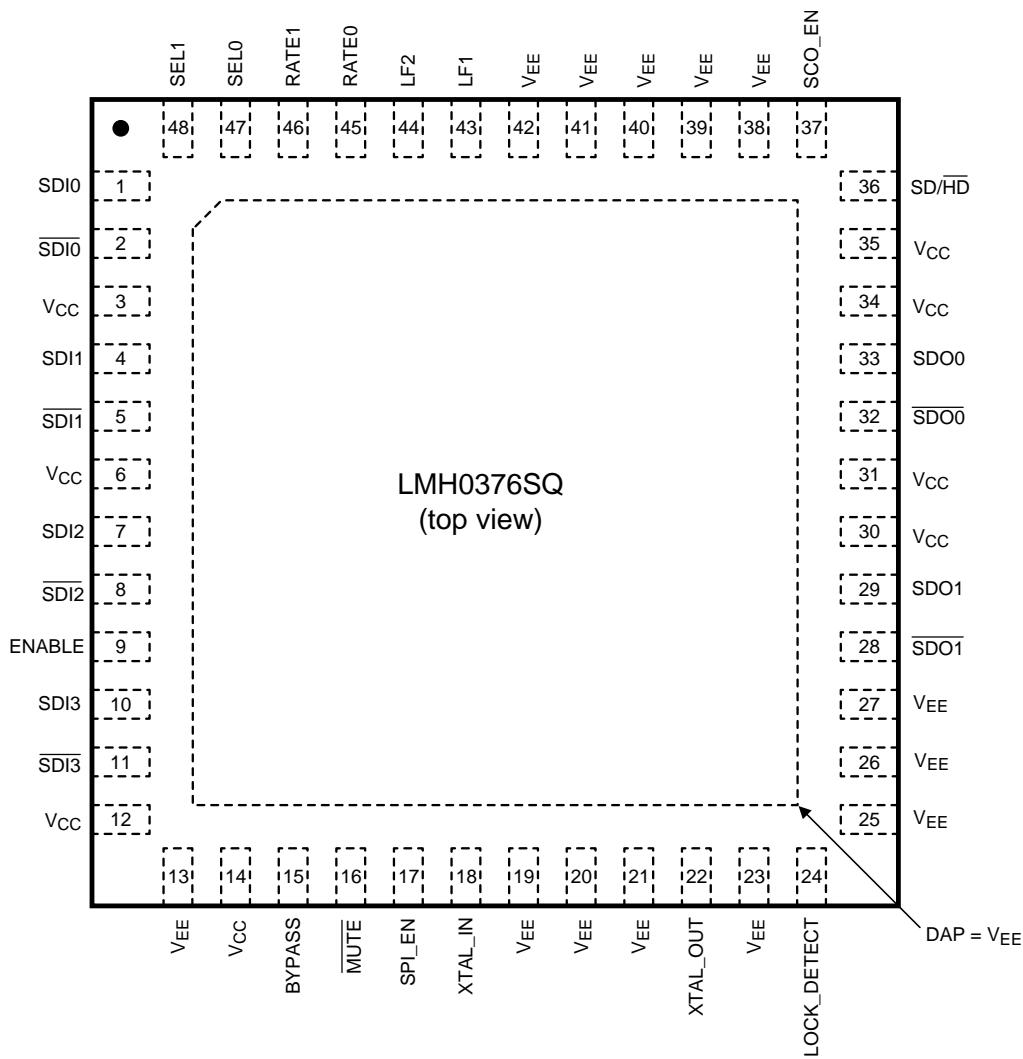

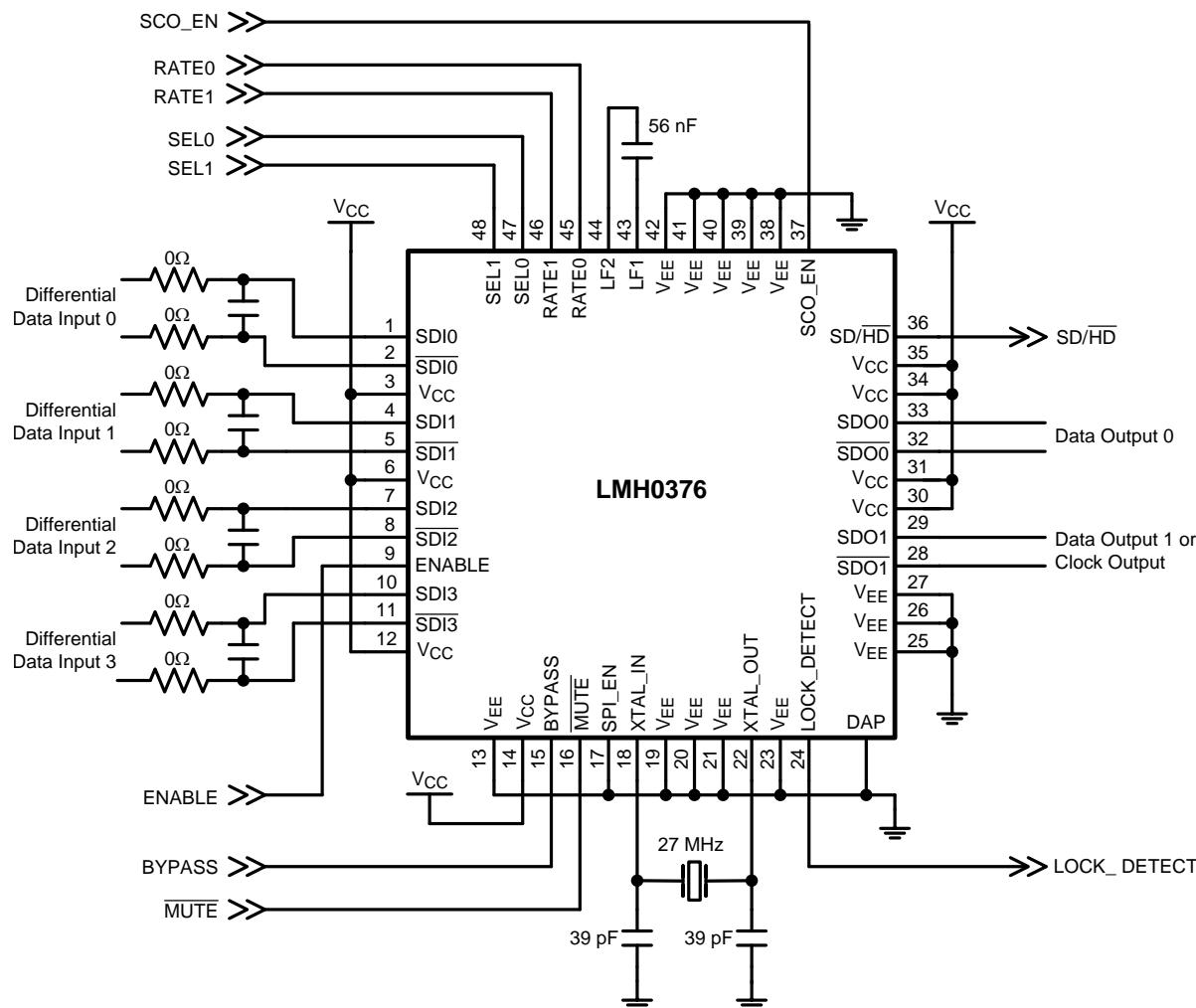

## Connection Diagrams

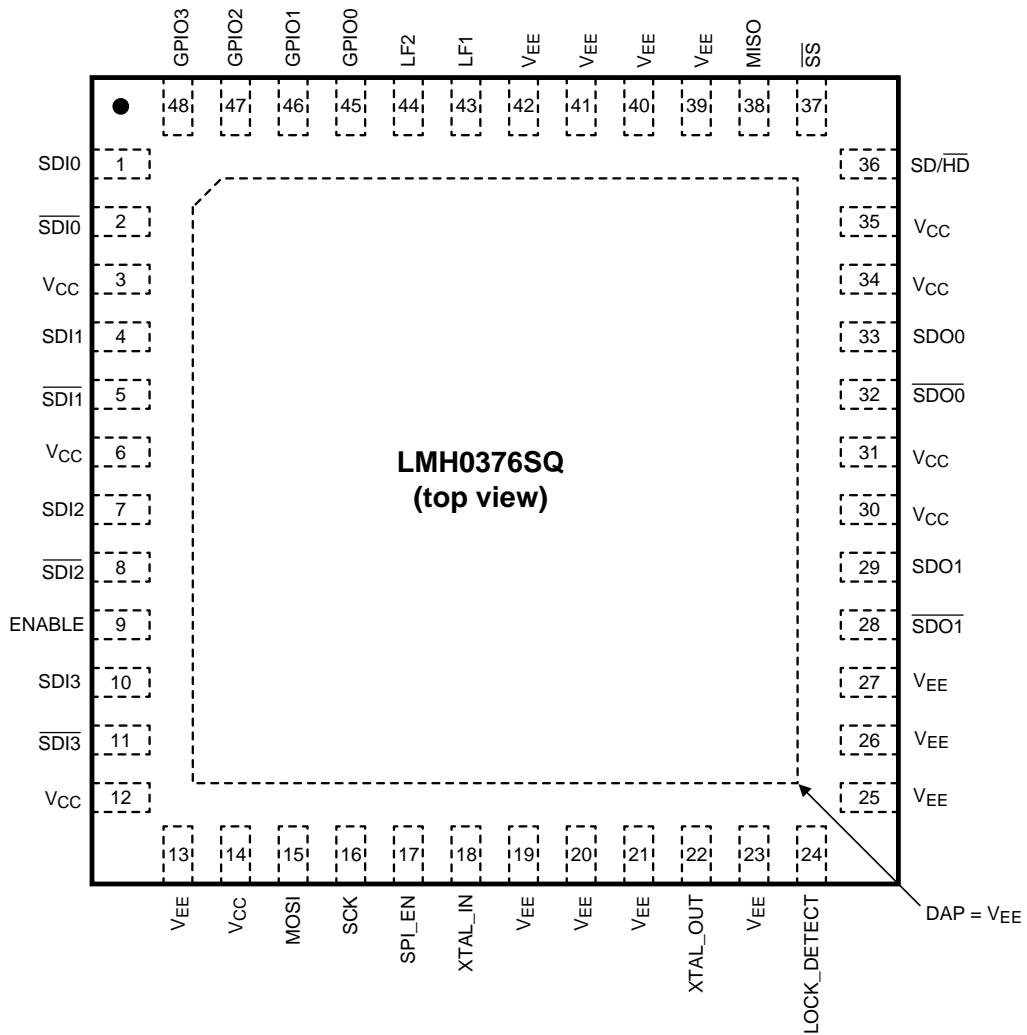

SVA-30149002

**Figure 1. Pin Mode (non-SPI) / SPI\_EN = GND / LMH0356 Compatible**

SVA-30149013

NOTE: The exposed die attach pad is the primary negative electrical terminal for this device. It must be connected to the negative power supply voltage.

**Figure 2. SPI Mode / SPI\_EN = V<sub>cc</sub>

48-Pin WQFN

See Package Number RHS 48**

**Table 1. PIN DESCRIPTIONS – Pin Mode (non-SPI) / SPI\_EN = GND / LMH0356 Compatible**

| Pin                                                     | Name               | I/O, Type | Description                                                                                                                                    |

|---------------------------------------------------------|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                                                    | SDI0, <u>SDI</u> 0 | I, SDI    | Serial data differential input 0.                                                                                                              |

| 4, 5                                                    | SDI1, <u>SDI</u> 1 | I, SDI    | Serial data differential input 1.                                                                                                              |

| 7, 8                                                    | SDI2, <u>SDI</u> 2 | I, SDI    | Serial data differential input 2.                                                                                                              |

| 9                                                       | ENABLE             | I, LVCMOS | Device enable. This pin has an internal pullup.<br>H = Device enabled (normal operation).<br>L = Device powered down.                          |

| 10, 11                                                  | SDI3, <u>SDI</u> 3 | I, SDI    | Serial data differential input 3.                                                                                                              |

| 15                                                      | BYPASS             | I, LVCMOS | Reclocker bypass. This pin has an internal pulldown.<br>H = Reclocking bypassed.<br>L = Normal operation.                                      |

| 16                                                      | MUTE               | I, LVCMOS | Output mute. This pin has an internal pullup.<br>H = Normal operation.<br>L = SDO0 and SDO1 outputs are muted.                                 |

| 17                                                      | SPI_EN             | I, LVCMOS | SPI register access enable. This pin has an internal pulldown.<br>H = SPI register access mode.<br>L = Pin mode.                               |

| 18                                                      | XTAL_IN            | I, ANALOG | External crystal or clock input for optional 27 MHz external reference. When not used (i.e. referenceless mode), connect to ground.            |

| 22                                                      | XTAL_OUT           | O, ANALOG | External crystal or clock output.                                                                                                              |

| 24                                                      | LOCK_DETECT        | O, LVCMOS | PLL lock detect status.<br>H = PLL locked.<br>L = PLL not locked.                                                                              |

| 28, 29                                                  | SDO1, SDO1         | O, LVDS   | Serial data differential output 1.                                                                                                             |

| 32, 33                                                  | <u>SDO</u> 0, SDO0 | O, LVDS   | Serial data differential output 0.                                                                                                             |

| 36                                                      | SD/ <u>HD</u>      | O, LVCMOS | Data rate range indication.<br>H = Locked data rate is SD.<br>L = Locked data rate is 3G or HD (or PLL unlocked).                              |

| 37                                                      | SCO_EN             | I, LVCMOS | Serial clock output enable for SDO1. This pin has an internal pulldown.<br>H = SDO1 output is serial clock.<br>L = SDO1 output is serial data. |

| 43, 44                                                  | LF1, LF2           | I, Analog | Loop filter. Connect a 56 nF capacitor between LF1 and LF2.                                                                                    |

| 45, 46                                                  | RATE0, RATE1       | I, LVCMOS | Data rate select inputs. RATE0 and RATE1 each has an internal pulldown.                                                                        |

| 47, 48                                                  | SEL0, SEL1         | I, LVCMOS | Input channel select inputs. SEL0 and SEL1 each has an internal pulldown.                                                                      |

| 3, 6, 12, 14, 30, 31, 34, 35                            | V <sub>CC</sub>    | Power     | Positive power supply (2.5V).                                                                                                                  |

| DAP, 13, 19, 20, 21, 23, 25, 26, 27, 38, 39, 40, 41, 42 | V <sub>EE</sub>    | Ground    | Negative power supply (ground).                                                                                                                |

**Table 2. PIN DESCRIPTIONS – SPI Mode / SPI\_EN = V<sub>CC</sub>**

| Pin                                                       | Name                          | I/O, Type   | Description                                                                                                                                                                                                                    |

|-----------------------------------------------------------|-------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2                                                      | SDI0, <u>SDI</u> 0            | I, SDI      | Serial data differential input 0.                                                                                                                                                                                              |

| 4, 5                                                      | SDI1, <u>SDI</u> 1            | I, SDI      | Serial data differential input 1.                                                                                                                                                                                              |

| 7, 8                                                      | SDI2, <u>SDI</u> 2            | I, SDI      | Serial data differential input 2.                                                                                                                                                                                              |

| 9                                                         | ENABLE                        | I, LVCMOS   | Device enable. This pin has an internal pullup.<br>H = Device enabled (normal operation).<br>L = Device powered down.                                                                                                          |

| 10, 11                                                    | SDI3, <u>SDI</u> 3            | I, SDI      | Serial data differential input 3.                                                                                                                                                                                              |

| 15                                                        | MOSI (SPI)                    | I, LVCMOS   | SPI master output / slave input. LMH0376 data receive. This pin has an internal pullup.                                                                                                                                        |

| 16                                                        | SCK (SPI)                     | I, LVCMOS   | SPI serial clock input.                                                                                                                                                                                                        |

| 17                                                        | SPI_EN                        | I, LVCMOS   | SPI register access enable. This pin has an internal pulldown.<br>H = SPI register access mode.<br>L = Pin mode.                                                                                                               |

| 18                                                        | XTAL_IN                       | I, ANALOG   | External crystal or clock input for optional 27 MHz external reference. When not used (i.e. referenceless mode), connect to ground.                                                                                            |

| 22                                                        | XTAL_OUT                      | O, ANALOG   | External crystal or clock output.                                                                                                                                                                                              |

| 24                                                        | LOCK_DETECT                   | O, LVCMOS   | PLL lock detect status.<br>H = PLL locked.<br>L = PLL not locked.                                                                                                                                                              |

| 28, 29                                                    | <u>SDO</u> 1, SDO1            | O, LVDS     | Serial data differential output 1.                                                                                                                                                                                             |

| 32, 33                                                    | <u>SDO</u> 0, SDO0            | O, LVDS     | Serial data differential output 0.                                                                                                                                                                                             |

| 36                                                        | SD/ <u>HD</u>                 | O, LVCMOS   | Data rate range indication.<br>H = Locked data rate is SD.<br>L = Locked data rate is 3G or HD (or PLL unlocked).                                                                                                              |

| 37                                                        | <u>SS</u> (SPI)               | I, LVCMOS   | SPI slave select. This pin has an internal pullup.                                                                                                                                                                             |

| 38                                                        | MISO (SPI)                    | O, LVCMOS   | SPI master input / slave output. LMH0376 data transmit.                                                                                                                                                                        |

| 43, 44                                                    | LF1, LF2                      | I, Analog   | Loop filter. Connect a 56 nF capacitor between LF1 and LF2.                                                                                                                                                                    |

| 45, 46, 47, 48                                            | GPIO0, GPIO1,<br>GPIO2, GPIO3 | I/O, LVCMOS | General purpose input/output pins, selectable via the SPI. Pins 45-48 will operate as RATE0, RATE1, SEL0, and SEL1 inputs (the same as while in pin mode), with internal pulldowns, unless configured differently via the SPI. |

| 3, 6, 12, 14, 30,<br>31, 34, 35                           | V <sub>CC</sub>               | Power       | Positive power supply (2.5V).                                                                                                                                                                                                  |

| DAP, 13, 19, 20,<br>21, 23, 25, 26, 27,<br>39, 40, 41, 42 | V <sub>EE</sub>               | Ground      | Negative power supply (ground).                                                                                                                                                                                                |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)</sup>

|                            |                           | MIN  | MAX             | UNIT |

|----------------------------|---------------------------|------|-----------------|------|

| Supply Voltage, $V_{CC}$   |                           |      | 3.1             | V    |

| Input Voltage (any input)  |                           | -0.3 | $V_{CC} + 0.3$  | V    |

| Storage Temperature Range  |                           | -65  | 150             | °C   |

| Junction Temperature       |                           |      | 125             | °C   |

| Package Thermal Resistance | $\theta_{JA}$ 48-pin WQFN |      | 31.3            | °C/W |

|                            | $\theta_{JC}$ 48-pin WQFN |      | 8.5             | °C/W |

| ESD Rating                 | HBM, STD - JESD22-A114F   |      | $\geq \pm 6$    | kV   |

|                            | MM, STD - JESD22-A115-A   |      | $\geq \pm 250$  | V    |

|                            | CDM, STD - JESD22-C101-D  |      | $\geq \pm 1250$ | V    |

- (1) "Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied.

- (2) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/Distributors for availability and specifications.

## RECOMMENDED OPERATING CONDITIONS<sup>(1)</sup>

|                                       |  | MIN   | NOM | MAX      | UNIT |

|---------------------------------------|--|-------|-----|----------|------|

| Supply Voltage, $V_{CC}$              |  | 2.375 | 2.5 | 2.625    | V    |

| Input Voltage                         |  | 0     |     | $V_{CC}$ | V    |

| Operating Free Air Temperature, $T_A$ |  | -40   | 25  | 85       | °C   |

- (1) The Recommended Operating Conditions indicate conditions at which the device is functional and the device should not be operated beyond such conditions. Absolute Maximum Numbers are ensured for a junction temperature range of -40°C to +125°C. Models are validated to Maximum Operating Voltages only.

## DC ELECTRICAL CHARACTERISTICS

Over recommended supply voltage and operating temperature ranges, unless otherwise specified.<sup>(1)(2)</sup>

| Symbol          | Parameter                                                       | Conditions                                                                                | Reference              | Min      | Typ | Max      | Units                    |

|-----------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------|----------|-----|----------|--------------------------|

| $V_{IH}$        | Input Voltage High Level                                        |                                                                                           | Logic inputs           | 1.7      |     | $V_{CC}$ | V                        |

| $V_{IL}$        | Input Voltage Low Level                                         |                                                                                           |                        | $V_{EE}$ |     | 0.7      | V                        |

| $I_{IN}$        | Input Current                                                   |                                                                                           |                        | -55      |     | 55       | $\mu A$                  |

| $V_{OH}$        | Output Voltage High Level                                       | $I_{OH} = -2\text{ mA}$                                                                   | Logic outputs          | 2.0      |     |          | V                        |

| $V_{OL}$        | Output Voltage Low Level                                        | $I_{OL} = +2\text{ mA}$                                                                   |                        |          |     | 0.2      | V                        |

| $V_{SDID}$      | Serial Input Voltage, Differential                              | See <sup>(3)</sup>                                                                        | SDI0, SDI1, SDI2, SDI3 | 200      |     | 1600     | $\text{mV}_{\text{P-P}}$ |

| $V_{CMI}$       | Input Common Mode Voltage                                       | See <sup>(3)</sup>                                                                        |                        | 0        |     | $V_{CC}$ | V                        |

| $R_{IN}$        | Input Termination Resistor                                      | Between SDI and SDI <sup>(4)</sup>                                                        |                        |          | 100 |          | $\Omega$                 |

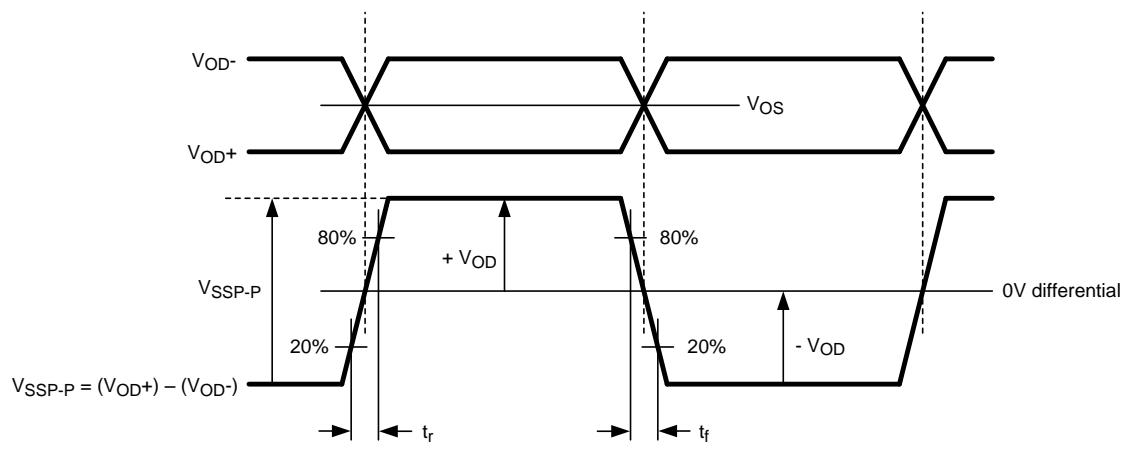

| $V_{SSP-P}$     | Differential Output Voltage, P-P                                | 100 $\Omega$ load, default register settings <sup>(5)</sup> ,<br><a href="#">Figure 3</a> | SDO0, SDO1             | 700      | 800 | 1000     | $\text{mV}_{\text{P-P}}$ |

| $V_{OD}$        | Differential Output Voltage                                     |                                                                                           |                        | 350      | 400 | 500      | $\text{mV}_{\text{P-P}}$ |

| $\Delta V_{OD}$ | Change in Magnitude of $V_{OD}$ for Complimentary Output States |                                                                                           |                        |          |     | 50       | mV                       |

| $V_{OS}$        | Offset Voltage                                                  |                                                                                           |                        | 1.1      | 1.2 | 1.375    | V                        |

| $\Delta V_{OS}$ | Change in Magnitude of $V_{OS}$ for Complimentary Output States |                                                                                           |                        |          |     | 50       | mV                       |

| $I_{OS}$        | Output Short Circuit Current                                    |                                                                                           |                        |          |     | 30       | mA                       |

| $I_{CC}$        | Supply Current                                                  | Normal operation, two output drivers                                                      |                        |          | 58  | 75       | mA                       |

|                 |                                                                 | Normal operation, one output driver and low power settings <sup>(6)</sup>                 |                        |          | 40  | 55       | mA                       |

|                 |                                                                 | Device disabled (ENABLE = 0)                                                              |                        |          | 7   | 14       | mA                       |

- (1) The Electrical Characteristics tables list ensures specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only.

- (2) Typical values represent most likely parametric norms at  $V_{CC} = +2.5\text{V}$ ,  $T_A = +25^\circ\text{C}$ , and at the Recommended Operating Conditions at the time of product characterization and are not specified.

- (3) Specified by characterization and not tested in production.

- (4) The LMH0376 provides an integrated 100 $\Omega$  input termination resistor for each serial data input pair.

- (5) The differential output voltage and offset voltage are adjustable via the SPI.

- (6) Low power mode with one output driver is achieved by powering down the second output driver, setting the amplitude of the active output driver to the lowest setting, disabling signal detection for all input channels, and disabling equalization for all input channels except SDI0. This can be configured with the following SPI register settings: write "1" to register 0x20 bit 7 (SIG\_DET\_PRESET) to force the reclocker to assume an input signal is present (so input signal detection can be turned off), write "1" to register 0x11 bit 3 (SDO1\_PD) to power down the SDO1 output driver, write "00" to register 0x12 bits 7:6 (SDO0\_VOD) to set the SDO0  $V_{OD}$  to 400  $\text{mV}_{\text{P-P}}$ , and write "1111110" (0xFE) to register 0x15 to power down the input signal detection for all input channels and power down the input equalization for all input channels except SDI0.

## AC ELECTRICAL CHARACTERISTICS

Over recommended supply voltage and operating temperature ranges, unless otherwise specified.<sup>(1)(2)</sup>

| Symbol                          | Parameter                               | Conditions                          | Reference              | Min  | Typ          | Max  | Units             |

|---------------------------------|-----------------------------------------|-------------------------------------|------------------------|------|--------------|------|-------------------|

| DR <sub>SDI</sub>               | Serial Input Data Rate (for reclocking) | MADI                                | SDI0, SDI1, SDI2, SDI3 |      | 125          |      | Mbps              |

|                                 |                                         | SMPTE ST 259-C, DVB-ASI             |                        |      | 270          |      | Mbps              |

|                                 |                                         | SMPTE ST 292                        |                        |      | 1483.5, 1485 |      | Mbps              |

|                                 |                                         | SMPTE ST 424                        |                        |      | 2967, 2970   |      | Mbps              |

| TOL <sub>JIT</sub>              | Serial Input Jitter Tolerance           | See <sup>(3)(4)(5)</sup>            |                        | >6   |              |      | UI <sub>P-P</sub> |

|                                 |                                         | See <sup>(3)(4)(6)</sup>            |                        | >0.6 |              |      | UI <sub>P-P</sub> |

| t <sub>JIT</sub>                | Serial Data Output Intrinsic Jitter     | 270 Mbps <sup>(3)</sup>             | SDO0, SDO1             |      | 0.01         | 0.02 | UI <sub>P-P</sub> |

|                                 |                                         | 1483.5 or 1485 Mbps <sup>(3)</sup>  |                        |      | 0.02         | 0.05 | UI <sub>P-P</sub> |

|                                 |                                         | 2967 or 2970 Mbps <sup>(3)</sup>    |                        |      | 0.04         | 0.1  | UI <sub>P-P</sub> |

| BW <sub>LOOP</sub>              | Loop Bandwidth                          | 270 Mbps, <0.1dB Peaking            |                        |      | 350          |      | kHz               |

|                                 |                                         | 1485 Mbps, <0.1dB Peaking           |                        |      | 2.0          |      | MHz               |

|                                 |                                         | 2970 Mbps, <0.1dB Peaking           |                        |      | 3.5          |      | MHz               |

| F <sub>CO</sub>                 | Serial Clock Output Frequency           | 125 Mbps data rate                  | SDO1                   |      | 125          |      | MHz               |

|                                 |                                         | 270 Mbps data rate                  |                        |      | 270          |      | MHz               |

|                                 |                                         | 1483.5 Mbps data rate               |                        |      | 1483.5       |      | MHz               |

|                                 |                                         | 1485 Mbps data rate                 |                        |      | 1485         |      | MHz               |

|                                 |                                         | 2967 Mbps data rate                 |                        |      | 2967         |      | MHz               |

|                                 |                                         | 2970 Mbps data rate                 |                        |      | 2970         |      | MHz               |

| t <sub>LOCK</sub>               | Asynchronous Lock Time                  | See <sup>(7)</sup>                  |                        |      |              | 15   | ms                |

| t <sub>SYNLOCK</sub>            | Synchronous Lock Time                   | See <sup>(8)</sup>                  |                        |      |              | 1    | ms                |

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall Time                   | 20% – 80%, 100Ω load <sup>(3)</sup> | SDO0, SDO1             |      | 80           | 130  | ps                |

- (1) The Electrical Characteristics tables list ensures specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only.

- (2) Typical values represent most likely parametric norms at V<sub>CC</sub> = +2.5V, T<sub>A</sub> = +25°C, and at the Recommended Operating Conditions at the time of product characterization and are not specified.

- (3) Specified by characterization and not tested in production.

- (4) Peak-to-peak amplitude with sinusoidal modulation per SMPTE RP 184-1996 paragraph 4.1. The test data signal shall be color bars.

- (5) Refer to “A1” in Figure 1 of SMPTE RP 184-1996.

- (6) Refer to “A2” in Figure 1 of SMPTE RP 184-1996.

- (7) Time to acquire lock when an input signal is first applied or when the data rate of the input signal is changed.

- (8) Time to reacquire lock after the switch to another input signal at the same data rate as the PLL is currently locked.

## AC ELECTRICAL CHARACTERISTICS - SPI

Over recommended supply voltage and operating temperature ranges, unless otherwise specified.<sup>(1)</sup> <sup>(2)</sup>

| Symbol                           | Parameter                    | Conditions                                              | Reference       | Min | Typ | Max | Units        |

|----------------------------------|------------------------------|---------------------------------------------------------|-----------------|-----|-----|-----|--------------|

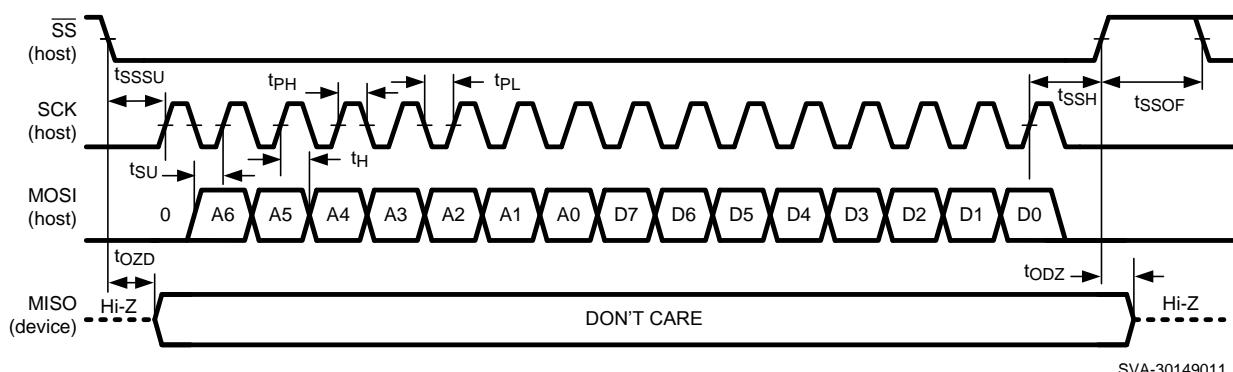

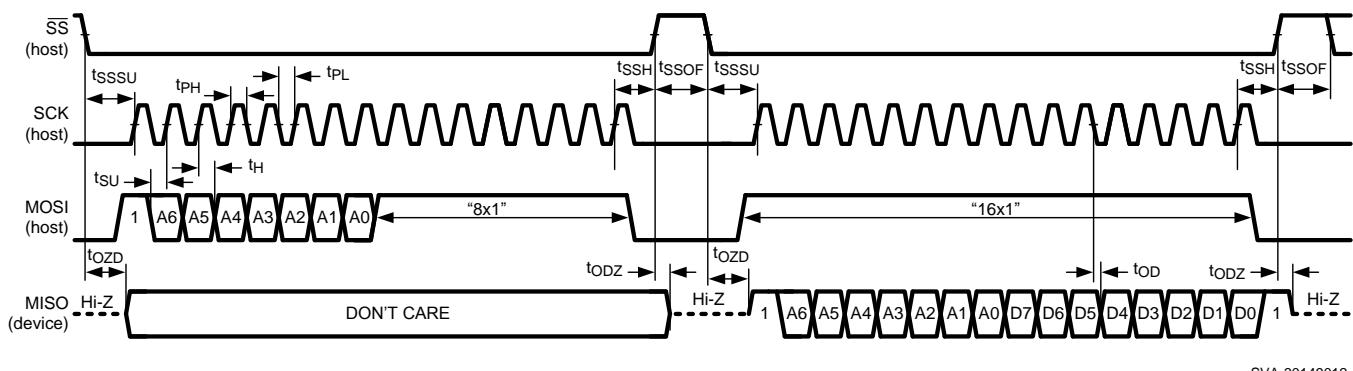

| $f_{SCK}$                        | SCK Frequency                | See <a href="#">Figure 4</a> , <a href="#">Figure 5</a> | SCK             |     |     | 20  | MHz          |

| $t_{PH}$                         | SCK Pulse Width High         |                                                         |                 | 40  |     |     | % SCK period |

| $t_{PL}$                         | SCK Pulse Width Low          |                                                         |                 | 40  |     |     | % SCK period |

| $t_{SU}$                         | MOSI Setup Time              | See <a href="#">Figure 4</a> , <a href="#">Figure 5</a> | MOSI            | 4   |     |     | ns           |

| $t_H$                            | MOSI Hold Time               |                                                         |                 | 4   |     |     | ns           |

| $t_{SSSU}$                       | $\overline{SS}$ Setup Time   | See <a href="#">Figure 4</a> , <a href="#">Figure 5</a> | $\overline{SS}$ | 14  |     |     | ns           |

| $t_{SSH}$                        | $\overline{SS}$ Hold Time    |                                                         |                 | 4   |     |     | ns           |

| $t_{SSOF}$                       | $\overline{SS}$ Off Time     |                                                         |                 | 1   |     |     | SCK period   |

| <b>Switching Characteristics</b> |                              |                                                         |                 |     |     |     |              |

| $t_{ODZ}$                        | MISO Driven-to-Tristate Time | See <a href="#">Figure 5</a>                            | MISO            |     |     | 20  | ns           |

| $t_{OZD}$                        | MISO Tristate-to-Driven Time |                                                         |                 |     |     | 10  | ns           |

| $t_{OD}$                         | MISO Output Delay Time       |                                                         |                 |     |     | 15  | ns           |

- (1) The Electrical Characteristics tables list ensures specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations.

- (2) Typical values represent most likely parametric norms at  $V_{CC} = +2.5V$ ,  $T_A = +25^\circ C$ , and at the Recommended Operating Conditions at the time of product characterization and are not specified.

### TIMING DIAGRAMS

**Figure 3. LVDS Output Voltage, Offset, and Timing Parameters**

**Figure 4. SPI Write**

**Figure 5. SPI Read**

## FUNCTIONAL DESCRIPTION

The LMH0376 is a multi-rate reclocker for serial digital video data and operates at 125 Mbps, 270 Mbps, 1.4835 Gbps, 1.485 Gbps, 2.967 Gbps, and 2.97 Gbps. The LMH0376 recovers the serial clock and retimes the serial data stream to suppress accumulated jitter.

### MODES OF OPERATION

The LMH0376 has two modes of operation: pin mode (SPI\_EN = 0) and SPI mode (SPI\_EN = 1).

In pin mode, the LMH0376 functions are controlled by control pins only, and the device is footprint compatible with the LMH0356 reclocker.

SPI mode allows access to SPI registers for controlling all LMH0376 features, including additional features such as:

- Eye opening monitor

- Output driver amplitude, common mode voltage, and de-emphasis controls

- Signal detection on each input channel

- More control over which signals are sent to the output drivers

- Full details of the locked data rate

- Ability to distinguish between 1.4835 and 1.485 Gbps, and between 2.967 and 2.97 Gbps (in external reference mode)

- Ability to configure device pins as GPIOs

- Ability to power down unused features for power savings

The LMH0376 SPI protocol is described in the [SPI Register Access](#) section.

Four device pins are dual mode and change functionality depending on whether the device is in pin mode or SPI mode, as indicated in [Table 3](#).

**Table 3. Pin Mode vs. SPI Mode Pin Changes**

| Pin | Pin Mode (SPI_EN = 0) | SPI Mode (SPI_EN = 1) |

|-----|-----------------------|-----------------------|

| 15  | BYPASS                | MOSI                  |

| 16  | MUTE                  | SCK                   |

| 37  | SCO_EN                | SS                    |

| 38  | V <sub>EE</sub>       | MISO                  |

SPI mode provides the ability to configure four device pins as general purpose input/output (GPIO) pins for such functions as displaying the input signal detection status or displaying the locked data rate. With default register settings, pins 45-48 operate as RATE0, RATE1, SEL0, and SEL1. In SPI mode, these pins can be configured as GPIOs (GPIO0, GPIO1, GPIO2, and GPIO3, respectively), but they do not explicitly change function to GPIOs upon entering SPI mode by setting SPI\_EN high. These pins will continue to operate as RATE0, RATE1, SEL0, and SEL1 until they are optionally configured differently via SPI register writes. Once changed, these pins will continue to operate as GPIOs even after reentering pin mode by setting SPI\_EN low.

### SERIAL DATA INPUT

The LMH0376 provides four differential data inputs: SDI0, SDI1, SDI2, and SDI3. These inputs have 100Ω differential internal terminations and support rail-to-rail input common mode voltages for versatility in DC input coupling. They are intended to be DC coupled to devices such as the LMH0394 adaptive cable equalizer.

The inputs are independently equalized and then multiplexed. Each input has an independent signal detect with a programmable threshold, accessible via the SPI.

#### Input FR4 Equalization

Each input includes an FR4 equalizer capable of equalizing up to 60" of FR4 trace.

The FR4 equalizer can be optimized for long trace lengths via the SPI. For input FR4 trace lengths longer than 40", it is recommended to set register 0x11 bit 1 (EQ\_BOOST\_60) to enable additional equalizer boost in order to compensate for the longer trace length.

## Input Signal Detection

Each input channel includes an independent signal detect circuit accessible via the SPI. The status of the input signal detection is indicated by register 0x01 bits 3:0 (SIG\_DET\_SDI) for SDI3, SDI2, SDI1, and SDI0. Register 0x03 bit 4 (SIG\_DET\_ACT) indicates the signal detection status for the currently selected input.

The signal detection threshold is adjustable via register 0x20 bits 5:3 (SIG\_DET\_LVL). The signal detection status for each input channel can optionally be indicated via the GPIO pins (see the [GENERAL PURPOSE INPUT/OUTPUT PINS \(GPIO\[3:0\]\)](#) section).

## INPUT SELECTION

The LMH0376 includes a 4:1 input mux to allow the connection of up to four independent serial data streams. The active input channel is selected either via the SEL0 and SEL1 pins or through SPI register access. With default register settings, the SEL0 and SEL1 pins select the active input, as shown in [Table 4](#). The SEL0 and SEL1 pins have internal pulldowns to select the SDI0 input by default.

**Table 4. Input Channel Selection**

| SEL1 | SEL0 | Selected Input |

|------|------|----------------|

| 0    | 0    | SDI0           |

| 0    | 1    | SDI1           |

| 1    | 0    | SDI2           |

| 1    | 1    | SDI3           |

SPI register access allows additional control over the input selection, including independent control of the input that goes to the eye opening monitor and to the bypassed data for the SDO1 output via a secondary input selection (see [Block Diagram](#)).

Upon entering SPI mode, the SEL pins will continue to select the active input channel. Setting register 0x1E bit 7 (INPUT\_SEL\_OV) overrides this selection and allows the input selection to be controlled by register 0x20 bits 2:1 (IN\_CH\_SEL) instead of the SEL pins. (This frees up the SEL0 and SEL1 pins to be used as GPIOs since they are no longer needed for input selection.)

Furthermore, the secondary input select can be controlled independently of the primary input select by setting register 0x14 bit 5 (MUX2\_OV). By default, the selected input is the same for both the primary and secondary input selects, but when this bit is set, the secondary input select is individually controlled by register 0x18 bits 1:0 (MUX2\_SEL). This allows the selection of any input channel for eye monitoring or physically monitoring on the SDO1 output. By default, this secondary input is equalized (the same as the primary input). Register 0x14 bit 1 (MUX2\_EQ\_SEL) selects between non-equalized or equalized data (before or after the FR4 equalizer) for the secondary input.

## SERIAL DATA OUTPUT

The LMH0376 provides two internally terminated 100Ω LVDS outputs: SDO0 and SDO1. The SDO0 output provides either serial reclocked data or bypassed data. The SDO1 output provides either serial reclocked data, the recovered serial clock, or bypassed data. Through SPI register access, the bypassed data on the SDO1 output can be independently selected from any input channel.

The LMH0376 output should be DC coupled to the input of the receiving device where possible. 100Ω transmission lines should be used to connect between the LMH0376 outputs and the input of the receiving device. The LMH0376 output should not be DC coupled to CML inputs. If there are strong pullup resistors (e.g. 50Ω) at the receiving device, AC coupling should be used.

The output driver swing (amplitude), offset voltage (common mode voltage), and de-emphasis level are adjustable via the SPI. In addition, the SPI register access allows the signal polarity of the output drivers to be inverted and the output drivers to be independently powered down.

### Output Swing ( $V_{OD}$ )

The default peak-to-peak differential output voltage is 800 mV<sub>P-P</sub>. The output swing is individually adjustable for the two output drivers via register 0x12 bits 7:6 (SDO0\_VOD) and bits 5:4 (SDO1\_VOD). The output swing may be selected between 400 mV<sub>P-P</sub>, 530 mV<sub>P-P</sub>, 670 mV<sub>P-P</sub>, and 800 mV<sub>P-P</sub>.

### Offset Voltage (V<sub>os</sub>)

The default offset voltage is 1.2V. The offset voltage is adjustable via register 0x11 bits 7:6 (SDO\_VOS). The offset voltage may be selected between 0.8V, 1.0V, and 1.2V. This setting applies to both the SDO0 and SDO1 output drivers.

### Output De-Emphasis

Output de-emphasis compensates for board trace losses. The output driver de-emphasis is turned off (0 dB) by default. The output de-emphasis is individually adjustable for the two output drivers via register 0x13 bits 7:6 (SDO0\_DEM) and bits 5:4 (SDO1\_DEM). The output de-emphasis may be selected between 0 dB (no de-emphasis, for driving up to 10" FR4), 3 dB (for driving 10-20" FR4), 5 dB (for driving 20-30" FR4), and 7 dB (for driving 30-40" FR4).

### Output Polarity Inversion

The output polarity of both output drivers can be inverted via register 0x11 bit 0 (SDO\_INV). This may be useful to preserve the proper signal polarity for polarity sensitive applications (e.g. DVB-ASI) in which the polarity of the reclocker's input or output signal needs to be swapped for layout reasons.

### Output Power Down

The output drivers may be individually powered down via register 0x11 bit 4 (SDO0\_PD) and bit 3 (SDO1\_PD).

### LOCK DETECT

The lock detect indicates when the reclocker is locked to the incoming data stream. The lock detection status can be monitored by the active-high LOCK\_DETECT pin, or by reading register 0x01 bit 4 (LOCK\_DET). Note that when the bypass mode is active, lock detect will not assert. See [Table 5](#).

### OUTPUT MUTE

The output mute places the SDO0 and SDO1 outputs into the muted state. When muted, the outputs will be forced to a logic 0. The output mute has precedence over the bypass mode. See [Table 5](#).

In pin mode, the output mute is controlled by the active-low  $\overline{\text{MUTE}}$  pin. The  $\overline{\text{MUTE}}$  pin has an internal pullup to enable the outputs by default.

In SPI mode, the output mute is controlled by register 0x12 bit 1 ( $\overline{\text{MUTE}}$ ), as long as manual output selection is not enabled (i.e. as long as register 0x09 bit 5, PIN\_MODE\_OV, remains cleared). The muted state of the output drivers can be changed via register 0x14 bit 7 (MUTE\_STATE) so that, when muted, the outputs are forced to a logic 1 instead of a logic 0.

### BYPASS MODE

The bypass mode forces the reclocker to output the serial data without reclocking it. In bypass mode, bypassed (non-reclocked) data will be present on both the SDO0 and SDO1 outputs (unless SDO1 is configured for the serial clock, in which case the SDO1 output will be muted). When not in bypass mode, the reclocker will still automatically bypass the reclocking function when the detected data rate is a rate which the device does not support. Note that when the bypass mode is active, lock detect will not assert. See [Table 5](#).

In pin mode, the bypass mode is controlled by the active-high BYPASS pin. The BYPASS pin has an internal pulldown to disable reclocker bypassing by default.

In SPI mode, the bypass mode is controlled by register 0x12 bit 2 (BYPASS). Note that the eye opening monitor is not operational while the bypass mode is enabled.

## SERIAL CLOCK OUTPUT ENABLE (SCO\_EN)

The serial clock output enable (SCO\_EN) controls whether the SDO1 output is the serial clock or data. When SCO\_EN is asserted, the SDO1 output will be the recovered serial clock. If the SDO1 output is configured for the serial clock and either bypass mode is activated or the PLL lock is lost, then the SDO1 output will be muted. See [Table 5](#).

In pin mode, this function is controlled by the active-high SCO\_EN pin. The SCO\_EN pin has an internal pulldown to configure the SDO1 output as serial data by default.

In SPI mode, this function is controlled by register 0x12 bit 0 (SCO\_EN), as long as manual output selection is not enabled (i.e. as long as register 0x09 bit 5, PIN\_MODE\_OV, remains cleared).

**Table 5. SDO0 and SDO1 Output Configuration Based on MUTE, BYPASS, SCO\_EN and LOCK DETECT**

| MUTE | BYPASS | SCO_EN | LOCK DETECT | SDO0 Output    | SDO1 Output     |

|------|--------|--------|-------------|----------------|-----------------|

| 0    | X      | X      | X           | Muted          | Muted           |

| 1    | 1      | 0      | 0           | Bypassed data  | Bypassed data   |

| 1    | 1      | 1      | 0           | Bypassed data  | Muted           |

| 1    | 0      | 0      | 0           | Bypassed data  | Bypassed data   |

| 1    | 0      | 1      | 0           | Bypassed data  | Muted           |

| 1    | 0      | 0      | 1           | Reclocked data | Reclocked data  |

| 1    | 0      | 1      | 1           | Reclocked data | Recovered clock |

## MANUAL OUTPUT SELECTION

In pin mode and in SPI mode with default register settings, the SDO0 and SDO1 outputs are configured by the BYPASS, MUTE, and SCO\_EN functions according to [Table 5](#). (In pin mode, these functions are controlled by the BYPASS, MUTE, and SCO\_EN pins, and in SPI mode, these functions are controlled by register 0x12 bits 2:0.)

SPI register access allows the SDO0 and SDO1 outputs to be manually selected instead of using the BYPASS, MUTE, and SCO\_EN functions. Upon entering SPI mode, the SDO0 and SDO1 outputs will be configured by register 0x12 bits 2:0 (BYPASS, MUTE, and SCO\_EN). Register 0x09 bit 5 (PIN\_MODE\_OV) can be used to override this control and choose manual SDO0 and SDO1 output selection. Once this override bit is set, then register 0x1E bits 6:5 (SDO0\_SEL) select the output for SDO0 according to [Table 6](#), and register 0x1E bits 4:3 (SDO1\_SEL) select the output for SDO1 according to [Table 7](#). Note that register 0x09 bit 5 (PIN\_MODE\_OV) overrides the use of register 0x12 bits 1:0 (MUTE and SCO\_EN), but register 0x12 bit 2 (BYPASS), will still operate and can be used to bypass reclocking for both outputs.

**Table 6. SDO0 Manual Output Selection (via Register 0x1E bits 6:5)**

| SDO0_SEL[1:0] | SDO0 Output     |                 |

|---------------|-----------------|-----------------|

|               | Lock Detect = 1 | Lock Detect = 0 |

| 00            | Reclocked data  | Bypassed data   |

| 01            | Bypassed data   | Bypassed data   |

| 10            | Muted           | Muted           |

| 11            | Reclocked data  | Bypassed data   |

**Table 7. SDO1 Manual Output Selection (via Register 0x1E bits 4:3)**

| SDO1_SEL[1:0] | SDO1 Output     |                 |

|---------------|-----------------|-----------------|

|               | Lock Detect = 1 | Lock Detect = 0 |

| 00            | Recovered clock | Muted           |

| 01            | Reclocked data  | Bypassed data   |

| 10            | Muted           | Muted           |

| 11            | Bypassed data   | Bypassed data   |

## DATA RATE SELECTION

The LMH0376 can be configured for automatic or manual rate selection, which is controlled either by the RATE0 and RATE1 pins or through SPI register access. With default register settings, the RATE0 and RATE1 pins select the allowable rates at which the reclocker will lock, as shown in [Table 8](#). The RATE0 and RATE1 pins have internal pulldowns to select auto-rate detect by default.

**Table 8. Data Rate Selection**

| RATE1 | RATE0 | Selected Rate or Mode                                               |

|-------|-------|---------------------------------------------------------------------|

| 0     | 0     | Auto-rate detect – video rates (270, 1483.5, 1485, 2967, 2970 Mbps) |

| 0     | 1     | 270 Mbps                                                            |

| 1     | 0     | 1483.5/1485 Mbps, 2967/2970 Mbps                                    |

| 1     | 1     | 125 Mbps                                                            |

Upon entering SPI mode, the RATE pins will continue to select the allowable rates at which the reclocker will lock. Setting register 0x1D bit 0 (RATE\_SEL\_OV) overrides this selection and allows the rate selection to be controlled by register 0x1C bits 1:0 (RATE\_SEL) instead of the RATE pins. (This frees up the RATE0 and RATE1 pins to be used as GPIOs since they are no longer needed for rate selection.)

## EXTERNAL CLOCK REFERENCE OR REFERENCELESS MODE

The LMH0376 can operate with an external 27 MHz crystal or external clock signal as a timing reference input (external reference mode), or it can operate with no reference at all (referenceless mode). Providing an external 27 MHz reference allows the LMH0376 to distinguish between 2.97 Gbps and 2.97/1.001 Gbps, and between 1.485 Gbps and 1.485/1.001 Gbps. This reference could be a 27 MHz parallel resonant crystal and load network connected to the XTAL\_IN and XTAL\_OUT pins, or a 27 MHz 2.5V LVCMSO compatible clock signal connected to XTAL\_IN. The LMH0376 will automatically detect the 27 MHz reference clock and indicate its presence via register 0x41 bit 3 (REF\_CLK\_DET).

When using the LMH0376 in referenceless mode (i.e. no external 27 MHz crystal or reference clock applied), the XTAL\_IN pin must be connected to ground ( $V_{EE}$ ).

Parameters for a suitable crystal are given in [Table 9](#). A single crystal can be used as the 27 MHz reference for multiple reclockers by connecting the XTAL\_OUT output of one reclocker to the XTAL\_IN input of the next, propagating the 27 MHz reference signal through a cascade of reclockers.

**Table 9. Recommended Crystal Parameters**

| Parameter                   | Value                               |

|-----------------------------|-------------------------------------|

| Frequency                   | 27 MHz                              |

| Frequency Stability         | ±50 ppm at Recommended Drive Level  |

| Operating Mode              | Fundamental Mode, Parallel Resonant |

| Load Capacitance            | 20 pF                               |

| Shunt Capacitance           | 7 pF                                |

| Series Resistance           | 40Ω max                             |

| Recommended Drive Level     | 100 μW                              |

| Maximum Drive Level         | 250 μW                              |

| Operating Temperature Range | -10°C to +60°C                      |

## SD/HD INDICATION

The SD/HD output indicates whether the LMH0376 is processing SD or HD/3G data rates. It may be used to control the slew rate of another device such as the LMH0303 cable driver. This output is high when the data rate is 270 Mbps, and this output is low for all other data rates. When the PLL is not locked (the LOCK\_DETECT output is low), the SD/HD output is low.

## DATA RATE INDICATION

Details about the currently locked data rate can be obtained via the SPI. Register 0x03 bits 7:5 (RATE\_STATUS) indicate the locked data rate according to [Table 10](#).

The LMH0376 will detect the presence of a 27 MHz reference clock on the XTAL\_IN pin (register 0x41 bit 3, REF\_CLK\_DET, indicates the presence of the reference clock). When using an external reference, the LMH0376 can distinguish between 1.4835 and 1.485 Gbps, and between 2.967 and 2.97 Gbps. This is indicated in the RATE\_STATUS register bits. Also, when the reference clock is present, register 0x41 bit 2 (RATE\_1\_OV\_M) indicates if the detected data rate is a 1 over M rate (1.485/1.001 or 2.97/1.001 Gbps).

The GPIO pins can be configured as outputs to drive LEDs in order to indicate the locked rate (see the [GENERAL PURPOSE INPUT/OUTPUT PINS \(GPIO\[3:0\]\)](#) section).

**Table 10. Data Rate Indication (via Register 0x03 bits 7:5)**

| RATE_STATUS[2:0] | Data Rate Indication    |                      |

|------------------|-------------------------|----------------------|

|                  | External Reference Mode | Referenceless Mode   |

| 000              | 125 Mbps                | 125 Mbps             |

| 001              | 270 Mbps                | 270 Mbps             |

| 010              | 1.4835 Gbps             | N/A                  |

| 011              | 1.485 Gbps              | 1.485 or 1.4835 Gbps |

| 100              | 2.967 Gbps              | N/A                  |

| 101              | 2.97 Gbps               | 2.97 or 2.967 Gbps   |

| 111              | Unlocked                | Unlocked             |

## LOOP FILTER

The reclocker uses an external loop filter, which consists of a 56 nF capacitor connected between the LF1 and LF2 pins.

## ENABLE

The ENABLE input is used to enable or disable the LMH0376. Disabling the device powers down the output drivers and most of the internal circuitry in order to minimize the power dissipation. While in the disabled state, the SPI and input signal detection remain active. The external clock reference circuitry (XTAL\_IN and XTAL\_OUT) also remains active, allowing the 27 MHz reference clock signal to be generated and passed on to additional reclockers. ENABLE is active high and this pin has an internal pullup to enable the LMH0376 by default.

## GENERAL PURPOSE INPUT/OUTPUT PINS (GPIO[3:0])

The LMH0376 has four pins that can be configured through the SPI to provide direct access to certain register values via a dedicated pin. For example, if a particular application requires fast access to the condition of losing the input signal to the reclocker, the signal detect status bit could be routed directly to an external pin where it might generate an interrupt for the host processor. The GPIO pins can be configured as inputs or outputs. When used as inputs, the GPIO pins can be configured with a pullup resistor, a pulldown resistor, or no biasing at all.

The four GPIO pins, pins 45-48, originally function as the RATE0, RATE1, SEL0, and SEL1 inputs, respectively. To use these pins as GPIOs, their default functions must first be overridden. Setting register 0x1D bit 0 (RATE\_SEL\_OV) overrides the use of pins 45 and 46 as RATE0 and RATE1 and allows the rate selection to be controlled by register 0x1C bits 1:0 (RATE\_SEL), freeing pins 45 and 46 to be used as GPIO0 and GPIO1. Setting register 0x1E bit 7 (INPUT\_SEL\_OV) overrides the use of pins 47 and 48 as SEL0 and SEL1 and allows the input selection to be controlled by register 0x20 bits 2:1 (IN\_CH\_SEL), freeing pins 47 and 48 to be used as GPIO2 and GPIO3.

The four GPIO pins are controlled by registers 0x04 (GPIO0 Control), 0x05 (GPIO1 Control), 0x06 (GPIO2 Control), and 0x07 (GPIO3 Control).

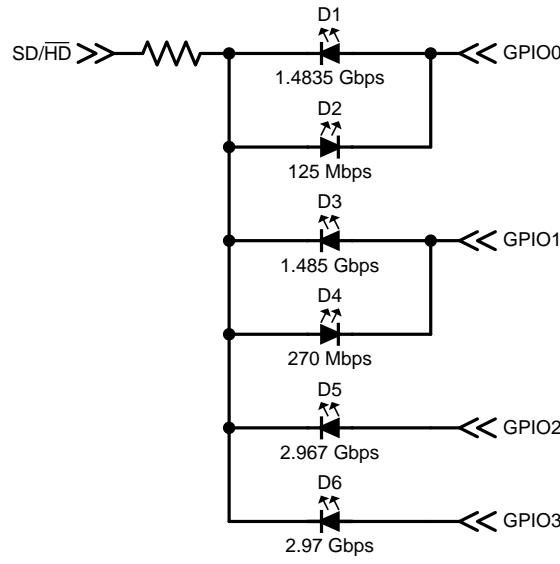

For each of these GPIO control registers, bits 7:4 control the output mode, and can select between the following: general purpose output, signal detect for a particular input channel, and the rate detect. When configured as the rate detect, the four GPIO pins and the SD/HD pin can be used to drive LEDs to indicate the locked rate as shown in [Figure 6](#) and [Table 11](#). When the GPIO is configured as an input, this mode selection has no effect.

Bits 3 and 2 select either a pullup or pulldown resistor for when the GPIO is operating as an input. Do not enable the pullup and pulldown resistor simultaneously. When the GPIO is operating as an output, neither the pullup nor the pulldown resistor should be enabled.

Bits 1 and 0 enable or disable the input and output buffers. If the GPIO is used as an output, the output buffer must be enabled and the input buffer must be disabled. If the GPIO is used as an input, the input buffer must be enabled and the output must be disabled. Do not enable both the input and output buffers simultaneously.

If the GPIO pins are configured as inputs, then the input values on each of the four GPIOs can be monitored via register 0x03 bits 3:0 (GPIO\_IN\_VAL). If the GPIO pins are configured as general purpose output pins, then the values written to register 0x08 bits 3:0 (GPIO\_OUT\_VAL) will appear on the respective GPIO pins.

**Figure 6. GPIO Data Rate Indication**

**Table 11. GPIO Data Rate Indication**

| SD/HD | GPIO0 | GPIO1 | GPIO2 | GPIO3 | LED On | Date Rate Indication                                    |

|-------|-------|-------|-------|-------|--------|---------------------------------------------------------|

| 0     | 0     | 0     | 0     | 0     | None   | Unlocked                                                |

| 1     | 0     | 1     | 1     | 1     | D2     | 125 Mbps                                                |

| 1     | 1     | 0     | 1     | 1     | D4     | 270 Mbps                                                |

| 0     | 1     | 0     | 0     | 0     | D1     | 1.4835 Gbps (external reference mode only)              |

| 0     | 0     | 1     | 0     | 0     | D3     | 1.485 Gbps (includes 1.4835 Gbps in referenceless mode) |

| 0     | 0     | 0     | 1     | 0     | D5     | 2.967 Gbps (external reference mode only)               |

| 0     | 0     | 0     | 0     | 1     | D6     | 2.97 Gbps (includes 2.967 Gbps in referenceless mode)   |

## EYE OPENING MONITOR (EOM)

The LMH0376 includes an eye opening monitor for analyzing the quality of the incoming signal, accessible via the SPI. The eye opening monitor can be used on any one of the four serial inputs. It analyzes the eye opening with 64 horizontal time points and 64 vertical voltage points, with 6-bit phase DAC control for the horizontal coordinates and 6-bit voltage DAC control for the vertical coordinates.

The eye opening monitor can be used to measure the eye shape using either the normal or fast EOM modes. It can also be used to quickly determine the width and height of the eye opening.

### Eye Opening Monitor Configuration

For all modes, the eye opening monitor must first be enabled by clearing register 0x14 bit 4 (EOM\_PD).

The LMH0376 must be locked to the incoming data rate for eye opening monitor operation.

The input signal to the eye opening monitor will be the same as the primary selected input unless register 0x14 bit 5 (MUX2\_OV) is set to override this selection. If this override bit is set, the input to the eye opening monitor is selected independently of the primary input selection by register 0x18 bits 1:0 (MUX2\_SEL). Note that if the input to the eye opening monitor is selected independently in this manner, then this signal must be the same data rate as the signal selected for the primary input. The input signal to the eye opening monitor is equalized by default, but register 0x14 bit 1 (MUX2\_EQ\_SEL) can be used to select between non-equalized or equalized data.

The output eye monitor is configured for HD input signals by default. When analyzing SD input signals, it is recommended to set register 0x11 bit 2 (EOM\_SEL\_SD) to enable SD eye monitor mode. For 3G input signals, it is recommended to set register 0x22 bit 6 (EOM\_SEL\_3G) to enable 3G eye monitor mode.

The amount of time during which the eye opening monitor accumulates eye opening data can be set by the value in register 0x29 (EOM\_TIMER). In general, the greater this value, the longer the accumulation time.

### Normal Eye Opening Monitor Mode

In normal eye opening monitor mode, the external controller has full control over the horizontal and vertical coordinates, and must enable the measurement for each point. This provides the option to do a more coarse measurement.

The procedure for normal EOM mode is as follows:

1. Enable the eye opening monitor by clearing register 0x14 bit 4 (EOM\_PD).

2. Enable manual operation of the phase DAC and voltage DAC by setting register 0x22 bit 7 (EOM\_OV).

3. Write the 6-bit phase DAC value to register 0x22 bits 5:0 (EOM\_PDAC), and write the 6-bit voltage DAC value to register 0x23 bits 5:0 (EOM\_VDAC).

4. Enable the EOM counter by setting register 0x24 bit 0 (EOM\_START), and poll for completion of the measurement by reading this bit until it has cleared itself.

5. Read register 0x25 (EOM\_COUNT[15:8]) to get the most significant byte and register 0x26 (EOM\_COUNT[7:0]) to get the least significant byte of the hits counter, and store this value.

6. Repeat steps 3-5 for the remaining desired phase DAC and voltage DAC points. (In a typical application, steps 2-4 will be repeated by sweeping through every voltage DAC setting at each phase DAC setting.)

## Fast Eye Opening Monitor Mode

In fast eye opening monitor mode, the eye opening monitor sweeps through all 4096 phase and voltage DAC settings autonomously. A new measurement at the next coordinate is automatically triggered when the current 16-bit count is ready and has been read. The full 64-by-64 point dimensions are used in this mode.

The procedure for fast EOM mode is as follows:

1. Enable the eye opening monitor by clearing register 0x14 bit 4 (EOM\_PD).

2. Enable fast EOM mode by setting register 0x24 bit 7 (FAST\_EOM).

3. Read register 0x26 (EOM\_COUNT[7:0]) to clear the initial invalid data and start the EOM counter, and poll for completion of the measurement by reading register 0x24 bit 0 (EOM\_START) until it has cleared itself.

4. Read register 0x26 again to load the hits counter for read back and start the next measurement.

5. Poll for completion of the measurement by reading register 0x24 bit 0 (EOM\_START) until it has cleared itself.

6. Read register 0x25 (EOM\_COUNT[15:8]) to get the most significant byte and register 0x26 (EOM\_COUNT[7:0]) to get the least significant byte of the hits counter, and store this value. (Reading register 0x26 will also automatically step to the next point in the EOM graph and initiate the measurement.)

7. Repeat steps 5-6 a total of 4096 times.

## Measuring Horizontal and Vertical Eye Openings

The eye opening monitor can quickly detect and report the horizontal eye opening (HEO) and vertical eye opening (VEO). The eye opening monitor first sweeps its variable-phase clock through one unit interval with the comparison voltage set to the midpoint of the signal. This determines the midpoint of the horizontal eye opening. The eye opening monitor then sets its variable-phase clock to the midpoint of the horizontal eye opening and sweeps its comparison voltage. These two measurements determine the horizontal and vertical eye openings.

The procedure to measure the horizontal and vertical eye openings is as follows:

1. Enable the eye opening monitor by clearing register 0x14 bit 4 (EOM\_PD).

2. Enable the measurement by setting register 0x24 bit 1 (GET\_HEO\_VEO), and wait for completion by reading this bit until it has cleared itself.

3. Ensure no errors have occurred by verifying that register 0x24 bits 4:2 (VEO\_MAX\_ERR, NO\_OPENING\_ERR, and NO\_HITS\_ERR) are all cleared.

4. Read the horizontal eye opening in register 0x2A (HEO) and the vertical eye opening in register 0x2B (VEO).

## SPI REGISTER ACCESS

Setting SPI\_EN high enables the optional SPI register access mode. The LMH0376 supports SPI daisy-chaining among an unlimited number of LMH0376 devices. With SPI\_EN set low, the device operates in pin mode and is footprint compatible with the LMH0356, LMH0056, and LMH0036.

Table 12 shows the SPI register table for the LMH0376. The LMH0376 provides over 50 accessible registers, which are divided into over 100 bit fields. When writing to the device registers, it is important to ensure that reserved register values are not changed. In configuring the LMH0376, it is often required to write to a bit field that makes up only part of a register value while leaving the remainder of the register value unchanged. The procedure for accomplishing this is to read in the current value of the register to be written, modify only the desired bits in this value, and write the modified value back to the register.

When power is first applied to the LMH0376, the host must wait 500 ms to ensure the power-on reset has completed before initiating SPI transactions.

### SPI Transaction Overview

Each SPI transaction to a single device is 16-bits long. The transaction is initiated by driving  $\overline{SS}$  low, and completed by returning  $\overline{SS}$  high. The 16-bit MOSI payload consists of the read/write command ("1" for reads and "0" for writes), the seven address bits of the device register (MSB first), and the eight data bits (MSB first). The LMH0376 MOSI input data is latched on the rising edge of SCK, and the MISO output data is sourced on the falling edge of SCK.

In order to facilitate daisy-chaining, the prior SPI command, address, and data are shifted out on the MISO output as the current command, address, and data are shifted in on the MOSI input. For SPI writes, the MISO output is typically ignored as "Don't Care" data. For SPI reads, the MISO output provides the requested read data (after 16 periods of SCK). The MISO output is active when  $\overline{SS}$  low, and tri-stated when  $\overline{SS}$  is high.

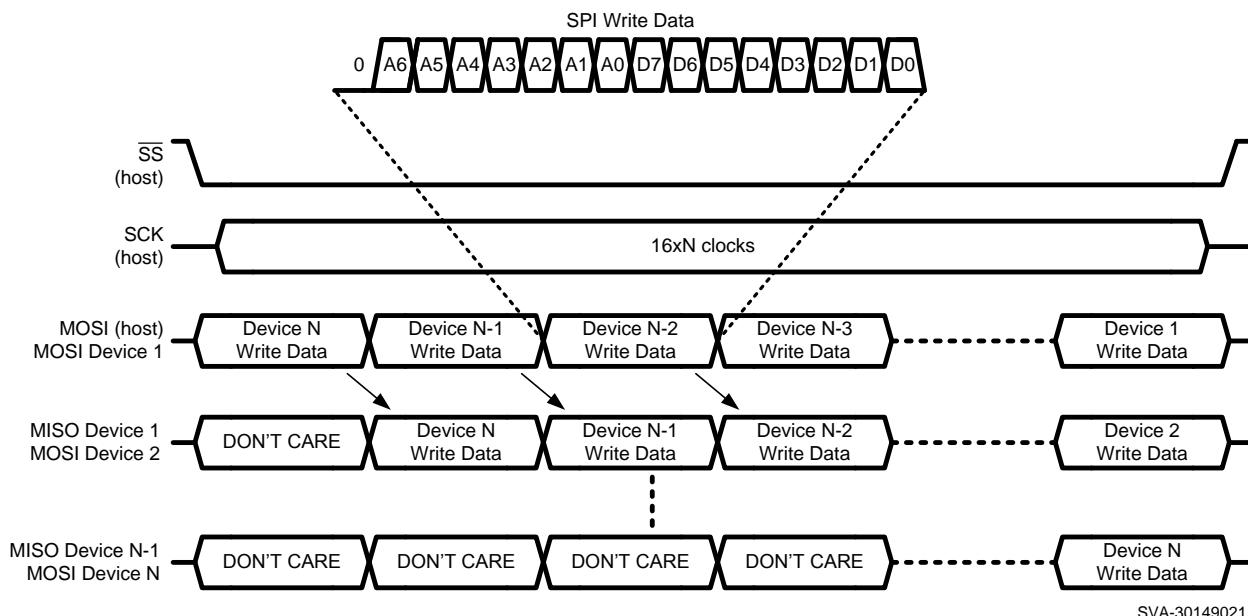

### SPI Write

The SPI write is shown in Figure 4. The SPI write is 16 bits long. The 16-bit MOSI payload consists of a "0" (write command), seven address bits, and eight data bits. The  $\overline{SS}$  signal is driven low, and the 16 bits are sent to the LMH0376's MOSI input. After the SPI write,  $\overline{SS}$  must return high. The prior SPI command, address, and data shifted out on the MISO output during the SPI write is shown as "Don't Care" on the MISO output in Figure 4.

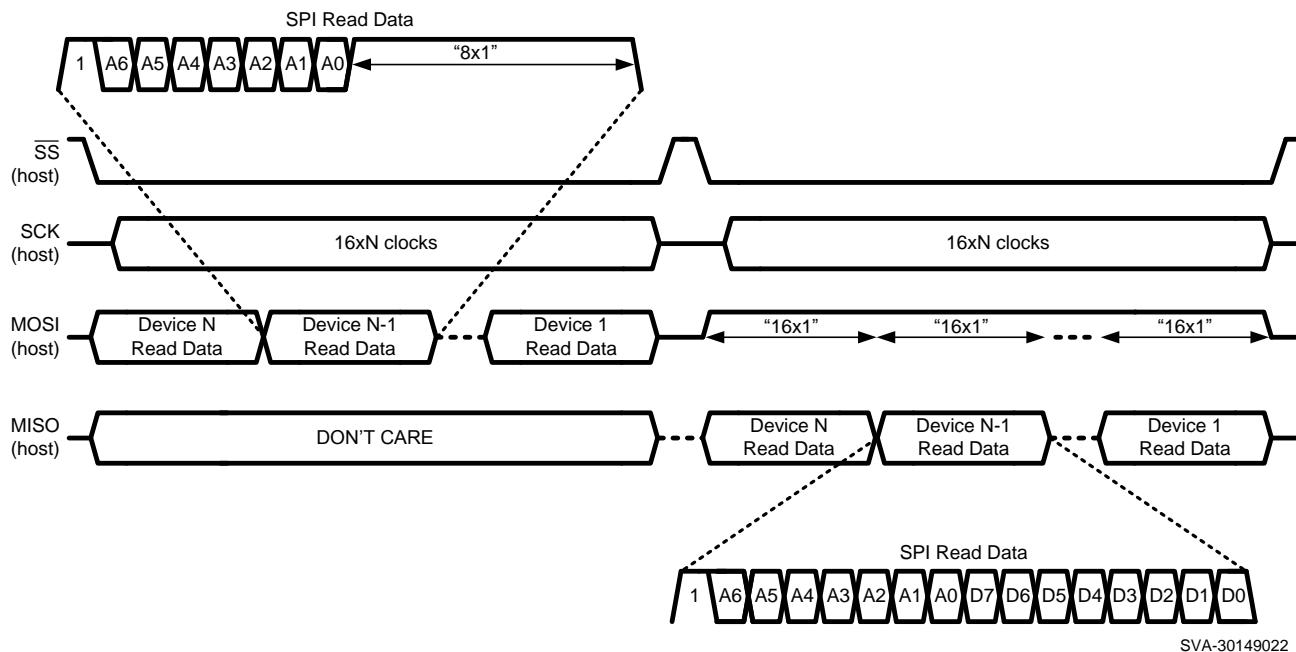

### SPI Read

The SPI read is shown in Figure 5. The SPI read is 32 bits long, consisting of a 16-bit read transaction followed by a 16-bit dummy read transaction to shift out the read data on the MISO output. The first 16-bit MOSI payload consists of a "1" (read command), seven address bits, and eight "1"s which are ignored. The second 16-bit MOSI payload consists of 16 "1"s which are ignored but necessary in order to shift out the requested read data on the MISO output. The  $\overline{SS}$  signal is driven low, and the first 16 bits are sent to the LMH0376's MOSI input. The prior SPI command, address, and data are shifted out on the MISO output during the first 16-bit transaction, and are typically ignored (this is shown as "Don't Care" on the MISO output in Figure 5).  $\overline{SS}$  must return high and then is driven low again before the second 16 bits (all "1"s) are sent to the LMH0376's MOSI input. Once again, the prior SPI command, address, and data are shifted out on the MISO output, but this data now includes the requested read data. The read data is available on the MISO output during the second 8 bits of the 16-bit dummy read transaction, as shown by D7-D0 in Figure 5.

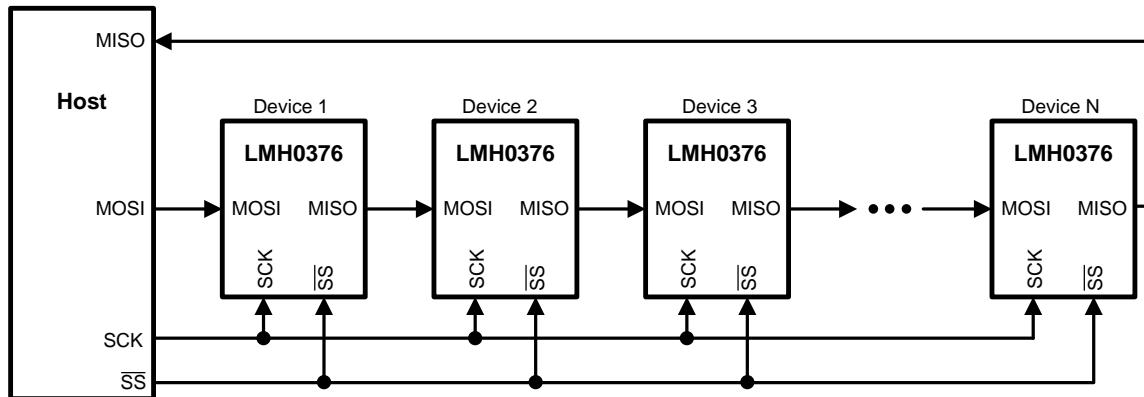

### SPI Daisy-Chain Operation

The LMH0376 SPI controller supports daisy-chaining the serial data between an unlimited number of LMH0376 devices. Each LMH0376 device is directly connected to the SCK and  $\overline{SS}$  pins on the host. However, only the first LMH0376 device in the chain is connected to the host's MOSI pin, and only the last device in the chain is connected to the host's MISO pin. The MISO pin of each intermediate LMH0376 device in the chain is connected to the MOSI pin of the next LMH0376 device, creating a serial shift register. This daisy-chain architecture is shown in Figure 7.

SVA-30149020

**Figure 7. SPI Daisy Chain System Architecture**

In a daisy-chain configuration of  $N$  LMH0376 devices, the host conceptually sees a shift register of length  $16 \times N$ . Therefore the length of SPI transactions (as previously described) is  $16 \times N$  bits, and  $\overline{SS}$  must be asserted for  $16 \times N$  clock cycles for each SPI transaction.

### SPI Daisy-Chain Write

Figure 8 shows the SPI daisy-chain write for a daisy-chain of  $N$  devices. The  $\overline{SS}$  signal is driven low and SCK is toggled for  $16 \times N$  clocks. The  $16 \times N$  bit MOSI payload (sent to Device 1 in the daisy-chain) consists of the 16-bit SPI write data for Device  $N$  (the last device in the chain), followed by the write data for Device  $N-1$ , Device  $N-2$ , etc., ending with the write data for Device 1 (the first device in the chain). The 16-bit SPI write data for each device consists of a “0” (write command), seven address bits, and eight data bits. After the SPI daisy-chain write,  $SS$  must return high and then the write occurs for all devices in the daisy-chain.

**Figure 8. SPI Daisy-Chain Write**

## SPI Daisy-Chain Read

Figure 9 shows the SPI daisy-chain read for a daisy-chain of  $N$  devices. The SPI daisy-chain read is  $32 \times N$  bits long, consisting of  $16 \times N$  bits for the read transaction followed by  $16 \times N$  bits for the dummy read transaction (all “1”s) to shift out the read data on the MISO output. The  $\overline{SS}$  signal is driven low and SCK is toggled for  $16 \times N$  clocks. The first  $16 \times N$  bit MOSI payload (sent to Device 1 in the daisy-chain) consists of the 16-bit SPI read data for Device  $N$  (the last device in the chain), followed by the read data for Device  $N-1$ , Device  $N-2$ , etc., ending with the read data for Device 1 (the first device in the chain). The 16-bit SPI read data for each device consists of a “1” (read command), seven address bits, and eight “1”s (which are ignored). After the first  $16 \times N$  bit transaction,  $\overline{SS}$  must return high (to latch the data) and then is driven low again before the second  $16 \times N$  bit transaction of all “1”s is sent to the MOSI input. The requested read data is shifted out on MISO starting with the data for Device  $N$  and ending with the data for Device 1. After this transaction,  $\overline{SS}$  must return high.

**Figure 9. SPI Daisy-Chain Read**

## SPI Daisy-Chain Read and Write Example

The following example further clarifies LMH0376 SPI daisy-chain operation. Assume a daisy-chain of three LMH0376 devices (Device 1, Device 2, and Device 3), with Device 1 as the first device in the chain and Device 3 as the last device in the chain, as shown by the first three devices in Figure 7. Since there are three devices in the daisy-chain, each SPI transaction is 48-bits long. This example shows an SPI operation combining SPI reads and writes in order to accomplish the following three tasks:

1. Write 0x02 to register 0x12 of Device 1 in order to set the output swing of both SDO0 and SDO1 to 400 mV<sub>P-P</sub>.

2. Read the contents of register 0x01 of Device 2.

3. Write 0x50 to register 0x13 of Device 3 in order to set the output de-emphasis of both SDO0 and SDO1 to 3 dB.

Figure 10 shows the two 48-bit SPI transactions required to complete these tasks (the bits are shifted in left to right).

| 48-bit SPI Transaction #1 |      |      |            |      |      |            |      |      | 48-bit SPI Transaction #2 |      |      |            |      |      |             |      |      |      |

|---------------------------|------|------|------------|------|------|------------|------|------|---------------------------|------|------|------------|------|------|-------------|------|------|------|

| (Device 3)                |      |      | (Device 2) |      |      | (Device 1) |      |      | (Device 3)                |      |      | (Device 2) |      |      | (Device 1)  |      |      |      |

| R/W                       | Addr | Data | R/W        | Addr | Data | R/W        | Addr | Data | R/W                       | Addr | Data | R/W        | Addr | Data | R/W         | Addr | Data |      |

| MOSI<br>(host)            | 0    | 0x12 | 0x02       | 1    | 0x01 | 0xFF       | 0    | 0x13 | 0x50                      | 1    | 0x7F | 0xFF       | 1    | 0x7F | 0xFF        | 1    | 0x7F | 0xFF |

| MISO<br>(host)            | X    | XX   | XX         | X    | XX   | XX         | X    | XX   | XX                        | 0    | 0x12 | 0x02       | 1    | 0x01 | <b>0x20</b> | 0    | 0x13 | 0x50 |

SVA-30149023

**Figure 10. SPI Daisy-Chain Read and Write Example**

The following occurs at the end of the first transaction:

1. Write 0x02 to register 0x12 of Device 1.

2. Latch the data from register 0x01 of Device 2.

3. Write 0x50 to register 0x13 of Device 3.

In the second transaction, three dummy reads (each consisting of 16 “1”s) are shifted in, and the read data from Device 2 (with value 0x20) appears on MISO in the 25th through 32nd clock cycles.

### SPI Daisy-Chain Length Detection

A useful operation for the host may be to detect the length of the daisy-chain. This is a simple matter of shifting in a series of dummy reads with a known data value (such as 0x5A). For an SPI daisy-chain of N LMH0376 devices, the known data value will appear on the host's MISO pin after N+1 writes. Assuming a daisy-chain of three LMH0376 devices, the result of this operation is shown in [Figure 11](#).

| R/W Addr Data R/W Addr Data R/W Addr Data R/W Addr Data |      |      |            |      |      |            |      |      | R/W Addr Data R/W Addr Data R/W Addr Data R/W Addr Data |      |             |             |      |      |            |      |      |      |

|---------------------------------------------------------|------|------|------------|------|------|------------|------|------|---------------------------------------------------------|------|-------------|-------------|------|------|------------|------|------|------|

| (Device 3)                                              |      |      | (Device 2) |      |      | (Device 1) |      |      | (Device 3)                                              |      |             | (Device 2)  |      |      | (Device 1) |      |      |      |

| R/W                                                     | Addr | Data | R/W        | Addr | Data | R/W        | Addr | Data | R/W                                                     | Addr | Data        | R/W         | Addr | Data | R/W        | Addr | Data |      |

| MOSI<br>(host)                                          | 1    | 0x7F | 0x5A       | 1    | 0x7F | 0x5A       | 1    | 0x7F | 0x5A                                                    | 1    | 0x7F        | 0x5A        | 1    | 0x7F | 0x5A       | 1    | 0x7F | 0x5A |

| MISO<br>(host)                                          | X    | XX   | XX         | X    | XX   | XX         | X    | XX   | XX                                                      | 1    | <b>0x7F</b> | <b>0x5A</b> |      |      |            |      |      |      |

SVA-30149024

**Figure 11. SPI Daisy-Chain Length Detection**

## APPLICATION INFORMATION

## APPLICATION CIRCUIT (PIN MODE)

Figure 12 shows the typical application circuit for the LMH0376 in pin mode.

**Figure 12. Application Circuit (Pin Mode)**

## POWER SUPPLY RECOMMENDATIONS

The LMH0376 requires a single 2.5V power supply. Circuit board layout and stack-up for the LMH0376 should be optimized to minimize noise to the device from switching power supplies or nearby high speed devices.

It is recommended to provide power to the LMH0376 using a linear regulator. If a switching regulator used, the power supply filtering must be adequate to filter the switching noise.

The following guidelines are recommended for supplying power to the LMH0376:

- Bypass/decouple each supply pin with a high frequency ceramic bypass capacitor (0.01  $\mu$ F to 0.1  $\mu$ F) placed as close as possible to the pin.

- Deploy nearby bulk capacitors (2.2  $\mu$ F to 22  $\mu$ F) for additional power supply filtering.

- Wherever possible, use two vias for each connection to internal power and ground planes to minimize the via parasitics.

- Use the capacitance of the power-ground system for extra bypassing by using thin dielectrics between the power and ground planes.

- Route high speed differential lines away from the device power pins to avoid coupling noise into the power supply lines.

## LOOP FILTER RECOMMENDATIONS

The LMH0376 uses a 56 nF capacitor for the loop filter, connected between the LF1 and LF2 pins. Alternately, a 47 nF capacitor may be used in place of this 56 nF capacitor.

The loop filter layout should be optimized to minimize coupling between the loop filters of different devices and also to avoid noise pick up from other signals. The external loop filter capacitor should be connected as close to the device pins as possible and with maximum isolation from other signals.

It is important to keep multiple reclockers as isolated from one another as possible to avoid any interaction between the loop filters or other sensitive circuits.

The following guidelines are recommended for the loop filter layout:

- Keep the loop filter traces as short as possible; place the loop filter capacitor parallel to the device to allow for the shortest trace interconnect.

- Avoid using vias between the loop filter pins and the external loop filter capacitor.

- Remove the ground plane underneath the LF1 and LF2 pins and also in the area underneath the loop filter capacitor to increase isolation.

- Avoid running traces under the loop filter area as much as possible to increase isolation.

- When using multiple devices, place the devices as far apart from one another as possible. Avoid placing the loop filter pins of different devices next to each other.

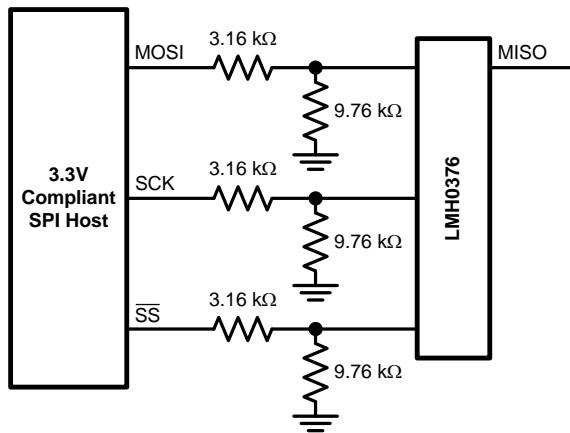

## INPUT INTERFACING RECOMMENDATIONS