DS90C189-Q1

ZHCSI69A - JULY 2018-REVISED AUGUST 2018

## DS90C189-Q1 低功耗、1.8V RGB 到 Open LDI (LVDS) 桥

## 1 特性

- 符合面向汽车应用的 AEC-Q100 标准, 具有 以下 规格:

- 器件温度 2 级: -40℃ 至 +105℃ 环境运行温度

范围

- 器件 HBM ESD 分类等级 ±8kV

- 器件 CDM ESD 分类等级 ±750V

- 185MHz 频率下的典型功耗为 150mW (SIDO 模式)

- 驱动 QXGA 和 WQXGA 类显示器

- 两种工作模式:

- 单输入像素、单输出像素 (SISO): 最大频率为 105MHz

- 单输入像素、双输出像素 (SIDO): 最大频率为 185MHz

- 支持 24 位 RGB

- 支持 3D+C、4D+C、6D+C、6D+2C、8D+C 和 8D+2C LVDS 配置

- 与 FPD-Link 器件兼容

- 由 1.8V 单电源供电

- 直接与 1.8V LVCMOS 连接

- 睡眠模式下的功耗低于 10mW

- 与扩频时钟兼容

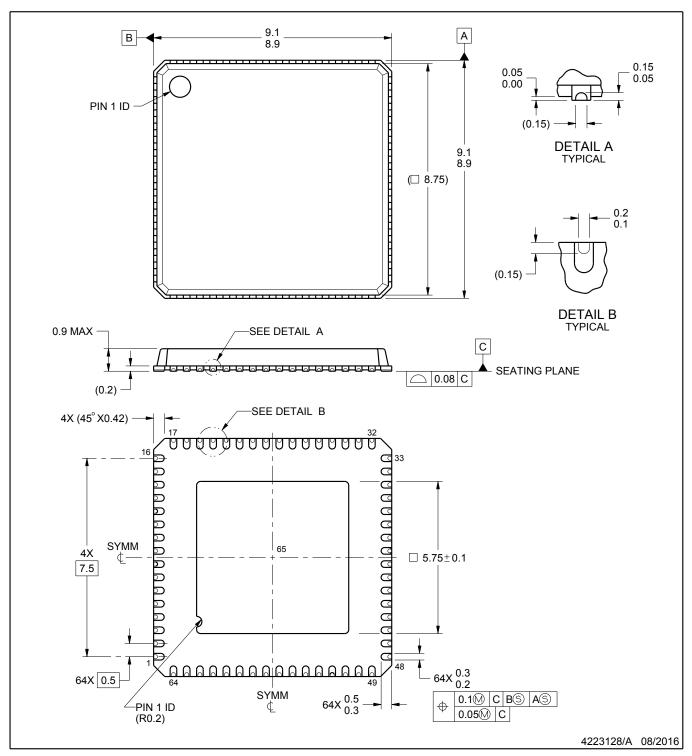

- 小型 9mm × 9mm × 0.9mm 64 引脚 VQFN 封装

#### 2 应用

- 摄像头监控系统 (CMS)

- 汽车音响主机

- 智能后视镜

- 仪表组

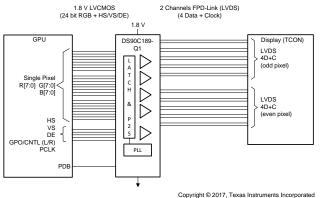

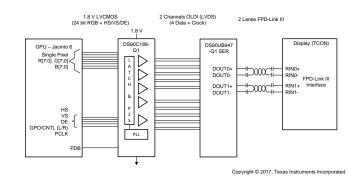

#### 4 典型应用图

#### 3 说明

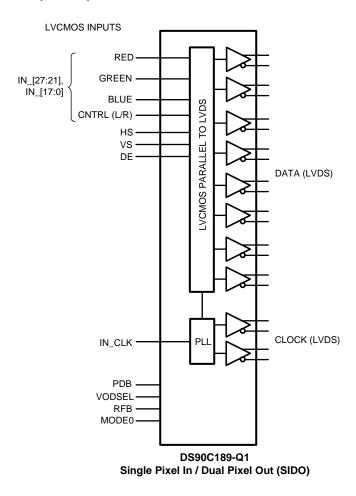

DS90C189-Q1 是一款低功耗桥,该器件用于汽车 应用,能够减小主机 GPU 与显示器之间的 RGB 接口的尺寸。

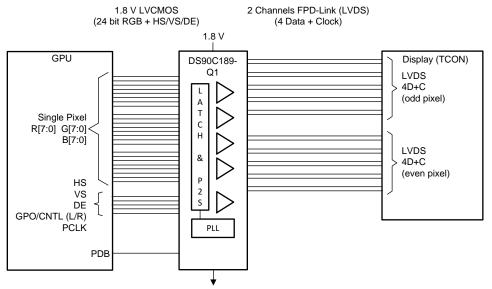

DS90C189-Q1 桥旨在支持主机与平板显示器之间频率为 60Hz、分辨率高达 QXGA (2048x1536) 的单像素数据传输。该发送器可将高达 24 位(单像素 24 位颜色)的 1.8V LVCMOS 数据转换成双通道 4 数据 + 时钟 (4D+C) 宽度更低的接口 LVDS 兼容数据流。

#### DS90C189-Q1 支持 2 种工作模式。

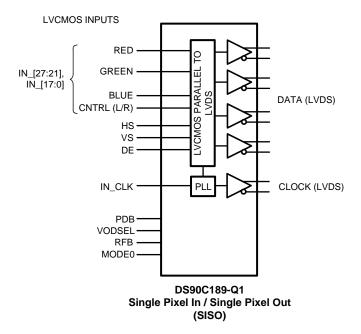

- 在单输入像素/单输出像素模式下,该器件能够以 60Hz 的频率驱动高达 SXGA+ (1400x1050) 的分 辨率。在该模式下,该器件可以将一组 24 位的 RGB 数据转换成单通道 4D+C LVDS 数据流。

- 在单输入像素/双输出像素模式下,该器件能够以60Hz的频率驱动高达WUXGA+(1920x1440)的分辨率。在该配置下,该器件可以提供单像素到双像素的转换,将一组24位RGB数据转换成双通道4D+CLVDS数据流,其频率是像素时钟频率的一半。

对于所有模式,该器件都支持 24bpp 颜色。

DS90C189-Q1 采用小型 64 引脚 QFN 封装并 采用 1.8V 单电源,以实现最低的功率耗散。

#### 器件信息(1)

|             | BB 11 1B 10. |                   |

|-------------|--------------|-------------------|

| 器件型号        | 封装           | 封装尺寸 (标称值)        |

| DS90C189-Q1 | VQFN (64)    | 9.00 mm × 9.00 mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

Copyright © 2017, Texas Instruments Incorporate

|                                 | 目表                                         | 录                   |                        |      |

|---------------------------------|--------------------------------------------|---------------------|------------------------|------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | 特性                                         | 9<br>10<br>11<br>12 | 10.1 Power Up Sequence |      |

| <b>5</b> 作                      | 多订历史记录                                     |                     |                        |      |

| Chan                            | ges from Original (May 2018) to Revision A |                     |                        | Page |

将器件状态从"预告信息"更改成了"生产数据".......1

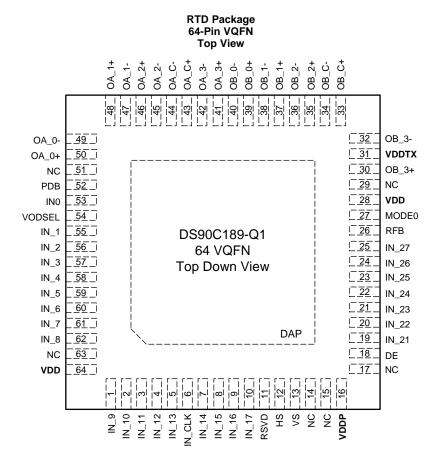

## 6 Pin Configuration and Functions

**DS90C189 Pin Descriptions**

|                                                                | DS90C189 Pin Descriptions               |     |                                                                                                                        |  |  |

|----------------------------------------------------------------|-----------------------------------------|-----|------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                           | NO.                                     | I/O | DESCRIPTION                                                                                                            |  |  |

| 1.8-V LVCMOS VID                                               | EO INPUTS                               |     |                                                                                                                        |  |  |

| IN_[27:21],<br>IN_[17:14],<br>IN_[13:9],<br>IN_[8:1]<br>IN_[0] | 25-19,<br>10-7,<br>5-1,<br>62-55,<br>53 | I   | Data Inputs Typically consists of 8 Red, 8 Green, 8 Blue and a general purpose or L/R control bit. Includes pull down. |  |  |

| HS,<br>VS,<br>DE                                               | 12,<br>13,<br>18                        | I   | Video Control Signal Inputs -<br>HS = Horizontal Sync, VS = Vertical SYNC, and DE = Data Enable                        |  |  |

| IN_CLK                                                         | 6                                       | 1   | Pixel Input Clock Includes pull down.                                                                                  |  |  |

| 1.8-V LVCMOS CO                                                | NTROL INPUTS                            |     |                                                                                                                        |  |  |

| MODE0                                                          | 27                                      | I   | Mode Control Input (MODE0) - 0= Single In / Single Out 1= Single In / Dual Out Includes pull down.                     |  |  |

| RFB                                                            | 26                                      | I   | Rising / Falling Clock Edge Select Input - 0 = Falling Edge 1 = Rising Edge Includes pull down.                        |  |  |

| PDB                                                            | 52                                      | I   | Power Down (Sleep) Control Input - 0 = Sleep (Power Down mode) 1 = Device Active (enabled) Includes pull down.         |  |  |

| VODSEL                                                         | 54                                      | I   | VOD Level Select Input - 0 = Low swing 1 = Normal swing Includes pull down.                                            |  |  |

| N/C                                                            | 14, 15, 17, 29, 51,<br>63               | 1   | No Connect Pin – Leave Open                                                                                            |  |  |

| RSVD                                                           | 11                                      | I   | Reserved – Tie to Ground.                                                                                              |  |  |

| LVDS OUTPUTS                                                   | ,                                       |     |                                                                                                                        |  |  |

| OA_C+<br>OA_C-                                                 | 43<br>44                                | 0   | Channel A LVDS Output Clock – Expects 100 Ω termination.                                                               |  |  |

| OA_[0]+,<br>OA_[0]-                                            | 50<br>49                                | 0   | Channel A LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OA_[1]+,<br>OA_[1]-                                            | 48<br>47                                | 0   | Channel A LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OA_[2]+,<br>OA_[2]-                                            | 46<br>45                                | 0   | Channel A LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OA_[3]+,<br>OA_[3]-                                            | 41<br>42                                | 0   | Channel A LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OB_C+,<br>OB_C-                                                | 33<br>34                                | 0   | Channel B LVDS Output Clock – Expects 100 Ω termination.                                                               |  |  |

| OB_[0]+,<br>OB_[0]-                                            | 39<br>40                                | 0   | Channel B LVDS Output Data – Expects 100 $\Omega$ termination.                                                         |  |  |

| OB_[1]+,<br>OB_[1]-                                            | 37<br>38                                | 0   | Channel B LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OB_[2]+,<br>OB_[2]-                                            | 35<br>36                                | 0   | Channel B LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| OB_[3]+,<br>OB_[3]-                                            | 30<br>32                                | 0   | Channel B LVDS Output Data – Expects 100 Ω termination.                                                                |  |  |

| POWER AND GROUND                                               |                                         |     |                                                                                                                        |  |  |

| $V_{DDTX}$                                                     | 31                                      | Р   | Power supply for LVDS Drivers, 1.8 V.                                                                                  |  |  |

| $V_{DD}$                                                       | 28, 64                                  | Р   | Power supply pin for core, 1.8 V.                                                                                      |  |  |

| $V_{DDP}$                                                      | 16                                      | Р   | Power supply pin for PLL, 1.8 V.                                                                                       |  |  |

| DAP                                                            | DAP                                     | G   | Connect DAP to Ground plane.                                                                                           |  |  |

## 7 Specifications

#### 7.1 Absolute Maximum Ratings

See (1)

|                                         | MIN  | MAX        | UNIT |

|-----------------------------------------|------|------------|------|

| Supply Voltage (V <sub>DD</sub> )       | -0.3 | 2.5        | V    |

| LVCMOS Input Voltage                    | -0.3 | VDD + 0.3  | V    |

| LVDS Driver Output Voltage              | -0.3 | 3.6        | V    |

| LVDS Output Short-Circuit Duration      | С    | Continuous |      |

| Junction Temperature                    |      | 150        | °C   |

| Storage Temperature (T <sub>stg</sub> ) | -65  | 150        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or anyother conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 7.2 ESD Ratings

|                                            |                         |                                                                 | VALUE | UNIT |

|--------------------------------------------|-------------------------|-----------------------------------------------------------------|-------|------|

| V                                          | Flootrootatia diaaharaa | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001              | ±8000 | V    |

| V <sub>(ESD)</sub> Electrostatic discharge |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 | ±750  | V    |

## 7.3 Recommended Operating Conditions

|                                                 | MIN  | NOM  | MAX  | UNIT       |

|-------------------------------------------------|------|------|------|------------|

| Supply Voltage                                  | 1.71 | 1.80 | 1.89 | V          |

| Operating Free Air Temperature (T <sub>A)</sub> | -40  | +25  | +105 | °C         |

| Differential Load Impedance                     | 80   | 100  | 120  | Ω          |

| Supply Noise Voltage                            |      |      | <90  | $mV_{p-p}$ |

#### 7.4 Thermal Information

|                      |                                                           | DS90C189-Q1 |      |

|----------------------|-----------------------------------------------------------|-------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                             | RTD (VQFN)  | UNIT |

|                      |                                                           | 64 PINS     |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance AEC-Q100 Qualified | 23.8        | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance                 | 12.5        | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance                      | 7.9         | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter                | 0.2         | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter              | 7.9         | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance              | 1.0         | °C/W |

For more information about traditional and new thermalmetrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 7.5 Electrical Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

|                  | PARAMETER                                                     | TEST C                                                                    | CONDITIONS                                        | MIN                 | TYP           | MAX                 | UNIT              |

|------------------|---------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------|---------------------|---------------|---------------------|-------------------|

| LVCMOS           | DC SPECIFICATIONS                                             |                                                                           |                                                   | •                   |               |                     |                   |

| V <sub>IH</sub>  | High Level Input Voltage                                      |                                                                           |                                                   | 0.66V <sub>DD</sub> |               | $V_{DD}$            | V                 |

| V <sub>IL</sub>  | Low Level Input Voltage                                       |                                                                           |                                                   | GND                 |               | 0.35V <sub>DD</sub> | V                 |

| I <sub>IN</sub>  | Input Current                                                 | $V_{IN} = 0V \text{ or } V_{DD} = 1$                                      | 1.71 V to 1.89 V                                  | - 10                | ±1            | +10                 | μA                |

| LVDS DF          | RIVER DC SPECIFICATIONS                                       |                                                                           |                                                   |                     |               |                     |                   |

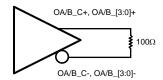

| V <sub>OD</sub>  | Differential Output Voltage                                   | $R_L = 100\Omega$                                                         | VODSEL = V <sub>DD</sub>                          | 160<br>(320)        | 340<br>(680)  | 500<br>(1000)       | $mV$ $(mV_{P-P})$ |

| VOD .            | Differential Output voltage                                   | See 图 3                                                                   | VODSEL = V <sub>GND</sub>                         | 110<br>(220)        | 220<br>(440)  | 400<br>(800)        | $mV$ $(mV_{P-P})$ |

| $\Delta V_{OD}$  | Change in V <sub>OD</sub> between Complimentary Output States | $R_L = 100\Omega$<br>See 🛭 3                                              |                                                   |                     |               | 50                  | mV                |

| V <sub>OS</sub>  | Offset Voltage                                                | $R_L = 100Ω$<br>See 🛭 3                                                   |                                                   | 1.09                | 1.22          | 1.36                | V                 |

| ΔV <sub>OS</sub> | Change in V <sub>OS</sub> between Complimentary Output States | $R_L = 100\Omega$<br>See 图 3                                              |                                                   |                     |               | 50                  | mV                |

| Ios              | Output Short-Circuit Current                                  | V <sub>OUT</sub> = GND, VOD                                               | SEL = V <sub>DD</sub>                             |                     | <b>-</b> 15.5 |                     | mA                |

| SUPPLY           | CURRENT                                                       |                                                                           |                                                   |                     |               |                     |                   |

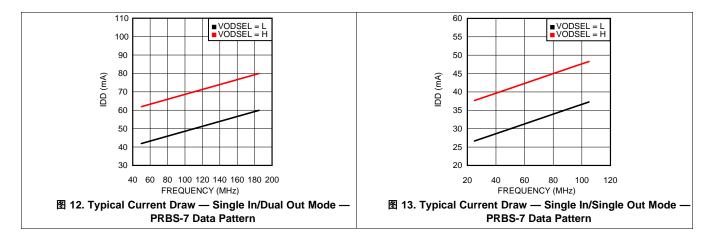

| IDDT1            | Worst Case Supply Current                                     | Checkerboard pattern,                                                     | f = 105 MHz,<br>MODE0 = GND<br>(SISO)             |                     | 50            | 85                  | mA                |

| IDDT2            | (includes load current)                                       | $R_{L} = 100 \Omega,$ $VODSEL = V_{DD},$ $V_{DD} = 1.89 V,$               | f = 185 MHz,<br>MODE0 = V <sub>DD</sub><br>(SIDO) |                     | 80            | 140                 | mA                |

|                  | ,                                                             | MODE0 = V <sub>DD</sub> (SIDO),                                           | VODSEL = GND,<br>VDD = 1.8                        |                     | 50            |                     | mA                |

| IDDTP            | Supply Current PRBS-7                                         | $f = 150 \text{ MHz},$ $R_L = 100 \Omega,$ PRBS-7 Pattern                 | VODSEL = V <sub>DD</sub> ,<br>VDD = 1.8           |                     | 70            |                     | mA                |

|                  |                                                               | MODE0 = V <sub>DD</sub> (SIDO),                                           | VODSEL = GND,<br>VDD = 1.8                        |                     | 53            |                     | mA                |

| IDDTG            | Supply Current 16 Grayscale                                   | $f = 150 \text{ MHz},$ $R_L = 100 \Omega,$ $16 \text{ Grayscale}$ Pattern | VODSEL = V <sub>DD</sub> ,<br>VDD = 1.8           |                     | 71            |                     | mA                |

| IDDZ             | Power Down Supply Current                                     | PDB = GND                                                                 |                                                   |                     | 6             | 800                 | μA                |

## 7.6 Recommended Input Characteristics

Over recommended operating supply and temperature ranges unless otherwise specified.

|      | PARAMETER              |                  |       | TYP              | MAX   | UNIT |

|------|------------------------|------------------|-------|------------------|-------|------|

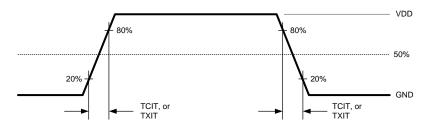

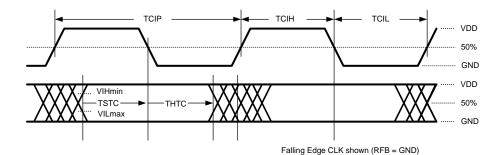

| TCIT | IN_CLK Transition Time | MODE0 = GND      | 1     |                  | 4     | ns   |

|      | 图 5                    | $MODE0 = V_{DD}$ | 1     |                  | 2     | ns   |

| TOID | IN_CLK Period<br>图 6   | MODE0 = GND      | 9.53  | T <sup>(1)</sup> | 40    | ns   |

| TCIP |                        | $MODE0 = V_{DD}$ | 5.40  | Т                | 20    | ns   |

| TCIH | IN_CLK High Time       | Can El C         | 0.35T | 0.5T             | 0.65T | ns   |

| TCIL | IN_CLK Low Time        | See 图 6          | 0.35T | 0.5T             | 0.65T | ns   |

| TXIT | IN_n Transition Time   | See ₹ 5          | 1.5   |                  | 0.3T  | ns   |

<sup>(1)</sup> T = Typical Period of the input Clock.

## 7.7 Switching Characteristics

Over recommended operating supply and temperature ranges unlessotherwise specified.

|         | PARAMETER                                               |                                     | MIN TYP           | MAX               | UNIT |

|---------|---------------------------------------------------------|-------------------------------------|-------------------|-------------------|------|

| TSTC    | IN_n Setup to IN_CLK                                    | See 图 6                             | 0                 |                   | ns   |

| THTC    | IN_n Hold from IN_CLK                                   | See 图 6                             | 2.5               |                   | ns   |

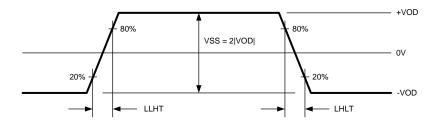

| LLHT    | LVDS Low-to-High Transition Time<br>See 图 4             |                                     | 0.33              |                   | ns   |

| LHLT    | LVDS High-to-Low Transition Time<br>See 图 4             |                                     | 0.33              |                   | ns   |

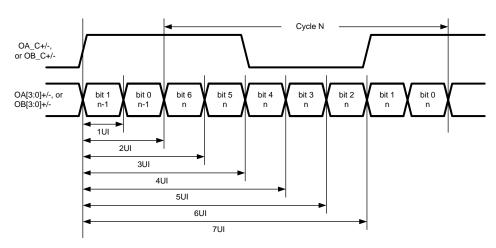

| ТВІТ    | LVDC Output Dit Width                                   | MODE0 = GND                         | 1/7 TCIP          |                   | ns   |

| IDII    | LVDS Output Bit Width                                   | $MODE0 = V_{DD}$                    | 2/7 TCIP          |                   | ns   |

| TPPOS0  | Transmitter Output Pulse Positions Normalized for Bit 0 | See 图 9                             | 1                 |                   | UI   |

| TPPOS1  | Transmitter Output Pulse Positions Normalized for Bit 1 | See 图 9                             | 2                 |                   | UI   |

| TPPOS2  | Transmitter Output Pulse Positions Normalized for Bit 2 | See 图 9                             | 3                 |                   | UI   |

| TPPOS3  | Transmitter Output Pulse Positions Normalized for Bit 3 | See 图 9                             | 4                 |                   | UI   |

| TPPOS4  | Transmitter Output Pulse Positions Normalized for Bit 4 | See 图 9                             | 5                 |                   | UI   |

| TPPOS5  | Transmitter Output Pulse Positions Normalized for Bit 5 | See 图 9                             | 6                 |                   | UI   |

| TPPOS6  | Transmitter Output Pulse Positions Normalized for Bit 6 | See 图 9                             | 7                 |                   | UI   |

| Δ_TPPOS | Variation in Transmitter Pulse Position (Bit 6 — Bit 0) | See 图 9                             | ±0.06             |                   | UI   |

| TCCS    | LVDS Channel to Channel Skew                            |                                     | 110               |                   | ps   |

| TJCC    | Jitter Cycle-to-Cycle                                   | MODE0 = GND,<br>f = 105 MHz         | 0.176             |                   | UI   |

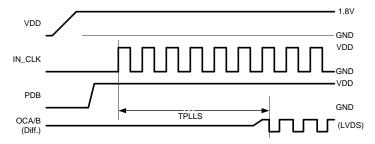

| TPLLS   | Phase Lock Loop Set (Enable Time)                       | See 图 7                             | 1                 |                   | ms   |

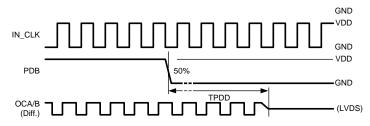

| TPDD    | Powerdown Delay                                         | See 图 8                             |                   | 100               | ns   |

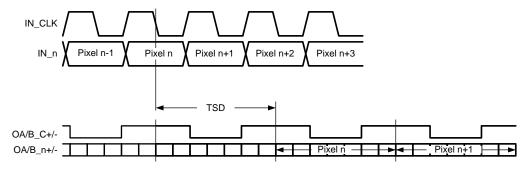

| TSD     | Latency Delay                                           | MODE0 = GND<br>See 图 11             | 2*TCIP +<br>10.54 | 2*TCIP +<br>19.38 | ns   |

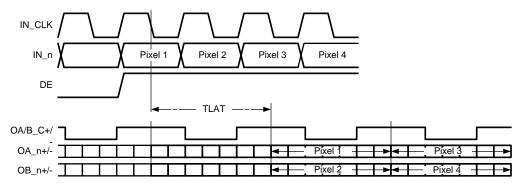

| ΓLAT    | Latency Delay for Single Pixel In / Dual Pixel Out Mode | MODE0 = V <sub>DD</sub><br>See 图 10 | 9*TCIP +<br>4.19  |                   | ns   |

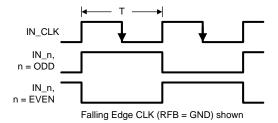

## 7.8 AC Timing Diagrams

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

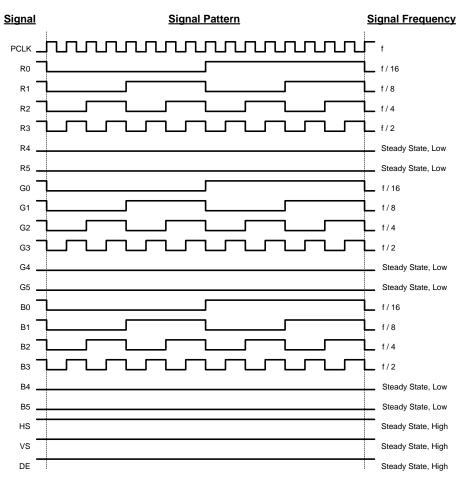

- B. 8 2 shows a falling edge data strobe (IN\_CLK).

图 1. Checker Board Test Pattern

## AC Timing Diagrams (接下页)

- A. The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and LVCMOS/ I/O.

- B. Recommended pin to signal mapping for 18 bits per pixel, customer may choose to define differently. The 16 grayscale test pattern tests device power consumption for a "typical" LCD display pattern. The test pattern approximates signal switching needed to produce groups of 16 vertical stripes across the display.

- C. 8 2 shows a falling edge data strobe (IN\_CLK).

## 图 2. "16 Gray Scale" Test Pattern (Falling Edge Clock shown)

图 3. DS90C189-Q1 (Transmitter) LVDS Output Load

## AC Timing Diagrams (接下页)

图 4. LVDS Output Transition Times

图 5. LVCMOS Input Transition Times

## 图 6. LVCMOS Input Setup/Hold and Clock High/Low Times (Falling Edge Strobe)

图 7. Start Up / Phase Lock Loop Set Time

## AC Timing Diagrams (接下页)

图 8. Sleep Mode / Power Down Delay

图 9. LVDS Serial Bit Positions

图 10. Single In, Dual Out Mode Timing and Latency

图 11. Single In, Single Out Mode Timing and Latency

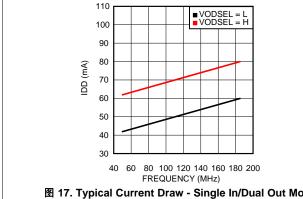

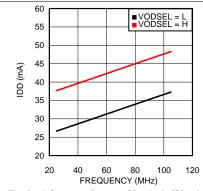

## 7.9 Typical Characteristics

#### 8 Detailed Description

#### 8.1 Overview

DS90C189-Q1 converts a wide parallel LVCMOS input bus into banks of OLDI (LVDS) data. The device can be configured to support RGB-888 (24-bit color) in two main configurations: single pixel in / single pixel out; single pixel in / dual pixel out. The DS90C189-Q1 has power saving features including: selectable VOD and a power down pin control.

#### 8.2 Functional Block Diagrams

## Functional Block Diagrams (接下页)

#### 8.3 Feature Description

#### 8.3.1 AEC-Q100 Qualified

The DS90C189-Q1 is qualified to AEC-Q100 Grade 2 standards and operates from -40°C to +105°C.

#### 8.3.2 ESD Protection

The DS90C189-Q1 has a HBM ESD Classification Level of ±8 kV and CDM ESD Classification Level of ±750 V.

#### 8.3.3 Operating Modes

The DS90C189-Q1 has two operating modes: Single Pixel In, Single Pixel Out (SISO), 25 MHz – 105 MHz and Single Pixel In, Dual Pixel Out (SIDO), 50 MHz – 185 MHz.

#### 8.3.4 LVDS Configurations

The DS90C189-Q1 supports 3D+C, 4D+C, 6D+C, 6D+2C, 8D+C, and 8D+2C LVDS configurations.

#### 8.4 Device Functional Modes

#### 8.4.1 Device Configuration

The MODE0 pin is used to configure the DS90C189-Q1 into the two main operation modes as shown in the table below.

表 1. Mode Configurations

| MODE0 | CONFIGURATION                                  |  |

|-------|------------------------------------------------|--|

| 0     | Single Pixel Input, Single Pixel Output (SISO) |  |

| 1     | Single Pixel Input, Dual Pixel Output (SIDO)   |  |

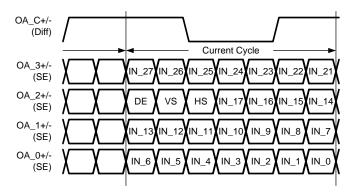

#### 8.4.2 Single Pixel Input / Single Pixel Output

When MODE0 is set to low, data from IN\_[27:21], IN\_[17:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- with OA\_C+/-.

In this configuration IN\_CLK can range from 25 MHz to 105 MHz, resulting in a total maximum payload of 700 Mbps (28 bits \* 25MHz) to 2.94 Gbps (28 bits \* 105 MHz). Each LVDS driver will operate at a speed of 7 bits per input clock cycle, resulting in a serial line rate of 175 Mbps to 735 Mbps. OA\_C+/- will operate at the same rate as IN\_CLK with a duty cycle ratio of 57:43.

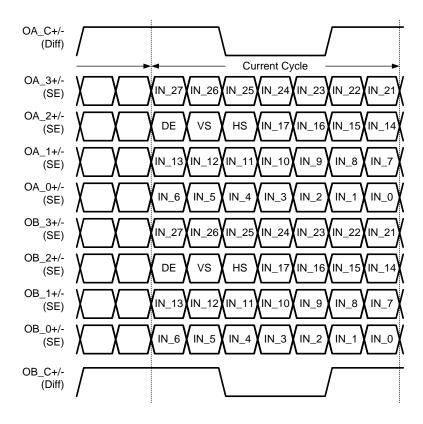

#### 8.4.3 Single Pixel Input / Dual Pixel Output

When MODE0 is HIGH, data from IN\_[27:21], IN\_[17:0], HS, VS and DE is serialized and driven out on OA\_[3:0]+/- and OB\_[3:0]+/- with OA\_C+/- and OB\_C+/-. The input LVCMOS data is split into odd and even pixels starting with the odd (first) pixel outputs OA\_[3:0]+/- and then the even (second) pixel outputs OB\_[3:0]+/-. The splitting of the data signals starts with DE (data enable) transitioning from logic LOW to HIGH indicating active data (see 10). **The number of clock cycles during blanking must be an EVEN number.** This configuration will allow the user to interface with two FPD-Link receivers or other dual pixel inputs.

In this configuration IN\_CLK can range from 50 MHz to 185 MHz, resulting in a total maximum payload of 1.4 Gbps (28 bits \* 50 MHz) to 5.18 Gbps (28 bits \* 185 MHz). Each LVDS driver will operate at a speed of 7 bits per 2 input clock cycles, resulting in a serial line rate of 175 Mbps to 647.5 Mbps. OA\_C+/- and OA\_B+/- will operate at ½ the rate as IN\_CLK with a duty cycle ratio of 57:43.

In the Single Pixel Input / Dual Pixel Output mode OA\_x and OB\_x can become misaligned if the clock or data is interrupted or PDB is toggled. If the clock or data is interrupted or PDB is toggled to prevent misalignment the following should be done:

- 1. Disable the clock and data.

- 2. Toggle PDB to Low and then High.

- 3. After PDB settles reset the data pattern and enable the clock and data.

#### 8.4.4 Pixel Clock Edge Select (RFB)

The RFB pin determines the edge that the input LVCMOS data is latched on. If RFB is HIGH, input data is latched on the RISING EDGE of the pixel clock (IN\_CLK). If RFB is LOW, the input data is latched on the FALLING EDGE of the pixel clock. Note: This can be set independently of receiver's output clock strobe.

表 2. Pixel Clock Edge

| RFB | Result       |

|-----|--------------|

| 0   | FALLING edge |

| 1   | RISING edge  |

#### 8.4.5 Power Management

The DS90C189-Q1 has several features to assist with managing power consumption. The device can be configured through the MODE0 control pin to enable only the required number of LVDS drivers for each application. If no clock is applied to the IN\_CLK pin, the DS90C189-Q1 will enter a low power state. To place the DS90C189-Q1 in its lowest power state, the device can be powered down by driving the PDB pin to LOW.

#### 8.4.6 Sleep Mode (PDB)

The DS90C189-Q1 provides a power down feature. When the device has been powered down, current draw through the supply pins is minimized and the PLL is shut down. The LVDS drivers are also powered down with their outputs pulled to GND through  $100-\Omega$  resistors (not tri-stated).

表 3. Power Down Select

| PDB | Result               |

|-----|----------------------|

| 0   | SLEEP Mode (default) |

| 1   | ACTIVE (enabled)     |

#### 8.4.7 LVDS Outputs

The DS90C189-Q1's LVDS drivers are compatible with ANSI/TIA/EIA-644-A LVDS receivers. The LVDS drivers can output a power saving low  $V_{OD}$ , or a high  $V_{OD}$  to enable longer trace and cable lengths by configuring the VODSEL pin.

表 4. VOD Select

| VODSEL | Result             |

|--------|--------------------|

| 0      | ±220 mV (440 mVpp) |

| 1      | ±340 mV (680 mVpp) |

Any unused LVDS outputs that are not powered down due to the MODE0 pin should be externally terminated differentially with a 100 ohm resistor. For example, when driving a timing controller (TCON) that only requires an 8D + C LVDS interface, rather than 8D + 2C, the unused clock line should be terminated near the package of the DS90C189-Q1. For more information regarding the electrical characteristics of the LVDS outputs, refer to the LVDS DC Characteristics and LVDS Switching Specifications.

#### 8.4.8 LVCMOS Inputs

The DS90C189-Q1 has one bank of 24 data inputs, one set of video control signal (HS, VS and DE) inputs and several device configuration LVCMOS pins. All LVCMOS input pins are designed for 1.8 V LVCMOS logic. All LVCMOS inputs, including clock, data and configuration pins, have an internal pull down resistor to set a default state. If any inputs are unused, they can be left as no connect (NC) or connected to ground.

#### 8.5 Programming

#### 8.5.1 LVDS Interface / TFT Color Data Recommended Mapping

Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application. The DS90C189-Q1 supports two modes of operation for single and dual pixel applications supporting 24bpp color depths.

In the Dual Pixel / 24bpp mode, eight LVDS data lines are provided along with two LVDS clock lines (8D+2C). The Deserializer may utilize one or two clock lines. The 53 bit interface typically assigns 24 bits to RGB for the odd pixel, 24 bits to RGB for the even pixel, 3 bits for the video control signals (HS, VS and DE), 1 bit for odd pixel and 1 bit for even pixel which can be ignored or used for general purpose data, control or L/R signaling.

A reduced width input interface is also supported with a Single-to-Dual Pixel conversion where the data is presented at double rate (same clock edge, 2X speed, see \$\begin{align\*} 10 \) and the DE transition is used to flag the first pixel. Also note in the 8D+2C configuration, the three video control signals are sent over **both** the A and B outputs. The DES / TCON may recover one set, or both depending upon its implementation. The Dual Pixel / 24bpp 8D+2C LVDS Interface Mapping is shown in \$\begin{align\*} 14.

In the Single Pixel / 24bpp mode, four LVDS data lines are provided along with a LVDS clock line (4D+C). The 28 bit interface typically assigns 24 bits to RGB color data, 3 bits to video control (HS, VS and DE) and one spare bit can be ignored, used for L/R signaling or function as a general purpose bit. The Single Pixel / 24bpp 4D+C LVDS Interface Mapping is shown in  $\boxtimes$  15.

## Programming (接下页)

图 14. Dual Pixel / 24bpp LVDS Mapping

图 15. Single Pixel / 24bpp LVDS Mapping

## 8.5.1.1 Color Mapping Information

A defacto color mapping is shown next. Different color mapping options exist. Check with the color mapping of the Deserializer / TCON device that is used to ensure compatible mapping for the application.

表 5. Single Pixel Input / 24bpp / MSB on CH3

| DS90C189-Q1 Input | Color Mapping | Note                       |

|-------------------|---------------|----------------------------|

| IN_22             | R7            | MSB                        |

| IN_21             | R6            |                            |

| IN_5              | R5            |                            |

| IN_4              | R4            |                            |

| IN_3              | R3            |                            |

| IN_2              | R2            |                            |

| IN_1              | R1            |                            |

| IN_0              | R0            | LSB                        |

| IN_24             | G7            | MSB                        |

| IN_23             | G6            |                            |

| IN_11             | G5            |                            |

| IN_10             | G4            |                            |

| IN_9              | G3            |                            |

| IN_8              | G2            |                            |

| IN_7              | G1            |                            |

| IN_6              | G0            | LSB                        |

| IN_26             | B7            | MSB                        |

| IN_25             | B6            |                            |

| IN_17             | B5            |                            |

| IN_16             | B4            |                            |

| IN_15             | B3            |                            |

| IN_14             | B2            |                            |

| IN_13             | B1            |                            |

| IN_12             | B0            |                            |

| DE                | DE            | Data Enable <sup>(1)</sup> |

| VS                | VS            | Vertical Sync              |

| HS                | HS            | Horizontal Sync            |

| IN_27             | GP            | General Purpose            |

<sup>(1)</sup> See section Single Pixel Input / Dual Pixel Output.

表 6. Single Pixel Input / 24bpp / LSB on CH3

| DS90C189-Q1 Input | Color Mapping | Note                       |

|-------------------|---------------|----------------------------|

| IN_5              | R7            | MSB                        |

| IN_4              | R6            |                            |

| IN_3              | R5            |                            |

| IN_2              | R4            |                            |

| IN_1              | R3            |                            |

| IN_0              | R2            |                            |

| IN_22             | R1            |                            |

| IN_21             | R0            | LSB                        |

| IN_11             | G7            | MSB                        |

| IN_10             | G6            |                            |

| IN_9              | G5            |                            |

| IN_8              | G4            |                            |

| IN_7              | G3            |                            |

| IN_6              | G2            |                            |

| IN_24             | G1            |                            |

| IN_23             | G0            | LSB                        |

| IN_17             | B7            | MSB                        |

| IN_16             | B6            |                            |

| IN_15             | B5            |                            |

| IN_14             | B4            |                            |

| IN_13             | B3            |                            |

| IN_12             | B2            |                            |

| IN_26             | B1            |                            |

| IN_25             | B0            |                            |

| DE                | DE            | Data Enable <sup>(1)</sup> |

| VS                | VS            | Vertical Sync              |

| HS                | HS            | Horizontal Sync            |

| IN_27             | GP            | General Purpose            |

(1) See section Single Pixel Input / Dual Pixel Output.

## 9 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 9.1 Application Information

The DS90C189-Q1 is a Low Power Bridge for automotive application that reduces the size of the RGB interface between the host GPU and the Display. It is designed to support single pixel data transmission between Host and Flat Panel Display up to QXGA (2048x1536) at 60 Hz resolutions. The transmitter converts up to 24 bits (Single Pixel 24 bit color) of 1.8V LVCMOS data into two channels of 4 data + clock (4D+C) reduced width interface LVDS compatible data streams.

## 9.2 Typical Application

Copyright © 2017, Texas Instruments Incorporated

图 16. Single Pixel In Dual Pixel Out (SIDO) Mode

#### 9.2.1 Design Requirements

The DS90C189 is used to convert 24-bit color to two channels of LVDS datastreams.

表 7. Design Parameters

| DESIGN PARAMETER | VALUE         |

|------------------|---------------|

| Supply           | 1.8V          |

| Display Driven   | SXGA+, WUXGA+ |

| Pixel Depth      | 24 bits       |

#### 9.2.2 Detailed Design Procedure

#### 9.2.2.1 LVDS Interconnect Guidelines

Refer to the AN-1108 Channel-Link PCB and Interconnect Design-In Guidelines (SNLA008) and Transmission Line RAPIDESIGNER Operation and Applications Guide (SNLA035) for full details.

- Use 100  $\Omega$  coupled differential pairs

- Use differential connectors when above 500 Mbps

- Minimize skew within the pair

- Use the S/2S/3S rule in spacings

- S = space between the pairs

- 2S = space between pairs

- 3S = space to LVCMOS signals

- Place ground vias next to signal vias when changing between layers

- When a signal changes reference planes, place a bypass cap and vias between the new and old reference plane

For more tips and detailed suggestions regarding high speed board layout principles, see the LVDS Owner's Manual at http://www.ti.com/lvds

#### 9.2.3 Application Curves

图 17. Typical Current Draw - Single In/Dual Out Mode -PRBS-7 Data Pattern

图 18. Typical Current Draw - Single In/Single Out Mode -PRBS-7 Data Pattern

## 10 Power Supply Recommendations

#### 10.1 Power Up Sequence

The  $V_{DD}$  power supply pins do not require a specific power on sequence and can be powered on in any order. However, the PDB pin should only be set to logic HIGH once the power sent to all supply pins is stable. Active data inputs should not be applied to the DS90C189-Q1 until all of the input power pins have been powered on, settled to the recommended operating voltage and the PDB pin has be set to logic HIGH.

The user experience can be impacted by the way a system powers up and powers down an LCD screen. The following sequence is recommended:

Power up sequence (DS90C189-Q1 PDB input initially LOW):

- 1. Ramp up LCD power (maybe 0.5ms to 10ms) but keep backlight turned off.

- 2. Toggle DS90C189-Q1 power down pin to PDB =  $V_{DD}$ .

- 3. Enable clock and wait for additional 0-200ms to ensure display noise won't occur.

- 4. Enable video source output; start sending black video data.

- Send >1ms of black video data; this allows the DS90C189-Q1 to be phase locked, and the display to show black data first.

- 6. Start sending true image data.

- 7. Enable backlight.

Power Down sequence (DS90C189-Q1 PDB input initially HIGH):

- 1. Disable LCD backlight; wait for the minimum time specified in the LCD data sheet for the backlight to go low.

- 2. Video source output data switch from active video data to black image data (all visible pixel turn black); drive this for >2 frame times.

- 3. Set DS90C189-Q1 power down pin to PDB = GND.

- 4. Disable the video output of the video source.

- 5. Remove power from the LCD panel for lowest system power.

#### 10.2 Power Supply Filtering

The DS90C189-Q1 has several power supply pins at 1.8 V. It is important that these pins all be connected and properly bypassed. Bypassing should consist of at least one  $0.1\mu F$  capacitor placed on each pin, with an additional 4.7  $\mu F$  - 22  $\mu F$  capacitor placed on the PLL supply pin (VDDP).  $0.01~\mu F$  capacitors are typically recommended for each pin. Additional filtering including ferrite beads may be necessary for noisy systems. It is recommended to place a 0 ohm resistor at the bypass capacitors that connect to each power pin to allow for additional filtering if needed. A large bulk capacitor is recommended at the point of power entry. This is typically in the 50  $\mu F$  — 100  $\mu F$  range.

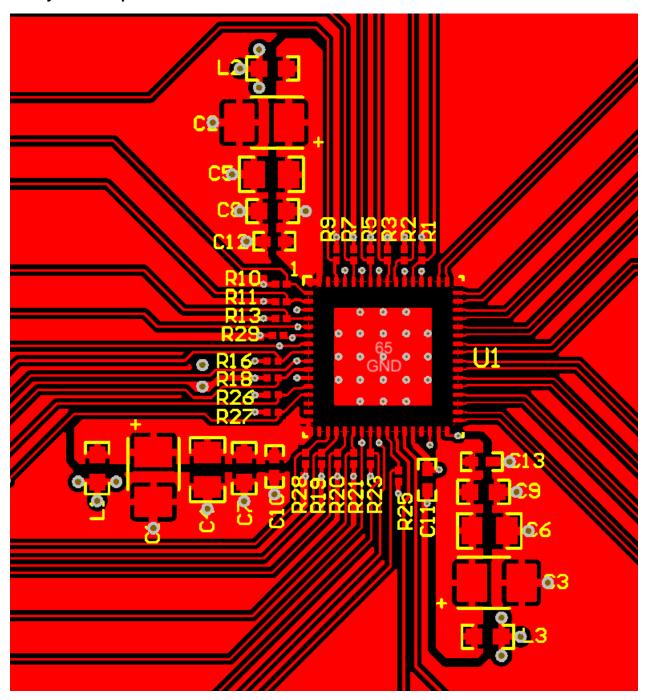

## 11 Layout

#### 11.1 Layout Guidelines

Circuit board layout and stack-up for the LVDS devices should be designed to provide low-noise power feed to the device. Good layout practice will also separate high frequency or high-level inputs and outputs to minimize unwanted stray noise pickup, feedback and interference. Power system performance may be greatly improved by using thin dielectrics (2 to 4 mils) for power / ground sandwiches. This arrangement provides plane capacitance for the PCB power system with low-inductance parasitics, which has proven especially effective at high frequencies, and makes the value and placement of external bypass capacitors less critical. This practice is easier to implement in dense pcbs with many layers and may not be practical in simpler boards. External bypass capacitors should include both RF ceramic and tantalum electrolytic types. RF capacitors may use values in the range of 0.01 uF to 0.1 uF. Tantalum capacitors may be in the 2.2 uF to 10 uF range. Voltage rating of the tantalum capacitors should be at least 5X the power supply voltage being used.

Surface mount capacitors are recommended due to their smaller parasitics. When using multiple capacitors per supply pin, locate the smaller value closer to the pin. It is recommended to connect power and ground pins directly to the power and ground planes with bypass capacitors connected to the plane with vias on both ends of the capacitor.

A small body size X7R chip capacitor, such as 0603, is recommended for external bypass. Its small body size reduces the parasitic inductance of the capacitor. The user must pay attention to the resonance frequency of these external bypass capacitors, usually in the range of 20-30 MHz. To provide effective bypassing, multiple capacitors are often used to achieve low impedance between the supply rails over the frequency of interest. At high frequency, it is also a common practice to use two vias from power and ground pins to the planes, reducing the impedance at high frequency. Some devices provide separate power and ground pins for different portions of the circuit. This is done to isolate switching noise effects between different sections of the circuit. Separate planes on the PCB are typically not required. Pin Description tables typically provide guidance on which circuit blocks are connected to which power pin pairs. In some cases, an external filter many be used to provide clean power to sensitive circuits such as PLLs.

Use at least a four layer board with a power and ground plane. Locate LVCMOS signals away from the LVDS lines to prevent coupling from the LVCMOS lines to the LVDS lines. Closely coupled differential lines of 100 Ohms are typically recommended for LVDS interconnect. The closely coupled lines help to ensure that coupled noise will appear as common mode and thus is rejected by the receivers. The tightly coupled lines will also radiate less.

For more information on the VQFN package, refer to the *AN-1187 Leadless Leadframe Package (LLP)* application note (SNOA401).

## 11.2 Layout Example

图 19. Layout Example

#### 12 器件和文档支持

#### 12.1 文档支持

#### 12.1.1 相关文档

请参阅如下相关文档:

- 《LVDS 用户手册》(SNLA187)

- 《AN-1108 通道链路 PCB 和互连设计指南》(SNLA008)

- 《传输线路 RAPIDESIGNER 操作和 应用 指南》(SNLA035)

- 《AN-1187 无引线框架封装 (LLP)》(SNOA401)

#### 12.2 接收文档更新通知

要接收文档更新通知,请导航至 Tl.com.cn 上的器件产品文件夹。单击右上角的通知我 进行注册,即可每周接收产 品信息更改摘要。有关更改的详细信息,请查看任何已修订文档中包含的修订历史记录。

#### 12.3 社区资源

下列链接提供到 TI 社区资源的连接。链接的内容由各个分销商"按照原样"提供。这些内容并不构成 TI 技术规范, 并且不一定反映 TI 的观点:请参阅 TI 的 《使用条款》。

TI E2E™ 在线社区 TI 的工程师对工程师 (E2E) 社区。此社区的创建目的在于促进工程师之间的协作。在 e2e.ti.com 中,您可以咨询问题、分享知识、拓展思路并与同行工程师一道帮助解决问题。

设计支持 TI 参考设计支持 可帮助您快速查找有帮助的 E2E 论坛、设计支持工具以及技术支持的联系信息。

#### 12.4 商标

E2E is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

#### 12.5 静电放电警告

ESD 可能会损坏该集成电路。德州仪器 (TI) 建议通过适当的预防措施处理所有集成电路。如果不遵守正确的处理措施和安装程序,可 能会损坏集成电路。

🗱 ESD 的损坏小至导致微小的性能降级,大至整个器件故障。 精密的集成电路可能更容易受到损坏,这是因为非常细微的参数更改都可 能会导致器件与其发布的规格不相符。

#### 12.6 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、缩写和定义。

#### 13 机械、封装和可订购信息

以下页面包含机械、封装和可订购信息。这些信息是指定器件的最新可用数据。数据如有变更,恕不另行通知,且 不会对此文档进行修订。如需获取此数据表的浏览器版本,请查阅左侧的导航栏。

## PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| DS90C189TWRTDRQ1 | ACTIVE     | VQFN         | RTD                | 64   | 2500           | RoHS & Green | NIPDAUAG                      | Level-3-260C-168 HR | -40 to 115   | DS90C189Q               | Samples |

| DS90C189TWRTDTQ1 | ACTIVE     | VQFN         | RTD                | 64   | 250            | RoHS & Green | NIPDAUAG                      | Level-3-260C-168 HR | -40 to 115   | DS90C189Q               | Samples |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

## PACKAGE MATERIALS INFORMATION

www.ti.com 2-Aug-2018

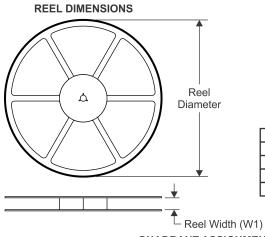

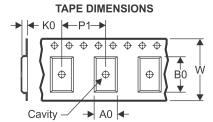

## TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

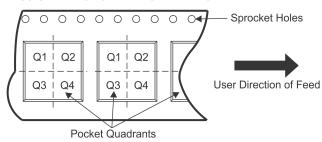

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device           | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| DS90C189TWRTDRQ1 | VQFN            | RTD                | 64 | 2500 | 330.0                    | 16.4                     | 9.3        | 9.3        | 1.1        | 12.0       | 16.0      | Q2               |

| DS90C189TWRTDTQ1 | VQFN            | RTD                | 64 | 250  | 180.0                    | 16.4                     | 9.3        | 9.3        | 1.1        | 12.0       | 16.0      | Q2               |

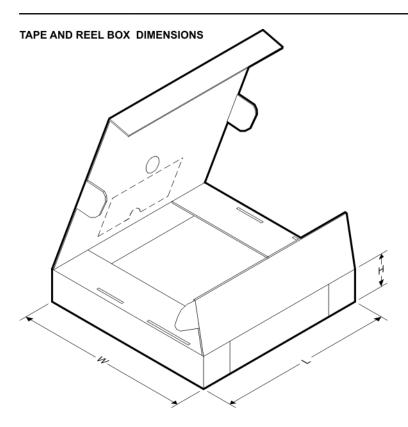

www.ti.com 2-Aug-2018

#### \*All dimensions are nominal

| Device           | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DS90C189TWRTDRQ1 | VQFN         | RTD             | 64   | 2500 | 367.0       | 367.0      | 38.0        |

| DS90C189TWRTDTQ1 | VQFN         | RTD             | 64   | 250  | 210.0       | 185.0      | 35.0        |

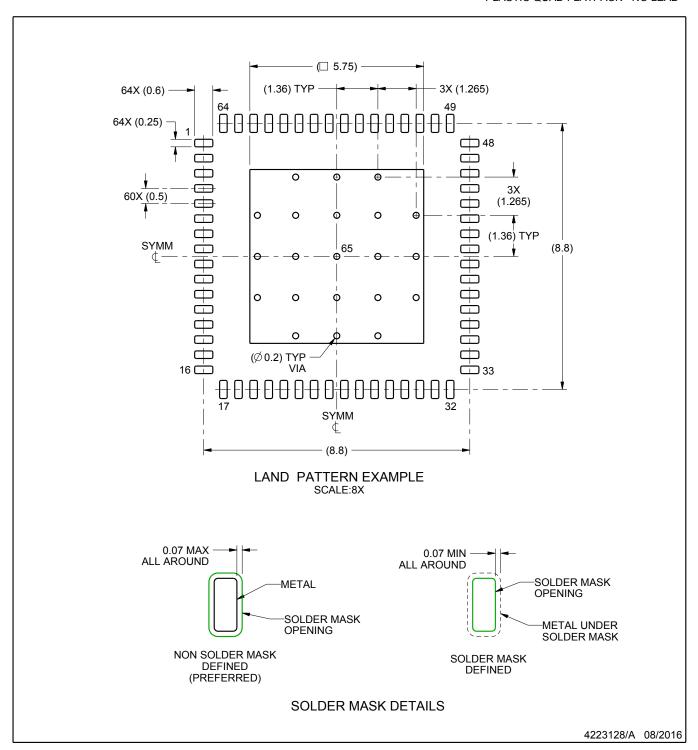

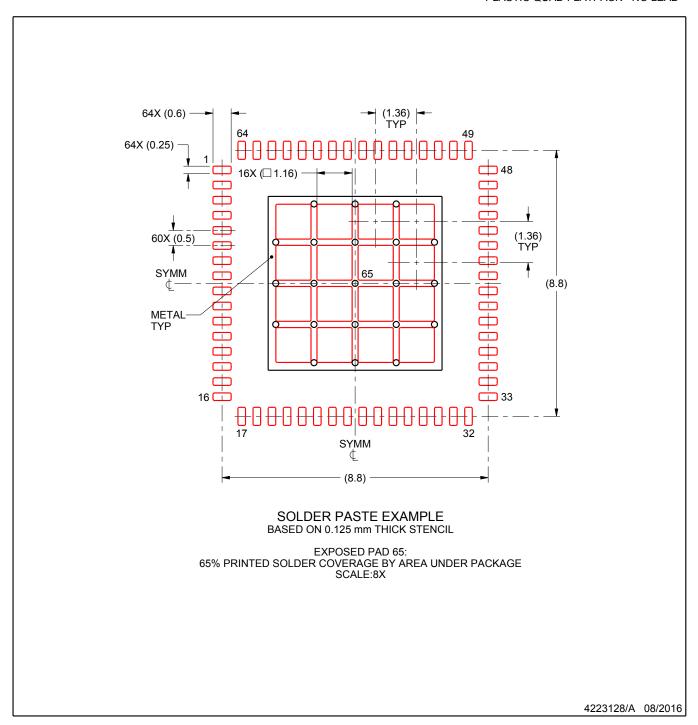

# VQFNP - 0.9 mm max height PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4205146/D

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

#### 重要声明和免责声明

TI 均以"原样"提供技术性及可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证其中不含任何瑕疵,且不做任何明示或暗示的担保,包括但不限于对适销性、适合某特定用途或不侵犯任何第三方知识产权的暗示担保。

所述资源可供专业开发人员应用TI产品进行设计使用。您将对以下行为独自承担全部责任: (1)针对您的应用选择合适的TI产品; (2)设计、验证并测试您的应用; (3)确保您的应用满足相应标准以及任何其他安全、安保或其他要求。所述资源如有变更,恕不另行通知。TI对您使用所述资源的授权仅限于开发资源所涉及TI产品的相关应用。除此之外不得复制或展示所述资源,也不提供其它TI或任何第三方的知识产权授权许可。如因使用所述资源而产生任何索赔、赔偿、成本、损失及债务等,TI对此概不负责,并且您须赔偿由此对TI及其代表造成的损害。

TI 所提供产品均受TI 的销售条款 (http://www.ti.com.cn/zh-cn/legal/termsofsale.html) 以及ti.com.cn上或随附TI产品提供的其他可适用条款的约束。TI提供所述资源并不扩展或以其他方式更改TI 针对TI 产品所发布的可适用的担保范围或担保免责声明。

邮寄地址: 上海市浦东新区世纪大道 1568 号中建大厦 32 楼,邮政编码: 200122 Copyright © 2020 德州仪器半导体技术(上海)有限公司