# TAS2563 具有集成式 DSP 和 IV 检测功能的 6.1W 升压 D 类音频放大器

## 1 特性

- 主要特性

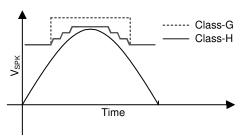

- 11.5V、12 级超前 H 类升压

- 集成型 DSP

- 高达 40kHz 的满量程超声波输出

- 2个 PDM 麦克风输入

- 强大的 D 类音频放大器:

- 6.1W 1% THD+N (  $4\Omega$  , 3.6V )

- 5W 1% THD+N (8Ω, 3.6V)

- 10W 1% THD+N (4Ω, 12V)

- 保护特性:

- 实时 I/V 检测扬声器保护

- 扬声器热保护和过冲保护

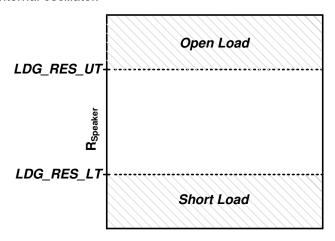

- 短路和开路负载保护

- 热保护和过流保护

- 高级音频处理

- 专用实时 DSP, 具有:

- 10 频带均衡器

- 3 频带动态均衡器

- 动态范围压缩

- 心理声学低音

- 灵活的接口和控制:

- I<sup>2</sup>S/TDM:8个通道(32位),运行速率达 96KSPS

- I2C:可选择地址,快速模式+

- 芯片间通信总线 (DSBGA)

- 8kHz 至 96kHz 采样速率

- 电源效率和灵活性:

- 1W 下效率达 83.5%

- 硬件关断 VBAT 电流低于 1uA

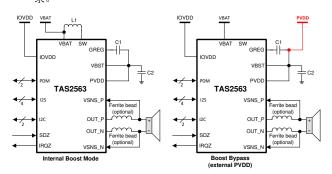

- 升压旁路模式

- 电源和管理

- VBAT: 2.5V 至 5.5V

- VDD: 1.62V 至 1.95V

- PVDD: VBAT 至 13V (QFN)

- PVDD: VBAT 至 16V (DSBGA)

- IOVDD: 1.65V 至 3.6V

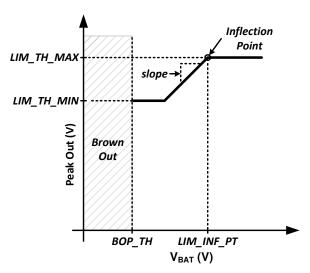

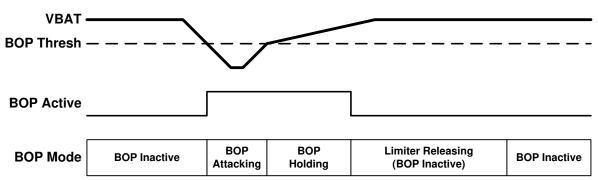

- VBAT 跟踪峰值电压限制器

- 高级欠压保护功能

### 2 应用

- 智能手机、平板电脑和笔记本电脑

- 智能音箱(带语音助理)

- 蓝牙和无线音箱

- 智能家居

- IP 摄像机

## 3 说明

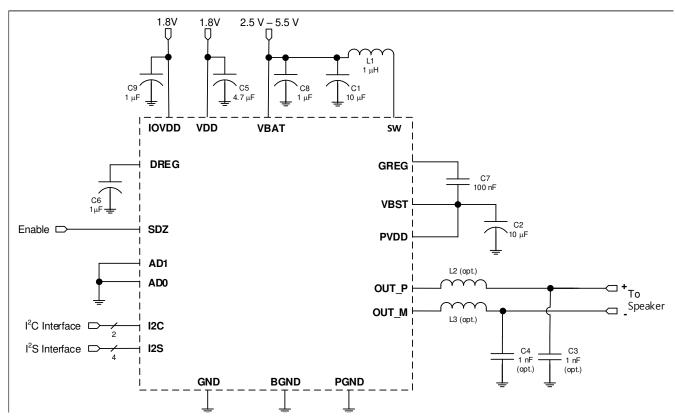

TAS2563 是一款经过优化、可将高峰值功率高效地驱 动到小型扬声器的数字输入 D 类音频放大器。该 D 类 放大器能够在 3.6V 的电池电压下使用集成式 11.5V H 类升压功能将 6.1W 峰值功率提供给  $4\Omega$  负载,或在升 压旁路模式下使用外部 12V 电源将 10W 峰值功率提供 给 $4\Omega$ 负载。

片上低延迟 DSP 支持德州仪器 (TI) 的 SmartAmp 扬声 器保护算法。集成的电流和电压检测功能可对扬声器进 行实时监测,从而在改变峰值声压级 (SPL) 的同时保 持扬声器不受损坏。

集成的超前 H 类升压功能可在播放期间动态调整升压 电压,从而提高电池供电型系统的效率并延长电池寿 命。对于稳压壁式供电型系统,TAS2563 还具有升压 旁路模式,支持高达 16V 的电源电压以实现更高的输 出功率。

两个 PDM 麦克风输入简化了双向音频系统的音频信号 链,能够将数字麦克风与主机处理器连接起来。电池跟 踪峰值电压限制器具有欠压保护功能,可以优化放大器 在整个充电周期中的余量,从而防止系统关断。

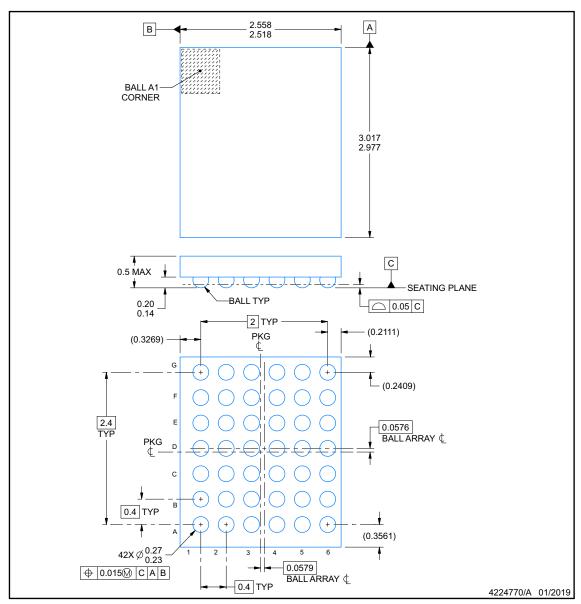

#### **哭**件信息(1)

| 器件型号    | 封装    | 封装尺寸(标称值)   |

|---------|-------|-------------|

| TAS2563 | DSBGA | 2.5mm × 3mm |

| TAS2563 | QFN   | 4.5mm x 4mm |

如需了解所有可用封装,请参阅数据表末尾的可订购产品附 录。

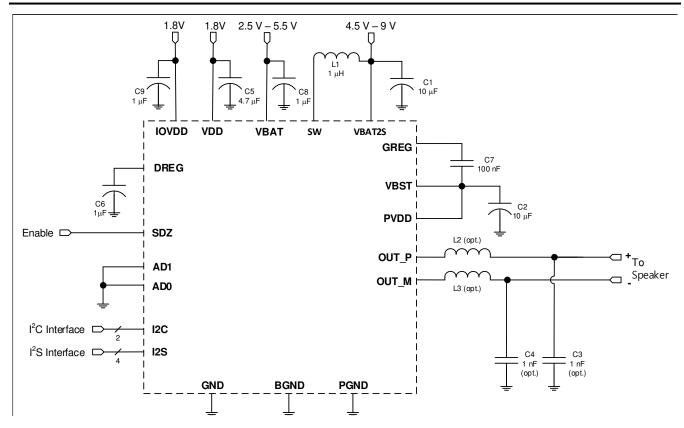

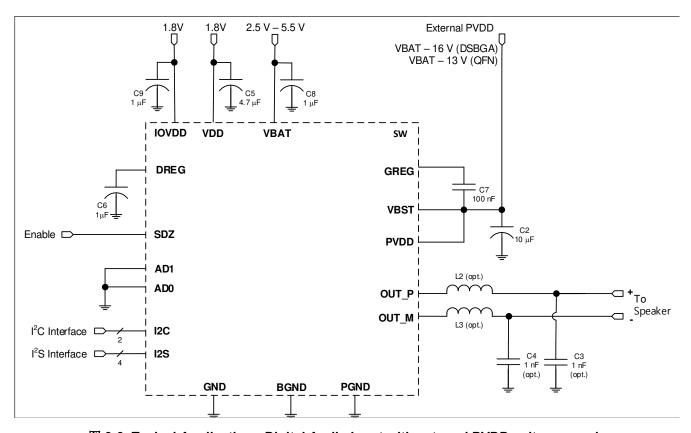

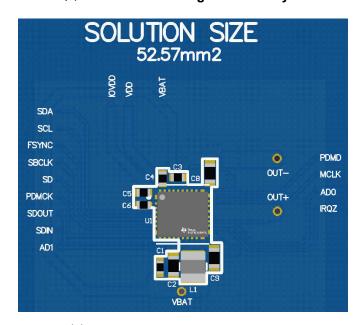

简化原理图

## **Table of Contents**

| 1 特性                                     | 1 | 8.3 Feature Description                        | 30                       |

|------------------------------------------|---|------------------------------------------------|--------------------------|

| 2 应用                                     |   | 8.4 Device Functional Modes                    | 39                       |

| - <i>—,,,,</i><br>3 说明                   |   | 8.5 Register Maps                              | 64                       |

| 4 Revision History                       |   | 9 Application and Implementation               | 95                       |

| 5 Pin Configuration and Functions        |   | 9.1 Application Information                    | 95                       |

| Pin Functions                            |   | 9.2 Typical Application                        | 95                       |

| 6 Specifications                         |   | 10 Power Supply Recommendations                | 99                       |

| 6.1 Absolute Maximum Ratings             |   | 10.1 Power Supplies                            | 99                       |

| 6.2 ESD Ratings                          |   | 10.2 Power Supply Sequencing                   | 99                       |

| 6.3 Recommended Operating Conditions     |   | 11 Layout                                      | 100                      |

| 6.4 Thermal Information                  |   | 11.1 Layout Guidelines                         | 100                      |

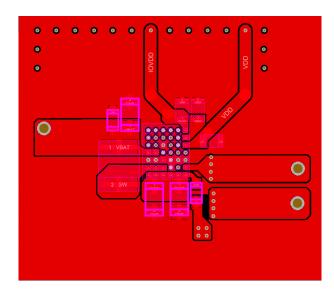

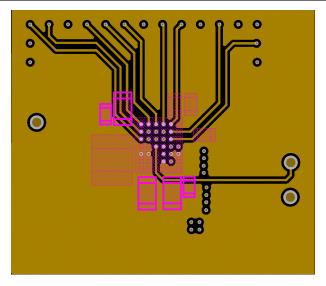

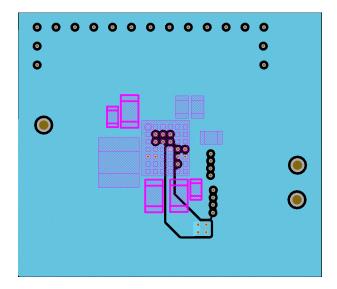

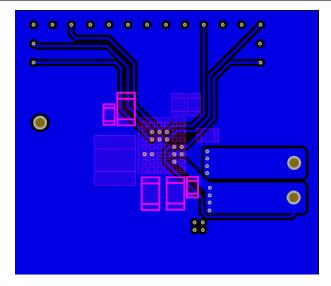

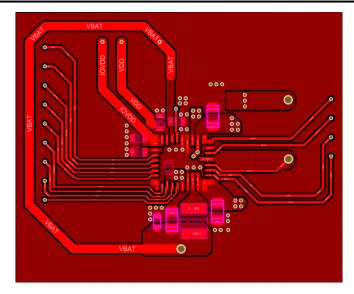

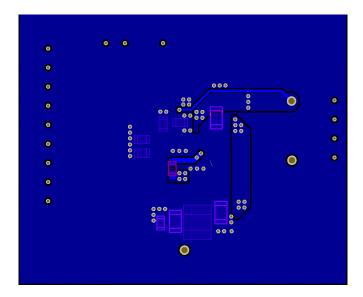

| 6.5 Electrical Characteristics           |   | 11.2 Layout Example                            | 101                      |

| 6.6 I <sup>2</sup> C Timing Requirements |   | 12 Device and Documentation Support            | 105                      |

| 6.7 SPI Timing Requirements              |   | 12.1 Documentation Support                     | 105                      |

| 6.8 PDM Port Timing Requirements         |   | 12.2 Receiving Notification of Documentation U | Jpdates <mark>105</mark> |

| 6.9 TDM Port Timing Requirements         |   | 12.3 支持资源                                      | 105                      |

| 6.10 Timing Diagrams                     |   | 12.4 Trademarks                                | 105                      |

| 6.11 Typical Characteristics             |   | 12.5 Electrostatic Discharge Caution           | 105                      |

| 7 Parameter Measurement Information      |   | 12.6 Glossary                                  |                          |

| 8 Detailed Description                   |   | 13 Mechanical, Packaging, and Orderable        |                          |

| 8.1 Overview                             |   | Information                                    | 105                      |

| 8.2 Functional Block Diagram             |   |                                                |                          |

| <b>U</b>                                 |   |                                                |                          |

**4 Revision History** 注:以前版本的页码可能与当前版本的页码不同

| Cn | langes from Revision B (December 2020) to Revision C (March 2021)  | Page           |

|----|--------------------------------------------------------------------|----------------|

|    | Added QFN THDN Isense                                              |                |

| •  | Removed Idle Channel QFN                                           | 7              |

|    | Added Current Consumption with Speaker Protection ON               |                |

|    | Updated DNR QFN PAckage                                            |                |

| •  | Updated DNR for Isense and Vsense                                  | 7              |

| •  | Removed Group Delay                                                | <mark>7</mark> |

| •  | Updated Captive Load for fast I2C                                  | 14             |

|    | Merged Efficency vs Output Power for both packages                 |                |

| •  | Added AVDD and VBAT Idel Current QFN Package                       | 18             |

|    | Merged Vsense characteristics for both packages                    |                |

| Ch | nanges from Revision A (August 2019) to Revision B (December 2020) | Page           |

| •  | 添加了 RPP 机械数据                                                       | 1              |

|    | 将器件状态更改为"混合量产"                                                     |                |

|    | 添加了 QFN 封装作为"预告信息"                                                 |                |

| Ch | nanges from Revision * (April 2019) to Revision A (August 2019)    | Page           |

|    | 将 TAS2562 从"预告信息"更改为"量产数据"                                         |                |

|    | <del></del>                                                        |                |

# **5 Pin Configuration and Functions**

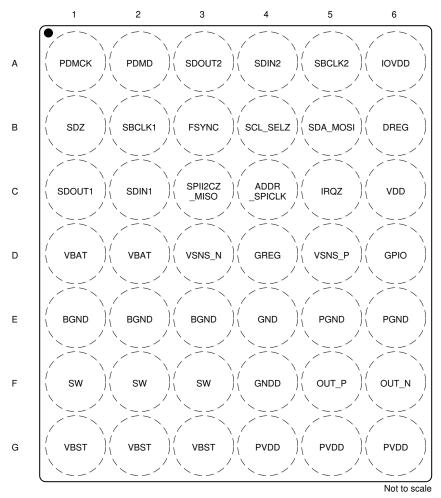

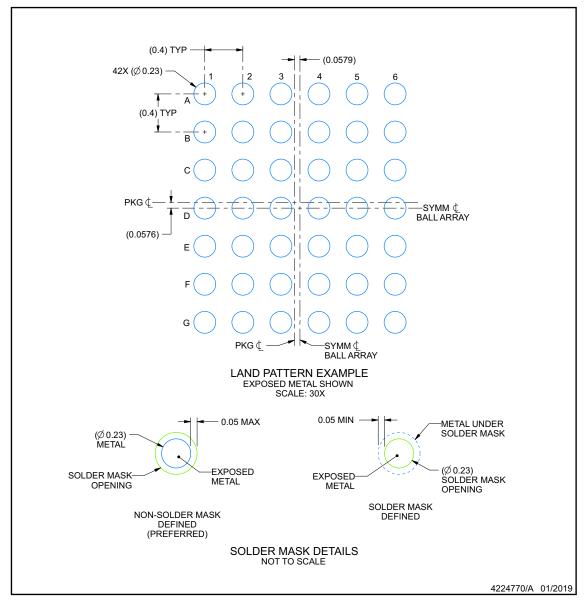

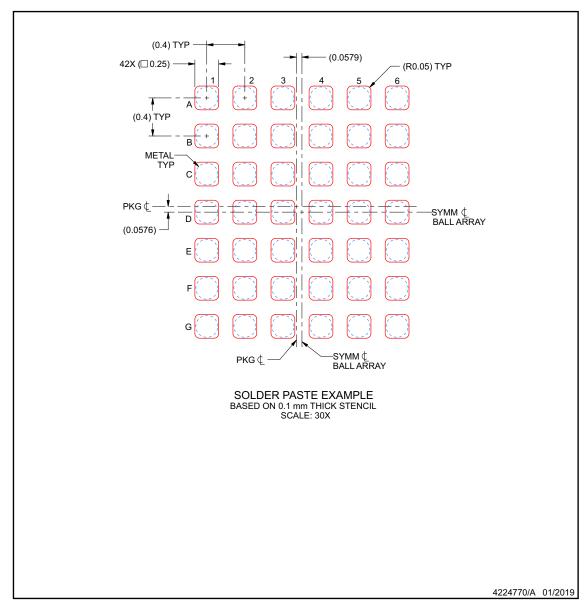

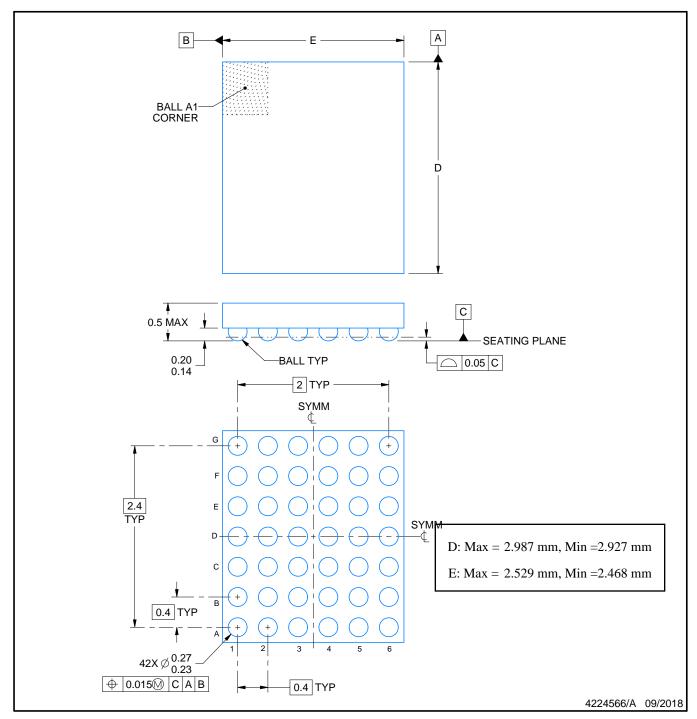

图 5-1. YBG Package 42-Ball DSBGA Top View

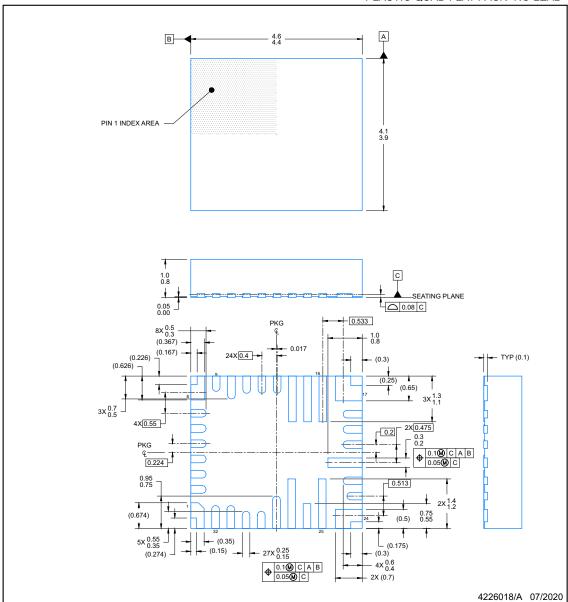

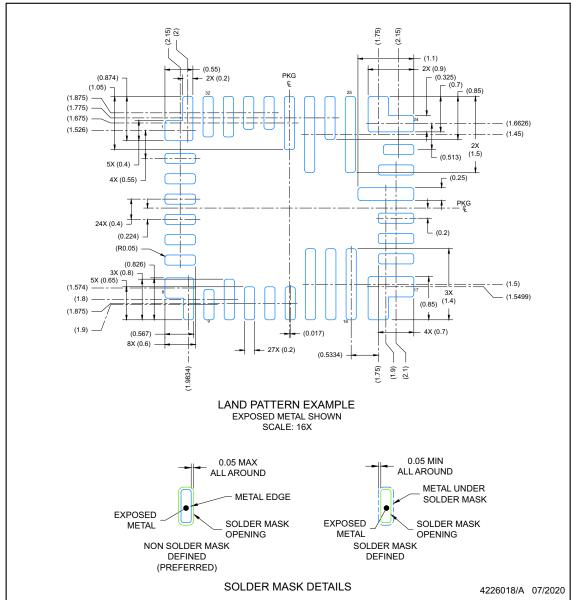

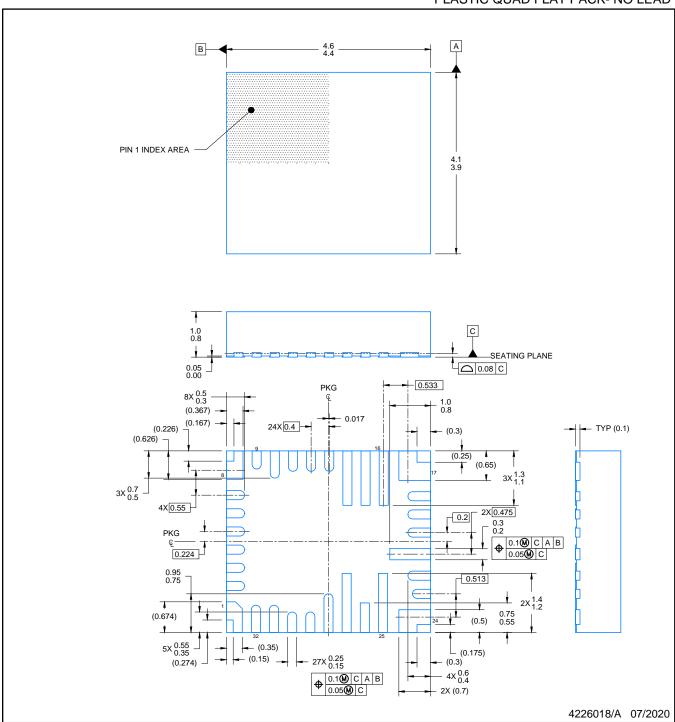

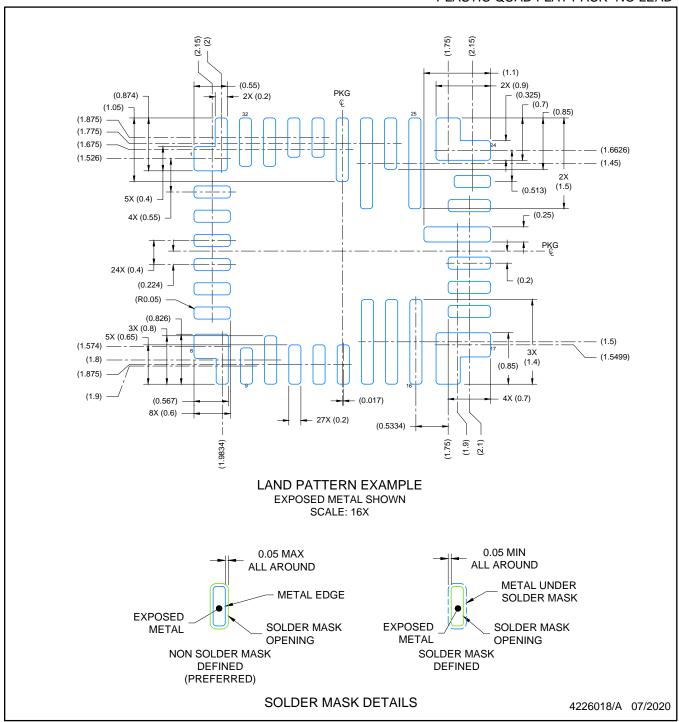

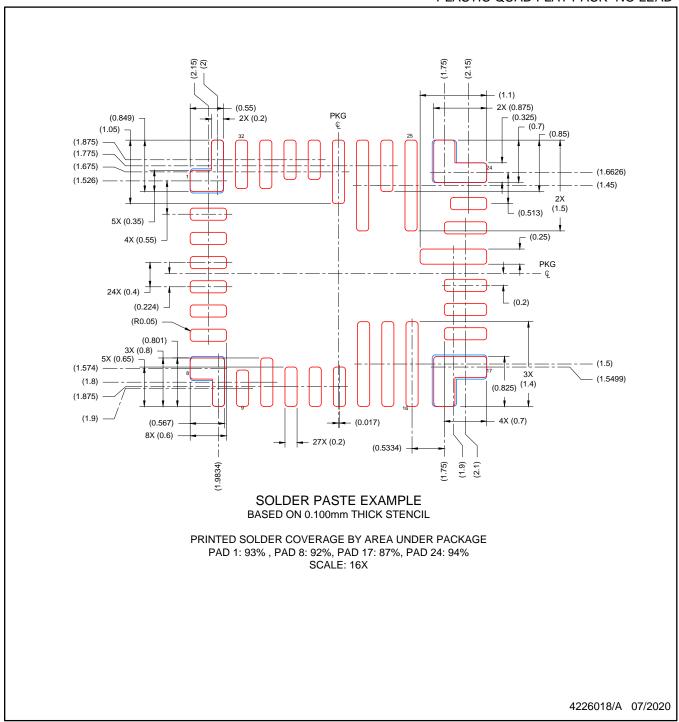

图 5-2. RPP Package 32-pin QFN Top View

## **Pin Functions**

|                 | PIN          |         |      |                                                                                                                |

|-----------------|--------------|---------|------|----------------------------------------------------------------------------------------------------------------|

| NAME            | DSBGA<br>NO. | QFN NO. | TYPE | DESCRIPTION                                                                                                    |

| ADDR_SPI<br>CLK | C4           | 19      | I    | I2C Mode - Address selection pin See General I2C operation. SPI Mode - SPI clock                               |

| DREG            | В6           | 2       | Р    | Digital core voltage regulator output. Bypass to GND with a cap. Do not connect to external load.              |

| FSYNC           | В3           | 5       | I    | I2S word clock or TDM frame sync for ASI1 and ASI2 channels.                                                   |

| GNDB            | E1, E2, E3   | 14      | Р    | Boost ground. Connect to PCB GND plane.                                                                        |

| GNDD            | F4           | 28      | Р    | Digital ground. Connect to PCB GND plane.                                                                      |

| GND             | E4           | N/A     | Р    | Analog ground. Connect to PCB GND plane.                                                                       |

| GNDP            | E5,E6        | 27      | Р    | Power stage ground. Connect to PCB GND plane.                                                                  |

| GPIO            | D6           | 22      | Ю    | General purpose input-ouput or MCLK base on register configuration.                                            |

| GREG            | D4           | 13      | Р    | High-side gate CP regulator output. Do not connect to external load.                                           |

| IOVDD           | A6           | 32      | Р    | 3.3-V/1.8-V IOVDD Supply                                                                                       |

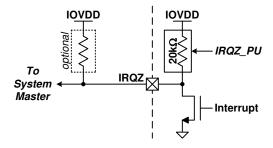

| IRQZ            | C5           | 18      | 0    | Open drain, active low interrupt pin. Pull up to IOVDD with resistor if optional internal pull up is not used. |

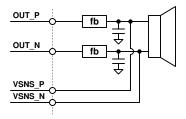

| OUT_N           | F6           | 26      | 0    | Class-D negative output for receiver channel.                                                                  |

| OUT_P           | F5           | 21      | 0    | Class-D positive output for receiver channel.                                                                  |

| PDMCLK          | A1           | 9       | 10   | PDM clock.                                                                                                     |

www.ti.com.cn

|                  | PIN          |          |      |                                                                                                                              |

|------------------|--------------|----------|------|------------------------------------------------------------------------------------------------------------------------------|

| NAME             | DSBGA<br>NO. | QFN NO.  | TYPE | DESCRIPTION                                                                                                                  |

| PDMD             | A2           | 24       | Ю    | PDM data.                                                                                                                    |

| PVDD             | G4, G5, G6   | 25       | Р    | Power stage supply.                                                                                                          |

| SBCLK1           | B2           | 6        | I    | ASI1 channel I2S/TDM serial bit clock.                                                                                       |

| SBCLK2           | A5           |          | I    | ASI2 channel I2S/TDM serial bit clock.                                                                                       |

| SDA_MOSI         | B5           | 3        | Ю    | I2C Mode: I <sup>2</sup> C Data Pin. Pull up to IOVDD with a resistor. SPI Mode: Serial data input pin.                      |

| SDIN1            | C2           | 11       | I    | ASI1 channel I2S/TDM serial data input.                                                                                      |

| SDIN2            | A4           |          | I    | ASI2 channel I2S/TDM serial data input.                                                                                      |

| SDOUT1           | C1           | 10       | Ю    | ASI1 channel I2S/TDM serial data output.                                                                                     |

| SDOUT2           | A3           |          | Ю    | ASI2 channel I2S/TDM serial data output.                                                                                     |

| SDZ              | B1           | 7        | I    | Active low hardware shutdown.                                                                                                |

| SCL_SELZ         | B4           | 4        | Ю    | I2C Mode: I2C clock pin. Pull up to IOVDD with a resistor. SPI Mode: active low chip select.                                 |

| SPII2CZ_MI<br>SO | C3           | 12       | Ю    | Pin is queried on power-up. Short to GND for I2C Mode. Pull to IOVDD with resistor for SPI mode. SPI serial data output pin. |

| SW               | F1, F2, F3   | 15       | Р    | Boost converter switch input.                                                                                                |

| VBAT             | D1, D2       | 30       | Р    | Battery power supply input. Connect to 2.7 V to 5.5 V supply and decouple with a cap.                                        |

| VBST             | G1, G2, G3   | 16       | Р    | Boost converter output. Do not connect to external load.                                                                     |

| VDD              | C6           | 31       | Р    | Analog, digital, and IO power supply. Connect to 1.8 V supply and decouple to GND with cap.                                  |

| VSNS_N           | D3           | 29       | I    | Voltage sense negative input. Connect to Class-D OUT_N output after Ferrite bead filter.                                     |

| VSNS_P           | D5           | 20       | I    | Voltage sense positive input. Connect to Class-D OUT_P output after Ferrite bead filter.                                     |

| NC               |              | 1, 8, 17 |      | No Connect.                                                                                                                  |

## **6 Specifications**

## **6.1 Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                                      |                                      | MIN   | MAX     | UNIT |

|--------------------------------------|--------------------------------------|-------|---------|------|

| IO Supply IOVDD                      | IOVDD                                | -0.3  | 3.9     | V    |

| Analog Voltage                       | VDD                                  | - 0.3 | 2       | V    |

| Battery Supply Voltage               | VBAT                                 | - 0.3 | 6       | V    |

| Boost Pin                            | VBST                                 | -0.3  | 18.5    | V    |

| Power Supply Voltage                 | PVDD <sup>(3)</sup>                  | -0.3  | 18.5    | V    |

| Switching Pin                        | SW                                   | -0.7  | 16      | V    |

| High Side Regulator Pin              | GREG                                 | -0.3  | PVDD+6  | V    |

| Digital Regular Pin                  | DREG                                 | -0.3  | 1.65    | V    |

| Input voltage <sup>(2)</sup>         | Digital IOs referenced to VDD supply | - 0.3 | VDD+0.3 | V    |

| Operating free-air tempe             | rature, T <sub>A</sub>               | - 40  | 85      | °C   |

| Operating junction temper            | erature, T <sub>J</sub>              | - 40  | 150     | °C   |

| Storage temperature, T <sub>st</sub> | g                                    | - 65  | 150     | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings can cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Procedures. Exposure to absolute-maximum-rated conditions for extended periods can affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                                                        | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 OUT_N / OUT_P / VSNS_N / VSNS_P Pins <sup>(1)</sup> | ±3000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>                                      | ±2000 |      |

|                    |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup>                         | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## **6.3 Recommended Operating Conditions**

over operating free-air temperature range (unless otherwise noted)

|                              |                                                      | MIN  | NOM       | MAX  | UNIT |

|------------------------------|------------------------------------------------------|------|-----------|------|------|

| IOVDD                        | IO Supplly Voltage 1.8V                              | 1.62 | 1.8       | 1.98 | V    |

| IOVDD                        | IO Supply Voltage 3.3V                               | 3    | 3.3       | 3.6  | V    |

| VBAT                         | Supply voltage                                       | 2.5  | 3.6       | 5.5  | V    |

| VDD                          | Supply voltage                                       | 1.62 | 1.8       | 1.95 | V    |

| PVDD <sub>DSBGA</sub> (VBST) | Supply voltage - external boost mode (DSBGA package) | VBAT |           | 16   | V    |

| PVDD <sub>QFN</sub> (VBST)   | Supply voltage - external boost mode (QFN package)   | VBAT |           | 13   | V    |

| V <sub>IH</sub>              | High-level digital input voltage                     | 0.   | 7 x IOVDD |      | V    |

| V <sub>IL</sub>              | Low-level digital input voltage                      |      | 0         |      | V    |

| R <sub>SPK</sub>             | Minimum speaker impedance                            | 3.2  |           |      | Ω    |

| L <sub>SPK</sub>             | Minimum speaker inductance                           | 10   |           |      | μН   |

Product Folder Links: TAS2563

<sup>(2)</sup> All digital inputs and IOs are failsafe.

<sup>(3)</sup> PVDD can handle 19V transients for less than 10ns

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## **6.4 Thermal Information**

|                        |                                              | TAS       | 2563       |      |

|------------------------|----------------------------------------------|-----------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RPP (QFN) | YBG (WCSP) | UNIT |

|                        |                                              | 32 PINS   | 42 PINS    |      |

| R <sub>0</sub> JA      | Junction-to-ambient thermal resistance       | 43.7      | 55.3       | °C/W |

| R <sub>θ JC(top)</sub> | Junction-to-case (top) thermal resistance    | 20.3      | 0.3        | °C/W |

| R <sub>θ JB</sub>      | Junction-to-board thermal resistance         | 10.5      | 11.6       | °C/W |

| ψ JT                   | Junction-to-top characterization parameter   | 0.5       | 0.2        | °C/W |

| ψ ЈВ                   | Junction-to-board characterization parameter | 10.5      | 11.6       | °C/W |

| R <sub>θ JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | N/A       | N/A        | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

### 6.5 Electrical Characteristics

|                      | PARAMETER                                                                               | TEST CONDITIONS                                                               | MIN               | TYP  | MAX             | UNIT |

|----------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------|------|-----------------|------|

| DIGITAL IN           | _                                                                                       |                                                                               |                   |      |                 |      |

| V <sub>IH</sub>      | High-level digital input logic voltage threshold (max current limit = 30 mA)            | All digital pins except SDA_MOSI and SCL_SELZ                                 | 0.65 ×<br>IOVDD   |      |                 | V    |

| V <sub>IL</sub>      | Low-level digital input logic voltage threshold (max current limit = 30 mA)             | All digital pins except SDA_MOSI and SCL_SELZ                                 |                   |      | 0.35 ×<br>IOVDD | V    |

| V <sub>IH(I2C)</sub> | High-level digital input logic voltage threshold (max current limit = 30 mA)            | SDA_MOSI and SCL_SELZ                                                         | 0.7 ×<br>IOVDD    |      |                 | V    |

| V <sub>IL(I2C)</sub> | Low-level digital input logic voltage threshold (max current limit = 30 mA)             | SDA_MOSI and SCL_SELZ                                                         |                   |      | 0.3 ×<br>IOVDD  | V    |

| V <sub>OH</sub>      | High-level digital output voltage (max current limit = 30 mA)                           | All digital pins except SDA_MOSI ,SCL_SELZ and IRQZ; I <sub>OH</sub> = 2 mA.  | IOVDD -<br>0.45 V |      |                 | V    |

| V <sub>OL</sub>      | Low-level digital output voltage (max current limit = 30 mA)                            | All digital pins except SDA_MOSI ,SCL_SELZ and IRQZ; I <sub>OL</sub> = -2 mA. |                   |      | 0.45            | V    |

| V <sub>OL(I2C)</sub> | Low-level digital output voltage (max current limit = 30 mA)                            | SDA and SCL; I <sub>OL(I2C)</sub> = -2 mA.                                    |                   |      | 0.2 ×<br>IOVDD  | V    |

| $V_{OL(IRQZ)}$       | Low-level digital output voltage for IRQZ open drain Output (max current limit = 30 mA) | IRQZ; I <sub>OL(IRQZ)</sub> = -2 mA.                                          |                   |      | 0.45            | V    |

| I <sub>IH</sub>      | Input logic-high leakage for digital inputs                                             | All digital pins; Input = VDD.                                                | - 5               | 0.1  | 5               | μА   |

| I <sub>IL</sub>      | Input logic-low leakage for digital inputs                                              | All digital pins; Input = GND.                                                | - 5               | 0.1  | 5               | μΑ   |

| C <sub>IN</sub>      | Input capacitance for digital inputs                                                    | All digital pins                                                              |                   | 8    |                 | pF   |

| R <sub>PD</sub>      | Pull down resistance for digital input/IO pins when asserted on                         | SDOUT, SDIN, FSYNC, SBCLK                                                     |                   | 50   |                 | kΩ   |

| AMPLIFIE             | R PERFORMANCE - Internal Boost                                                          |                                                                               |                   |      |                 |      |

|                      | Output Voltage for Full-scale digital Input                                             | Measured at -6 dB FS input                                                    |                   | 6.32 |                 | Vrms |

|                  | PARAMETER                                    | TEST CONDITIONS                                                                     | MIN TYP MA | X UNIT |

|------------------|----------------------------------------------|-------------------------------------------------------------------------------------|------------|--------|

|                  |                                              | $R_L$ = 32 Ω + 33 μH, THD+N = 0.03 %, $f_{in}$ = 1 kHz                              | 1.25       | W      |

| P <sub>OUT</sub> | Maximum Continuous Output Power              | $R_L$ = 8 $\Omega$ + 33 $\mu$ H, THD+N = 0.03 %, $f_{in}$ = 1 kHz                   | 5          | W      |

|                  |                                              | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, THD+N = 1 %, $f_{in}$ = 1 kHz             | 6.1        | W      |

|                  |                                              | R <sub>L</sub> = 8 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz,<br>DSBGA package | 82         | %      |

|                  |                                              | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz, QFN package                                  | 81.3       | %      |

|                  |                                              | $R_L = 4 \Omega + 33 \mu H$ , $f_{in} = 1 \text{ kHz}$                              | 78.5       | %      |

|                  | System efficiency at P <sub>OUT</sub> = 1 W  | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz, VBAT = 4.2 V, DSBGA package                  | 82.5       | %      |

|                  |                                              | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz, VBAT = 4.2 V, QFN package                    | 81.7       | %      |

|                  |                                              | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, VBAT = 4.2 V     | 84.2       | %      |

|                  |                                              | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz, DSGBA package                                | 76.6       | %      |

|                  |                                              | $R_L$ = 8 $\Omega$ + 33 $\mu$ H, $f_{in}$ = 1 kHz, QFN                              | 75.8       | %      |

|                  | System efficiency at P <sub>OUT</sub> =0.5 W | $R_L = 4 \Omega + 33 \mu H$ , $f_{in} = 1 kHz$                                      | 81.1       | %      |

|                  | System smarting at 1 001 one in              | R <sub>L</sub> = 8 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, VBAT = 4.2 V     | 84.2       | %      |

|                  |                                              | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, VBAT = 4.2 V     | 81.6       | %      |

|                  |                                              | $P_{OUT}$ = 0.25 W, $R_L$ = 32 $\Omega$ + 33 $\mu$ H, $f_{in}$ = 1 kHz              | 0.01       | %      |

| THD+N            | Total harmonic distortion + noise            | $P_{OUT}$ = 1 W, R <sub>L</sub> = 8 Ω + 33 μH, $f_{in}$ = 1 kHz                     | 0.01       | %      |

|                  |                                              | $P_{OUT}$ = 1 W, $R_L$ = 4 Ω + 33 μH, $f_{in}$ = 1 kHz                              | 0.01       | %      |

| / <sub>N</sub>   | Idle channel noise                           | A-Weighted, 20 Hz - 20 kHz, DAC<br>Modulator Running                                | 14.8       | μV     |

|                  |                                              | Average frequency in Spread<br>Spectrum Mode, CLASSD_SYNC=0                         | 384        | kHz    |

|                  |                                              | Fixed Frequency Mode,<br>CLASSD_SYNC=0                                              | 384        | kHz    |

| PWM              | Class-D PWM switching frequency              | Fixed Frequency Mode,<br>CLASSD_SYNC=1, f <sub>s</sub> = 44.1, 88.2,<br>174.6 kHz   | 352.8      | kHz    |

|                  |                                              | Fixed Frequency Mode,<br>CLASSD_SYNC=1, f <sub>s</sub> = 48, 96, 192<br>kHz         | 384        | kHz    |

| /os              | Output offset voltage                        |                                                                                     | -1         | 1 mV   |

| ONR              | Dynamic range, DSBGA Package                 | A-Weighted, -60 dBFS Method                                                         | 109        | dB     |

| ONR              | Dynamic range, QFN Package                   | A-Weighted, -60 dBFS Method                                                         | 105        | dB     |

| SNR              | Signal to noise ratio                        | A-Weighted, Referenced to 1 %<br>THD+N Output Level                                 | 112.5      | dB     |

www.ti.com.cn

|                     | PARAMETER                                   | TEST CONDITIONS                                                                                                        | MIN TYP | MAX | UNIT |

|---------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| K <sub>CP</sub>     | Click and pop performance                   | Into and out of Mute, Shutdown, Power Up, Power Down and audio clocks starting and stopping. Measured with APx Plugin. | 3.4     |     | mV   |

|                     | Programmable output level range             |                                                                                                                        | 8       | 18  | dBV  |

|                     | Programmable output level step size         |                                                                                                                        | 0.5     |     | dB   |

| AV <sub>ERROR</sub> | Amplifier gain error                        | P <sub>OUT</sub> = 1 W                                                                                                 | ±0.1    |     | dB   |

|                     | Mute attenuation                            | Device in Shutdown or Muted in Normal Operation                                                                        | 110     |     | dB   |

|                     | VBAT power-supply rejection ratio           | VBAT = 3.6 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                                     | 108     |     | dB   |

|                     | VDAT power-supply rejection ratio           | VBAT = 3.6 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                                     | 90      |     | dB   |

|                     | AVDD power-supply rejection ratio           | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                                      | 98      |     | dB   |

|                     | Power-supply rejection ratio                | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                                      | 93      |     | dB   |

|                     | Turn on time from release of SW             | No Volume Ramping                                                                                                      | 1.8     |     | ms   |

|                     | shutdown                                    | Volume Ramping                                                                                                         | 4.5     |     | ms   |

|                     | Turn off time from assertion of SW          | No Volume Ramping                                                                                                      | 1.5     |     | ms   |

|                     | shutdown to amp Hi-Z                        | Volume Ramping                                                                                                         | 12.5    |     | ms   |

| AMPLIFIEI           | R PERFORMANCE - External PVDD               |                                                                                                                        |         |     |      |

|                     | Output Voltage for Full-scale digital Input | Measured at -6 dB FS input                                                                                             | 7.94    |     | Vrms |

|                     |                                             | $R_L$ = 32 Ω + 33 μH, THD+N = 1 %, $f_{in}$ = 1 kHz                                                                    | 1.3     |     | W    |

|                     |                                             | R <sub>L</sub> = 8 $\Omega$ + 33 $\mu$ H, THD+N = 1 %, f <sub>in</sub> = 1 kHz                                         | 5.2     |     | W    |

| D                   | Mayimum Cantinuaua Output Dayyar            | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, THD+N = 1 %, f <sub>in</sub> = 1 kHz                                         | 10.4    |     | W    |

| Роит                | Maximum Continuous Output Power             | $R_L = 32 \Omega + 33 \mu H$ , THD+N = 10 %, $f_{in} = 1 \text{ kHz}$                                                  | 1.6     |     | W    |

|                     |                                             | $R_L$ = 8 $\Omega$ + 33 $\mu$ H, THD+N = 10 %, $f_{in}$ = 1 kHz                                                        | 6.3     |     | W    |

|                     |                                             | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, THD+N = 10%, $f_{in}$ = 1 kHz                                                | 12.6    |     | W    |

|                     |                                             | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz                                                                                  | 83.8    |     | %    |

|                     |                                             | $R_L = 4 \Omega + 33 \mu H, f_{in} = 1 \text{ kHz}$                                                                    | 80      |     | %    |

|                     | System efficiency at P <sub>OUT</sub> = 1 W | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz,<br>External PVDD = 8.4 V                                                        | 85.9    |     | %    |

|                     |                                             | $R_L$ = 4 Ω + 33 μH, $f_{in}$ = 1 kHz,<br>External PVDD = 8.4 V                                                        | 81.8    |     | %    |

|                     |                                             | $P_{OUT}$ = 0.25 W, $R_L$ = 32 $\Omega$ + 33 $\mu$ H, $f_{in}$ = 1 kHz                                                 | 0.01    |     | %    |

| THD+N               | Total harmonic distortion + noise           | $P_{OUT}$ = 1 W, $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz                                                                 | 0.01    |     | %    |

|                     |                                             | $P_{OUT}$ = 1 W, $R_L$ = 4 Ω + 33 μH, $f_{in}$ = 1 kHz                                                                 | 0.02    |     | %    |

| V <sub>N</sub>      | Idle channel noise                          | A-Weighted, 20 Hz - 20 kHz, DAC<br>Modulator Running                                                                   | 21.3    |     | μV   |

|                     | PARAMETER                               | TEST CONDITIONS                                                                                                        | MIN TYP MAX | UNIT |

|---------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------|------|

|                     |                                         | Average frequency in Spread<br>Spectrum Mode, CLASSD_SYNC=0                                                            | 384         | kHz  |

|                     |                                         | Fixed Frequency Mode,<br>CLASSD_SYNC=0                                                                                 | 384         | kHz  |

| F <sub>PWM</sub>    | Class-D PWM switching frequency         | Fixed Frequency Mode,<br>CLASSD_SYNC=1, f <sub>s</sub> = 44.1, 88.2,<br>174.6 kHz                                      | 352.8       | kHz  |

|                     |                                         | Fixed Frequency Mode,<br>CLASSD_SYNC=1, f <sub>s</sub> = 48, 96, 192<br>kHz                                            | 384         | kHz  |

| V <sub>OS</sub>     | Output offset voltage                   |                                                                                                                        | -1          | mV   |

| DNR                 | Dynamic range                           | A-Weighted, -60 dBFS Method                                                                                            | 109         | dB   |

| SNR                 | Signal to noise ratio                   | A-Weighted, Referenced to 1 % THD+N Output Level                                                                       | 109         | dB   |

| K <sub>CP</sub>     | Click and pop performance               | Into and out of Mute, Shutdown, Power Up, Power Down and audio clocks starting and stopping. Measured with APx Plugin. | 3           | mV   |

|                     | Programmable output level range         |                                                                                                                        | 8 18        | dBV  |

|                     | Programmable output level step size     |                                                                                                                        | 0.5         | dB   |

| AV <sub>ERROR</sub> | Amplifier gain error                    | P <sub>OUT</sub> = 1 W                                                                                                 | ±0.1        | dB   |

|                     | Mute attenuation                        | Device in Shutdown or Muted in Normal Operation                                                                        | 110         | dB   |

|                     | VBAT power-supply rejection ratio       | VBAT = 3.6 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                                     | 110         | dB   |

|                     |                                         | VBAT = 3.6 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                                     | 90          | dB   |

|                     | DVDD results out to the section and the | PVDD = 12 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                                      | 105         | dB   |

|                     | PVDD power-supply rejection ratio       | PVDD = 12 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                                      | 90          | dB   |

|                     | AVDD power-supply rejection ratio       | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 217 Hz                                                      | 86          | dB   |

|                     | AVBB power-supply rejection ratio       | VDD = 1.8 V + 200 mV <sub>pp</sub> , f <sub>ripple</sub> = 20 kHz                                                      | 73          | dB   |

|                     | Turn on time from release of SW         | No Volume Ramping                                                                                                      | 2           | ms   |

|                     | shutdown                                | Volume Ramping                                                                                                         | 4.8         | ms   |

|                     | Turn off time from assertion of SW      | No Volume Ramping                                                                                                      | 1.1         | ms   |

|                     | shutdown to amp Hi-Z                    | Volume Ramping                                                                                                         | 12.6        | ms   |

| BOOST<br>CONVERT    | ER                                      |                                                                                                                        |             |      |

|                     | Startup inrush current limit            | default setting                                                                                                        | 1.5         | Α    |

|                     | Startup inrush limit time               | default setting                                                                                                        | 0.45        | ms   |

|                     | Switching Frequency                     | PFM mode                                                                                                               | 50          | kHz  |

|                     | - Cwitching Frequency                   | Current Control Mode                                                                                                   | 4           | MHz  |

|                     | Inductor Peak Current Limit             | default setting                                                                                                        | 4           | А    |

| DIE TEMP<br>SENSOR  | ERATURE                                 |                                                                                                                        |             |      |

|                     | Resolution                              |                                                                                                                        | 8           | bits |

|                     | Die temperature measurement range       |                                                                                                                        | -40 150     | °C   |

www.ti.com.cn

|                  | PARAMETER                                                | TEST CONDITIONS                                                                                                    | MIN   | TYP   | MAX   | UNIT   |

|------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

|                  | Die temperature resolution                               |                                                                                                                    |       | 0.75  |       | °C     |

|                  | Die temperature accuracy                                 |                                                                                                                    |       | ±5    |       | °C     |

| VOLTAG<br>MONITO | E                                                        |                                                                                                                    |       |       |       |        |

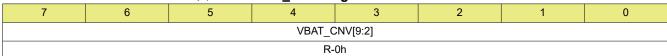

|                  | Resolution                                               |                                                                                                                    |       | 10    |       | bits   |

|                  | VBAT measurement range                                   |                                                                                                                    | 2     |       | 6     | V      |

|                  | VBAT resolution                                          |                                                                                                                    |       | 6     |       | mV     |

|                  | VBAT accuracy                                            |                                                                                                                    |       | ±25   |       | mV     |

| PDM INP          | PUT PORT                                                 |                                                                                                                    |       |       |       |        |

| 0110             | 0: 11 N : 5 1:                                           | No signal, Input generated using a 4 <sup>th</sup> order PDM modulator                                             |       | 118   |       |        |

| SNR              | Signal to Noise Ratio                                    | No signal, Input generated using a 5 <sup>th</sup> order PDM modulator                                             |       | 128   |       | dB     |

| DR               | Dynamic Range                                            | 20Hz to 20kHz, -60dBFS input<br>signal, A-weighted, Input generated<br>using a 4 <sup>th</sup> order PDM modulator |       | 117   |       | dB     |

| DIX              | Dynamic realige                                          | 20Hz to 20kHz, -60dBFS input<br>signal, A-weighted, Input generated<br>using a 5 <sup>th</sup> order PDM modulator |       | 127   |       | uБ     |

| FR               | Frequency Response                                       | 20Hz to 20kHz                                                                                                      | -0.1  |       | 0     | dB     |

| TDM SEF<br>PORT  | RIAL AUDIO                                               |                                                                                                                    |       |       | ·     |        |

|                  | PCM Sample Rates & FSYNC Input Frequency                 |                                                                                                                    | 8     |       | 96    | kHz    |

|                  | SBCLK Input Frequency                                    | I <sup>2</sup> S/TDM Operation                                                                                     | 0.512 |       | 24.57 | MHz    |

|                  | SBCLK Maximum Input Jitter                               | RMS Jitter below 40 kHz that can be tolerated without performance degradation                                      |       |       | 1     | ns     |

|                  |                                                          | RMS Jitter above 40 kHz that can be tolerated without performance degradation                                      |       |       | 10    | ns     |

|                  | SBCLK Cycles per FSYNC in I <sup>2</sup> S and TDM Modes | Values: 64, 96, 128, 192, 256, 384 and 512                                                                         | 64    |       | 512   | Cycles |

| PCM PLA          | AYBACK<br>CTERISTICS to fs ≤ 48 kHz                      |                                                                                                                    |       |       |       |        |

| fs               | Sample Rates                                             |                                                                                                                    | 8     |       | 48    | kHz    |

|                  | Passband LPF Corner                                      |                                                                                                                    | ,     | 0.454 |       | fs     |

|                  | Passband Ripple                                          | 20 Hz to LPF cutoff                                                                                                | -0.3  |       | 0.3   | dB     |

|                  | 2. 2 :                                                   | ≥ 0.55 fs                                                                                                          |       | 60    |       | dB     |

|                  | Stop Band Attenuation                                    | ≥ 1 fs                                                                                                             |       | 65    |       | dB     |

|                  | Group Delay (ROM MODE)                                   | DC to 0.454 fs                                                                                                     |       |       | 38    | 1/fs   |

|                  | AYBACK<br>CTERISTICS fs > 48 kHz                         |                                                                                                                    |       |       |       |        |

| fs               | Sample Rates                                             |                                                                                                                    | 88.2  |       | 96    | kHz    |

|                  | ·                                                        | fs = 96 kHz                                                                                                        |       | 0.42  |       | fs     |

|                  | Passband LPF Corner                                      | fs = 192 kHz                                                                                                       |       | 0.21  |       | fs     |

|                  | Passband Ripple                                          | DC to LPF cutoff                                                                                                   | -0.5  |       | 0.5   | dB     |

|                  |                                                          | ≥ 0.55 fs                                                                                                          |       | 60    | 0.0   | dB     |

|                  | Stop Band Attenuation                                    | ≥ 0.55 is<br>≥ 1 fs                                                                                                |       | 65    |       | dB     |

|                  |                                                          | > 1 IS                                                                                                             |       | UO    |       | uD     |

|                                   | PARAMETER                                              | TEST CONDITIONS                                                                           | MIN TYP | MAX  | UNIT     |

|-----------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------------|---------|------|----------|

| CURREN <sup>1</sup><br>SENSE      | Г                                                      |                                                                                           |         |      |          |

| DNR                               | Dynamic range, DSBGA Package                           | Un-Weighted, Relative to 0 dBFS                                                           | 69      |      | dB       |

| ONR                               | Dynamic range, QFN Package                             | Un-Weighted, Relative to 0 dBFS                                                           | 65      |      | dB       |

| Total harmonic distortion + noise | $R_L$ = 8 Ω + 33 μH, $f_{in}$ = 1 kHz, $P_{OUT}$ = 1 W | -56                                                                                       |         | dB   |          |

| THD+N                             | DSBGA package                                          | R <sub>L</sub> = 4 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, P <sub>OUT</sub> = 1 W | -57     |      | dB       |

| TUD : N                           | Total harmonic distortion + noise,                     | R <sub>L</sub> = 8 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, P <sub>OUT</sub> = 1 W | -54.5   |      | dB       |

| THD+N                             | QFN package                                            | $R_L$ = 4 Ω + 33 μH, $f_{in}$ = 1 kHz, $P_{OUT}$ = 1 W                                    | -54.7   |      | dB       |

|                                   | Full-scale input current                               |                                                                                           | 2.0     |      | Α        |

|                                   | Current-sense accuracy                                 | $R_L$ = 8 Ω + 33 μH, $I_{OUT}$ = 354 $MA_{RMS}$ ( $P_{OUT}$ = 1 W @ 1kHz)                 | ±1      |      | %        |

|                                   | Current-sense gain error over temperature              | 0°C to 70°C, 8 $\Omega$ , using a 60Hz -40dB pilot tone                                   | ±1      |      | %        |

|                                   | Current-sense gain error over output power             | 50mW to 0.1 % THD+N level, $f_{in}$ = 1 kHz, 8 $\Omega$ , using a 60Hz -40dB pilot tone   | ±1.5    |      | %        |

|                                   |                                                        | fs = 8 kHz to 48 kHz                                                                      | 0.417   |      | fs       |

|                                   | LPF passband corner                                    | fs = 88.2 kHz                                                                             | 0.208   |      | fs       |

|                                   |                                                        | fs = 96 kHz                                                                               | 0.208   |      | fs       |

|                                   | LPF passband ripple                                    |                                                                                           | -0.05   | 0.05 | dB       |

|                                   | LPF stopband attenuation                               | 0.55 fs                                                                                   | 60      |      | dB       |

| VOLTAGE<br>SENSE                  | :                                                      |                                                                                           |         |      |          |

| DNR                               | Dynamic range, DSBGA Package                           | Un-Weighted, Relative 0 dBFS                                                              | 69      |      | dB       |

| DNR                               | Dynamic range, QFN Package                             | Un-Weighted, Relative 0 dBFS                                                              | 66      |      | dB       |

| THD+N                             | Tatal bassassia distantian parisa                      | R <sub>L</sub> = 8 $\Omega$ + 33 $\mu$ H, f <sub>in</sub> = 1 kHz, P <sub>OUT</sub> = 1W  | -60     |      | dB       |

| THUTN                             | Total harmonic distortion + noise                      | $R_L$ = 4 Ω + 33 μH, $f_{in}$ = 1 kHz, $P_{OUT}$ = 1W                                     | -60     |      | dB       |

|                                   | Full-scale input voltage                               |                                                                                           | 14      |      | $V_{PK}$ |

|                                   | Voltage-sense accuracy                                 | $R_L$ = 8 Ω + 33 μH, $I_{OUT}$ = 354 $mA_{RMS}$ ( $P_{OUT}$ = 1 W)                        | ±0.5%   |      |          |

|                                   | Voltage-sense gain error over temperature              | 0°C to 70°C, 8 $^{\Omega}$ , using a 60Hz -40dB pilot tone                                | ±0.5%   |      |          |

|                                   | Voltage-sense gain error over output power             | 50mV to 0.1 % THD+N level, 8 $^{\Omega}$ , using a 60Hz -40dB pilot tone                  | ±0.5%   |      |          |

|                                   |                                                        | fs = 14.7 kHz to 48 kHz                                                                   | 0.417   |      | fs       |

|                                   | LPF passband corner                                    | fs = 88.2 kHz                                                                             | 0.208   |      | fs       |

|                                   |                                                        | fs = 96 kHz                                                                               | 0.208   |      | fs       |

|                                   | LPF passband ripple                                    |                                                                                           | -0.05   | 0.05 | dB       |

|                                   |                                                        | -                                                                                         | 60      |      | dB       |

www.ti.com.cn

|                       | PARAMETER                                                          | TEST CONDITIONS                                                                    | MIN TYP MAX | UNIT |

|-----------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------|------|

| C                     | Gain ratio error over output power                                 | 50mW to 0.1 % THD+N level, fin = 1 kHz, 8 $\Omega$ , using a 60Hz -40dB pilot tone | ±1%         |      |

| C                     | Gain ratio drift over temperature                                  | 0°C to 70°C                                                                        | ±1%         |      |

| \                     | //I phase error                                                    |                                                                                    | 300         | ns   |

| YPICAL CU<br>ONSUMPTI |                                                                    |                                                                                    |             |      |

| C                     | Current consumption in hardware                                    | SDZ = 0, VBAT                                                                      | 1           | μA   |

| s                     | shutdown                                                           | SDZ = 0, VDD                                                                       | 1           | μA   |

| C                     | Current consumption in software                                    | All Clocks Stopped, VBAT                                                           | 1           | μA   |

| s                     | shutdown                                                           | All Clocks Stopped, VDD                                                            | 10          | μΑ   |

| C                     | Current consumption in idle channel,                               | Clocking 0s PCM mode, VBAT                                                         | 2.7         | mA   |

|                       | OSBGA Package                                                      | Clocking 0s PCM mode, VDD                                                          | 10.9        | mA   |

|                       |                                                                    | f <sub>s</sub> = 48 kHz, VBAT                                                      | 4.6         | mA   |

|                       | Current consumption during active operation with IV sense disabled | f <sub>s</sub> = 48 kHz, VDD, DSBGA Package                                        | 10.9        | mA   |

|                       | operation with tv sense disabled                                   | f <sub>s</sub> = 48 kHz, VDD, QFN Package                                          | 13.2        | mA   |

|                       |                                                                    | f <sub>s</sub> = 48 kHz, VBAT                                                      | 4.6         | mA   |

|                       | Current consumption during active operation with IV sense enabled  | f <sub>s</sub> = 48 kHz, VDD, DSBGA Package                                        | 12.5        | mA   |

|                       | operation with the series enabled                                  | f <sub>s</sub> = 48 kHz, VDD, QFN Package                                          | 14.8        | mA   |

| C                     | Current consumption during active                                  | f <sub>s</sub> = 48 kHz, VBAT                                                      | 4.95        | mA   |

| c                     | pperation with speaker protection                                  | f <sub>s</sub> = 48 kHz, VDD, DSBGA Package                                        | 28.8        | mA   |

| C                     | ON                                                                 | f <sub>s</sub> = 48 kHz, VDD, QFN Package                                          | 36          | mA   |

| ROTECTION CIRCUITRY   | N                                                                  |                                                                                    |             |      |

| Т                     | Thermal shutdown temperature                                       |                                                                                    | 140         | °C   |

| Т                     | Thermal shutdown retry                                             |                                                                                    | 1.5         | S    |

| \                     | /BAT undervoltage lockout threshold                                | UVLO is asserted                                                                   | 2           | V    |

| (                     | UVLO)                                                              | UVLO is released                                                                   | 2.55        | 5 V  |

| C                     | Output short circuit limit                                         | Output to Output, Output to GND,<br>Output to VBST or Output to VBAT<br>Short      | 3.75        | А    |

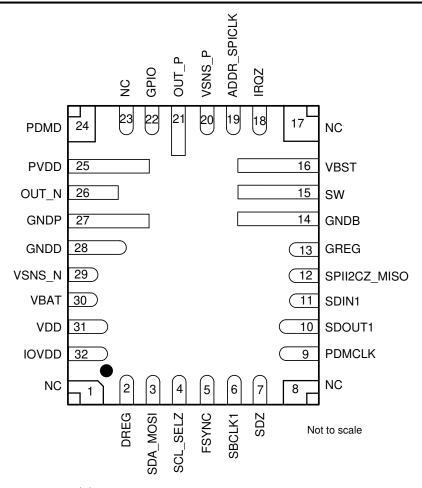

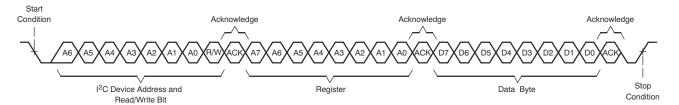

**6.6 I<sup>2</sup>C Timing Requirements**T<sub>A</sub> = 25 °C, VDD = 1.8 V (unless otherwise noted)

|                     |                                                                                              | MIN              | NOM N | AX       | UNIT       |

|---------------------|----------------------------------------------------------------------------------------------|------------------|-------|----------|------------|

| Standard-N          | lode                                                                                         |                  |       |          |            |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                |       | 100      | kHz        |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 4                |       |          | μs         |

| Low                 | LOW period of the SCL clock                                                                  | 4.7              |       |          | μ <b>s</b> |

| HIGH                | HIGH period of the SCL clock                                                                 | 4                |       |          | μs         |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 4.7              |       |          | μs         |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                | 3     | .45      | μs         |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 250              |       |          | ns         |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        |                  | 1     | 000      | ns         |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        |                  |       | 300      | ns         |

| t <sub>su;sto</sub> | Set-up time for STOP condition                                                               | 4                |       |          | μs         |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 4.7              |       |          | μ <b>s</b> |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |                  | ,     | 400      | pF         |

| Fast-Mode           |                                                                                              |                  |       |          |            |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                | ,     | 400      | kHz        |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.6              |       |          | μs         |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 1.3              |       |          | μS         |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.6              |       |          | μs         |

| t <sub>SU;STA</sub> | Setup time for a repeated START condition                                                    | 0.6              |       |          | μ <b>s</b> |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                |       | 0.9      | μS         |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 100              |       |          | ns         |

| t <sub>r</sub>      | SDA and SCL rise time                                                                        | 20 + 0.1 ×<br>Cb |       | 300      | ns         |

| t <sub>f</sub>      | SDA and SCL fall time                                                                        | 20 + 0.1 ×<br>Cb |       | 300      | ns         |

| t <sub>su;sто</sub> | Set-up time for STOP condition                                                               | 0.6              |       |          | μs         |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 1.3              |       |          | μs         |

| C <sub>b</sub>      | Capacitive load for each bus line                                                            |                  | ,     | 400      | pF         |

| Fast-Mode<br>Plus   |                                                                                              |                  |       |          |            |

| f <sub>SCL</sub>    | SCL clock frequency                                                                          | 0                | 1     | 000      | kHz        |

| t <sub>HD;STA</sub> | Hold time (repeated) START condition. After this period, the first clock pulse is generated. | 0.26             |       |          | μS         |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                                                  | 0.5              |       |          | μs         |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                 | 0.26             |       |          | μs         |

| t <sub>su;sta</sub> | Setup time for a repeated START condition                                                    | 0.26             |       |          | μS         |

| t <sub>HD;DAT</sub> | Data hold time: For I <sup>2</sup> C bus devices                                             | 0                |       |          | μ <b>s</b> |

| t <sub>SU;DAT</sub> | Data set-up time                                                                             | 50               |       | $\dashv$ | ns         |

| t <sub>r</sub>      | SDA and SCL Rise Time                                                                        |                  |       | 120      | ns         |

| t <sub>f</sub>      | SDA and SCL Fall Time                                                                        |                  |       | 120      | ns         |

| t <sub>su;sto</sub> | Set-up time for STOP condition                                                               |                  |       |          | μ <b>s</b> |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                             | 0.5              |       | +        | μ <b>s</b> |

Submit Document Feedback

Copyright © 2021 Texas Instruments Incorporated

$T_A$  = 25 °C, VDD = 1.8 V (unless otherwise noted)

|                |                                   | MIN | NOM | MAX | UNIT |

|----------------|-----------------------------------|-----|-----|-----|------|

| C <sub>b</sub> | Capacitive load for each bus line |     |     | 200 | pF   |

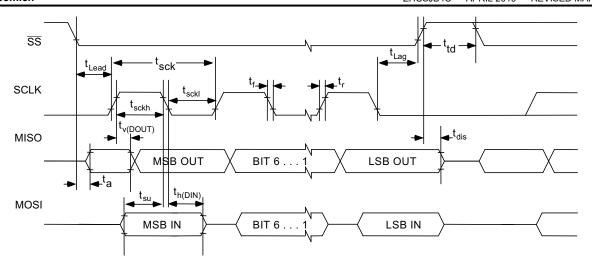

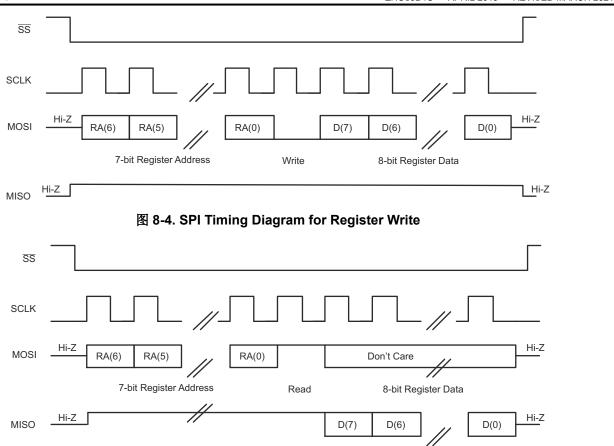

# **6.7 SPI Timing Requirements**

For SPI interface signals over recommended operating conditions (unless otherwise noted). **Note:** All timing specifications are specified by design but not tested at final test.

| SYMBOL                | PARAMETER                              | CONDITIONS | IOVDD = 1.8<br>V |     | IOVDD = 3.3<br>V |     | UNIT |

|-----------------------|----------------------------------------|------------|------------------|-----|------------------|-----|------|

|                       |                                        |            | MIN              | MAX | MIN              | MAX |      |

| t <sub>sck</sub>      | SCLK Period                            |            | 60               |     | 50               |     | ns   |

| t <sub>sckh</sub>     | SCLK Pulse width High                  |            | 30               |     | 25               |     | ns   |

| t <sub>sckl</sub>     | SCLK Pulse width Low                   |            | 30               |     | 25               |     | ns   |

| t <sub>lead</sub>     | Enable Lead Time                       |            | 60               |     | 50               |     | ns   |

| t <sub>trail</sub>    | Enable Trail Time                      |            | 60               |     | 50               |     | ns   |

| t <sub>d;seqxfr</sub> | Sequential Transfer Delay              |            | 60               |     | 50               |     | ns   |

| t <sub>a</sub>        | Slave DOUT access time                 |            |                  | 35  |                  | 25  | ns   |

| t <sub>dis</sub>      | Slave DOUT disable time                |            |                  | 35  |                  | 25  | ns   |

| t <sub>su</sub>       | DIN data setup time                    |            | 8                |     | 8                |     | ns   |

| t <sub>h;DIN</sub>    | DIN data hold time                     |            | 8                |     | 8                |     | ns   |

| t <sub>v;DOUT</sub>   | DOUT data valid time                   |            |                  | 35  |                  | 25  | ns   |

| t <sub>r</sub>        | SCLK Rise Time                         |            |                  | 4   |                  | 4   | ns   |

| t <sub>f</sub>        | SCLK Fall Time                         |            |                  | 4   |                  | 4   | ns   |

| Pd-spi                | External Pullup on SPII2CSELZ_MISO_PAD |            | 18               |     | 18               |     | kΩ   |

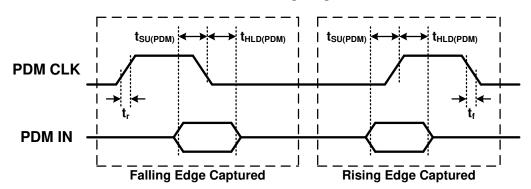

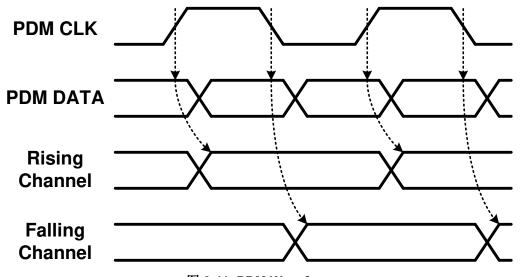

## **6.8 PDM Port Timing Requirements**

T<sub>A</sub> = 25 °C, AVDD = IOVDD = 1.8 V, 20 pF load on all outputs (unless otherwise noted)

|                        |                   |                       | MIN | NOM | MAX | UNIT |

|------------------------|-------------------|-----------------------|-----|-----|-----|------|

| t <sub>SU</sub> (PDM)  | PDM IN setup time |                       | 20  |     |     | ns   |

| t <sub>HLD</sub> (PDM) | PDM IN hold time  |                       | 3   |     |     | ns   |

| t <sub>r</sub> (PDM)   | PDM IN rise time  | 10 % - 90 % Rise Time |     |     | 4   | ns   |

| t <sub>f</sub> (PDM)   | PDM IN fall time  | 90 % - 10 % Fall Time |     |     | 4   | ns   |

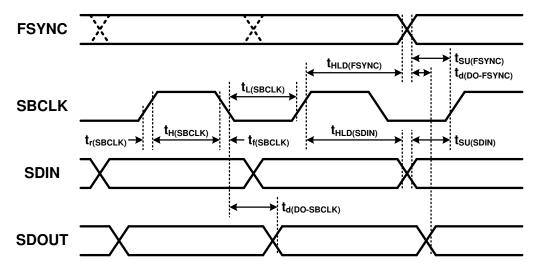

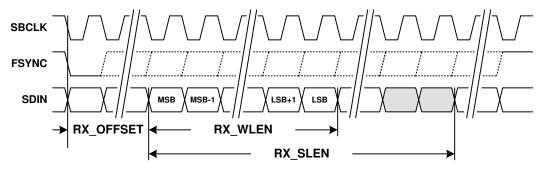

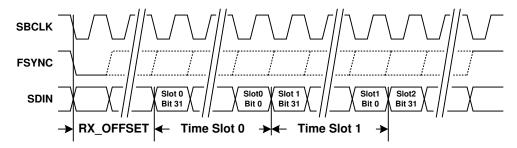

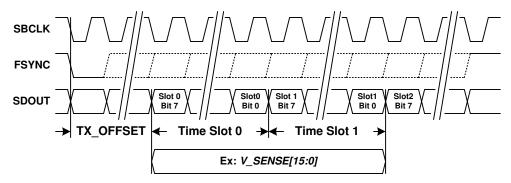

## **6.9 TDM Port Timing Requirements**

$T_A$  = 25 °C, VDD = 1.8 V, 20 pF load on all outputs (unless otherwise noted)

|                               |                      |                              | MIN | NOM | MAX | UNIT |

|-------------------------------|----------------------|------------------------------|-----|-----|-----|------|

| t <sub>H</sub> (SBCLK)        | SBCLK high period    |                              | 20  |     |     | ns   |

| t <sub>L</sub> (SBCLK)        | SBCLK low period     |                              | 20  |     |     | ns   |

| t <sub>SU</sub> (FSYNC)       | FSYNC setup time     |                              | 6.5 |     |     | ns   |

| t <sub>HLD</sub> (FSYNC)      | FSYNC hold time      |                              | 6.5 |     |     | ns   |

| t <sub>SU</sub> (FSYNC)       | SDIN setup time      |                              | 6.5 |     |     | ns   |

| t <sub>HLD</sub> (SDIN)       | SDIN hold time       |                              | 6.5 |     |     | ns   |

| t <sub>d</sub> (DO-<br>SBCLK) | SBCLK to SDOUT delay | 50% of SBCLK to 50% of SDOUT |     |     | 29  | ns   |

| t <sub>r</sub> (SBCLK)        | SBCLK rise time      | 10% - 90 % Rise Time         |     |     | 8   | ns   |

| t <sub>f</sub> (SBCLK)        | SBCLK fall time      | 90% - 10 % Fall Time         |     |     | 8   | ns   |

Copyright © 2021 Texas Instruments Incorporated

Submit Document Feedback

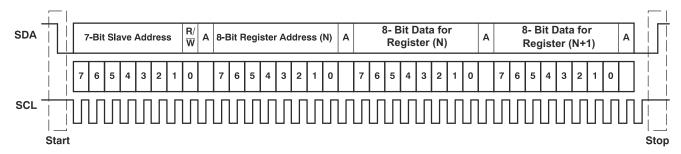

## 6.10 Timing Diagrams

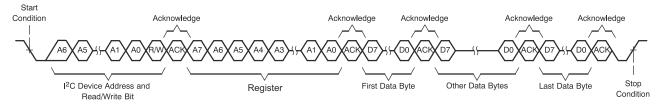

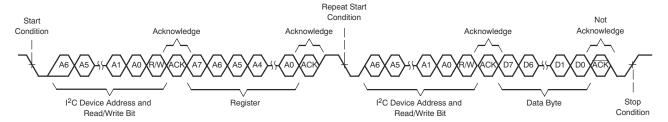

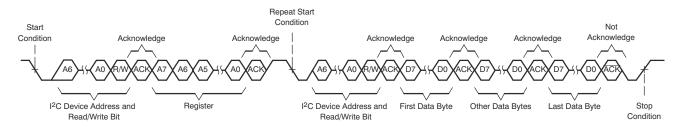

图 6-1. I<sup>2</sup>C Timing Diagram

图 6-2. TDM Timing Diagram

图 6-3. PDM Timing Diagram

图 6-4. SPI Interface Timing Diagram

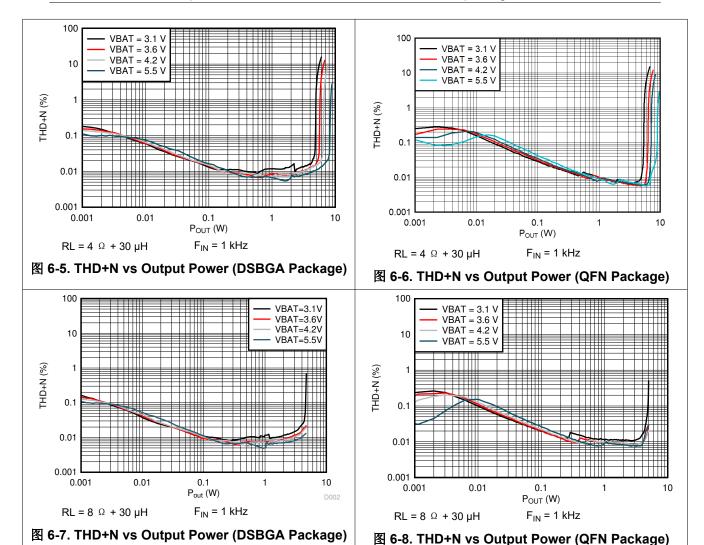

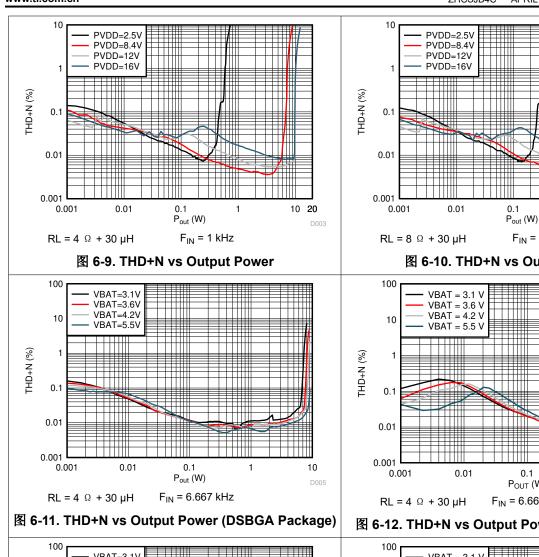

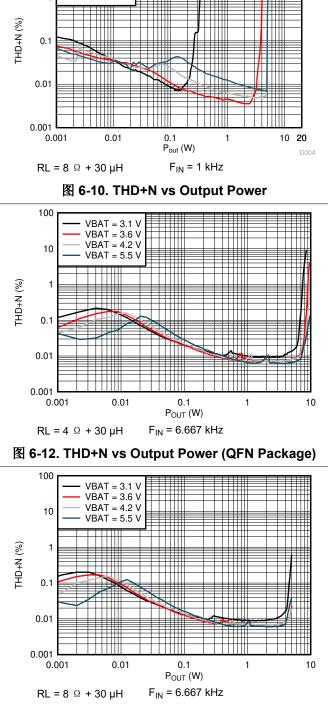

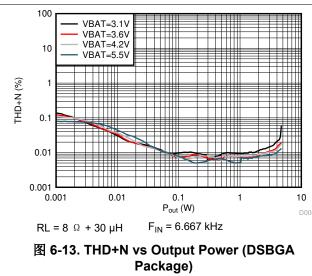

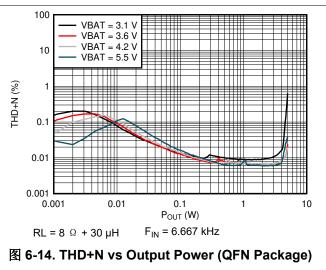

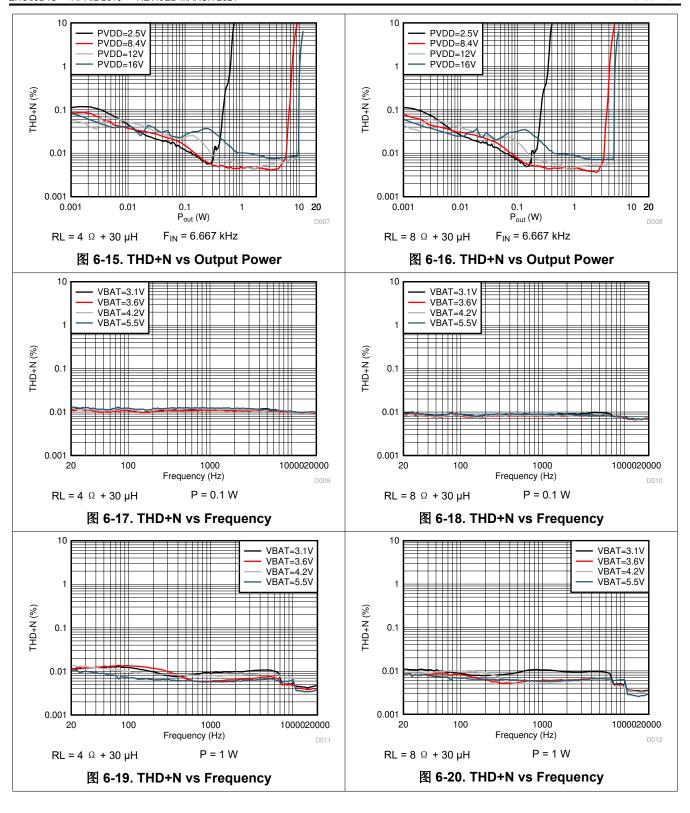

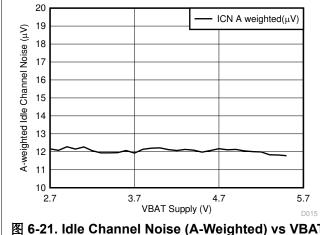

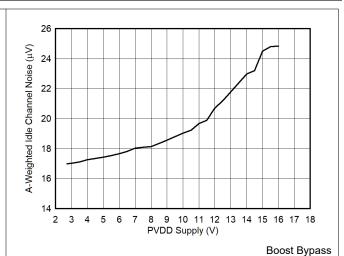

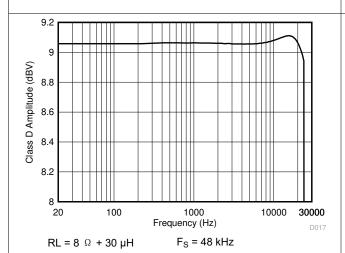

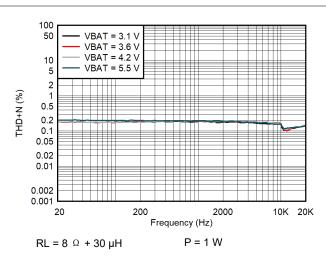

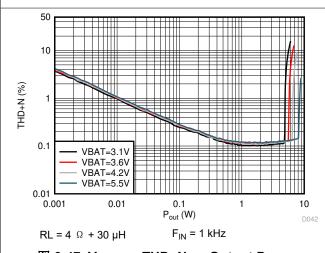

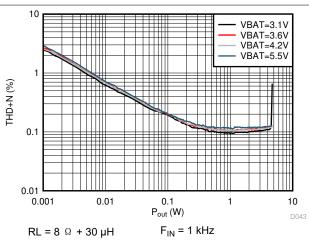

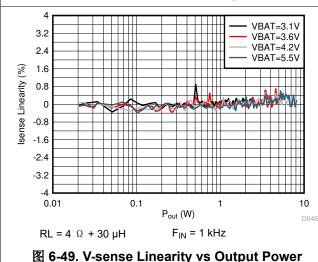

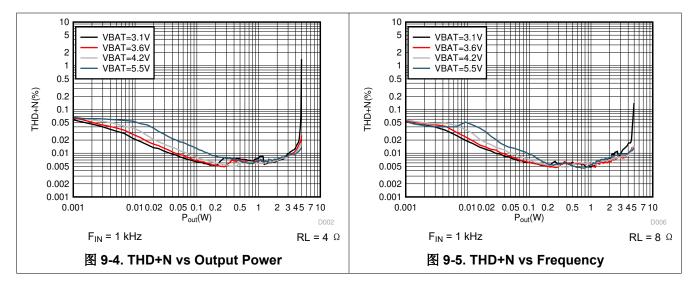

## **6.11 Typical Characteristics**

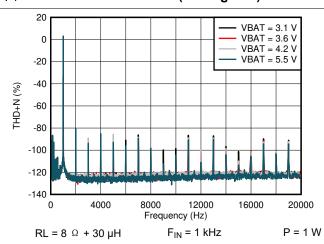

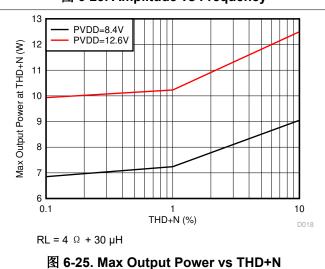

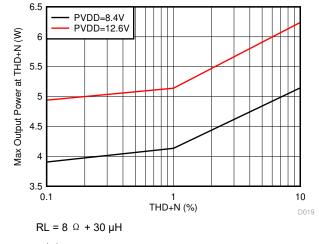

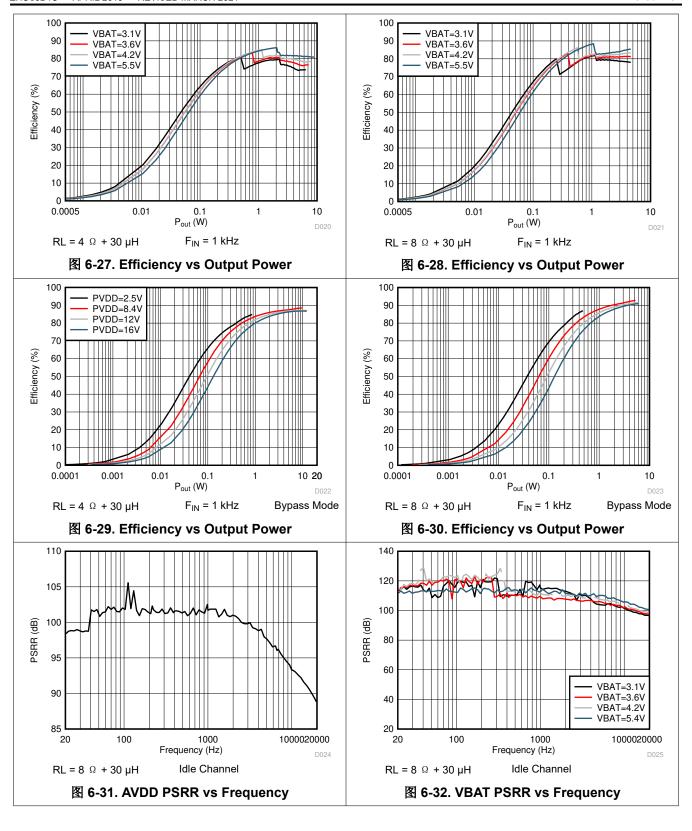

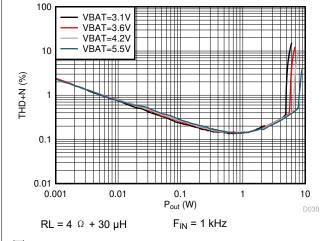

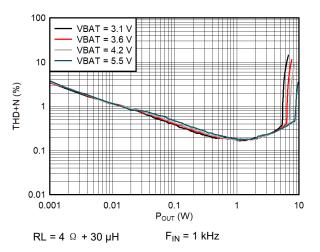

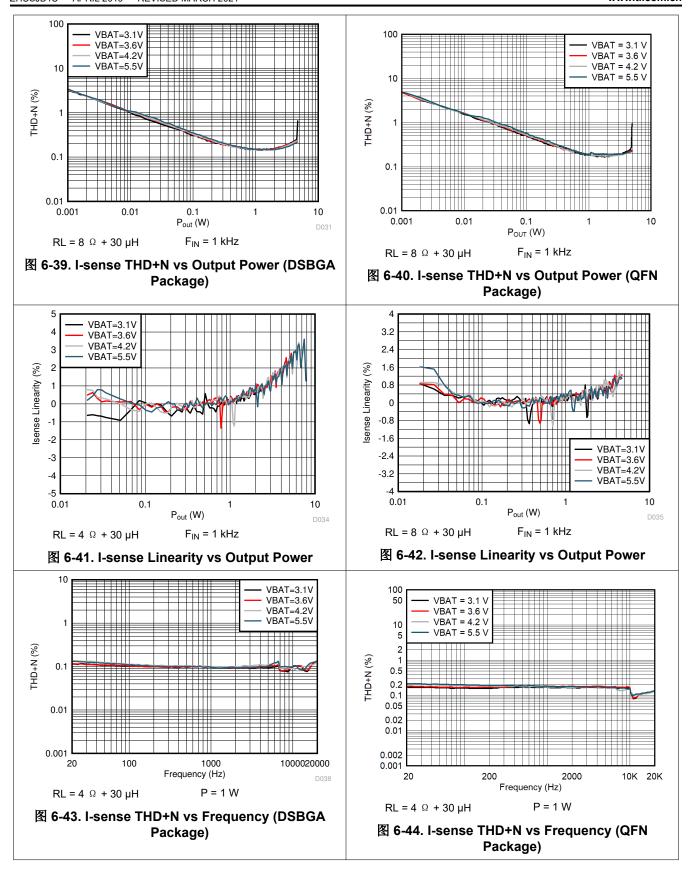

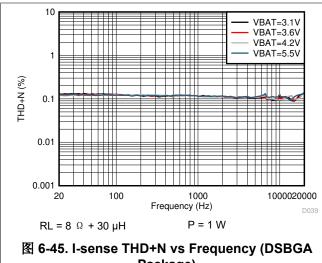

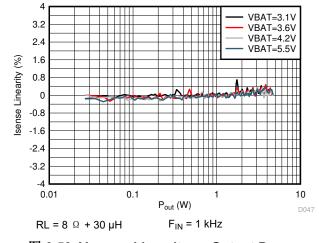

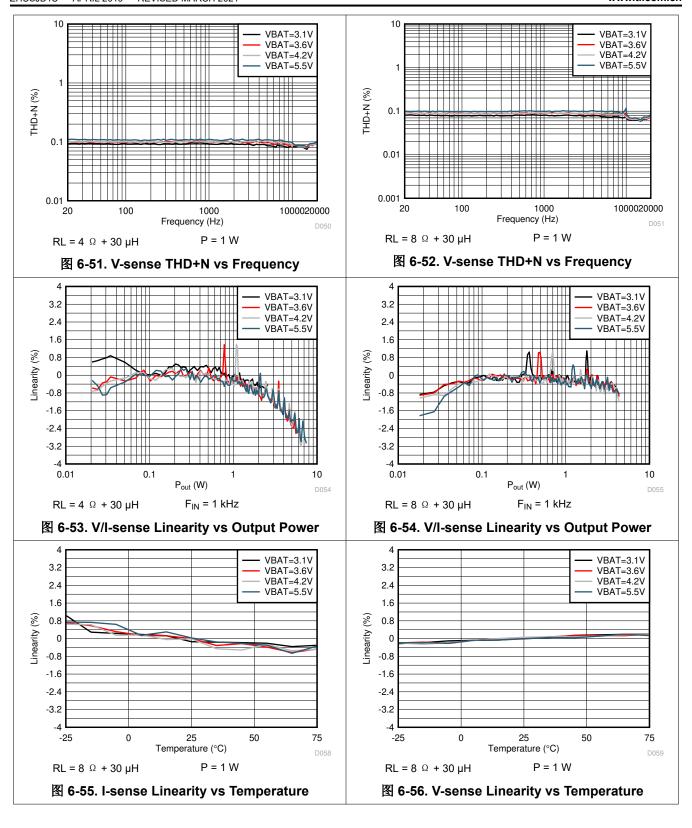

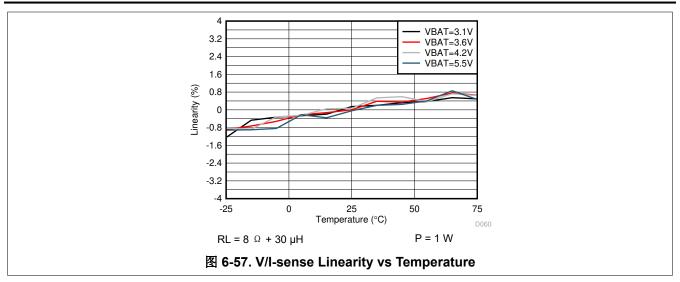

At  $T_A$  = 25°C,  $f_{SPK\_AMP}$  = 384 kHz, input signal is 1 kHz Sine, unless otherwise noted. Filter used for Load Resistance is 30  $\mu$ H, unless otherwise noted.

#### Note

All the characteristics specified for PVDD = 16 V reffer to the DSBGA package.

图 6-21. Idle Channel Noise (A-Weighted) vs VBAT

图 6-22. Idle Channel Noise (A-Weighted) vs PVDD

图 6-23. Amplitude vs Frequency

图 6-24. FFT Signal Plot

图 6-26. Max Output Power vs THD+N

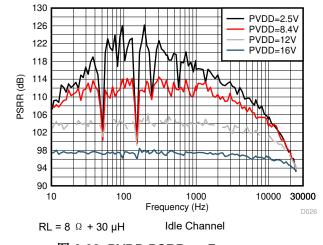

图 6-33. PVDD PSRR vs Frequency

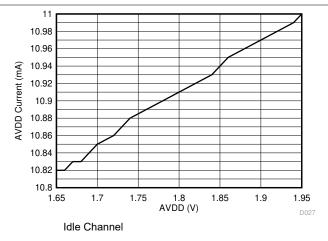

图 6-34. AVDD Idle Current vs AVDD (DSBGA Package)

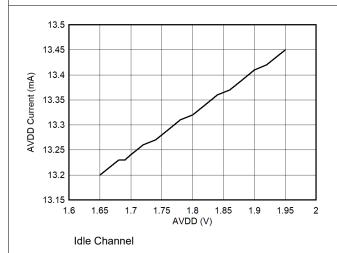

图 6-35. AVDD Idle Current vs AVDD (QFN Package)

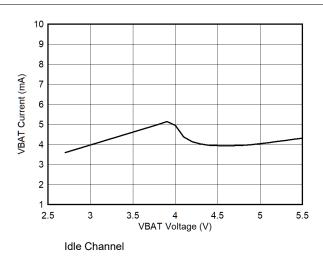

图 6-36. VBAT Idle Current vs VBAT

图 6-37. I-sense THD+N vs Output Power (DSBGA Package)

图 6-38. I-sense THD+N vs Output Power (QFN Package)

Package)

图 6-46. I-sense THD+N vs Frequency (QFN Package)

图 6-47. V-sense THD+N vs Output Power

图 6-48. V-sense THD+N vs Output Power

图 6-50. V-sense Linearity vs Output Power

### 7 Parameter Measurement Information

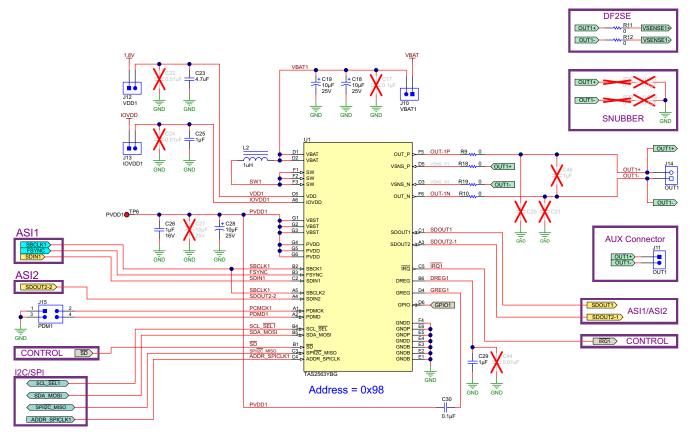

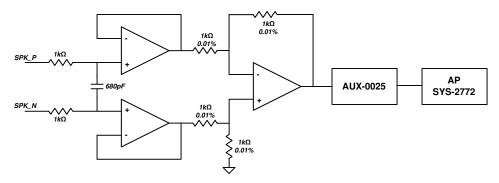

图 7-1. TAS2563 Circuit

All typical characteristics for the devices are measured using the Bench EVM and an Audio Precision SYS-2722 Audio Analyzer. A PSIA interface is used to allow the I<sup>2</sup>S interface to be driven directly into the SYS-2722. Speaker output terminals are connected to the Audio-Precision analyzer analog inputs through a differential-to-single ended (D2S) filter as shown below. The D2S filter contains a 1st order Passive pole at 120 kHz. The D2S filter ensures the TAS2563 high performance class-D amplifier sees a fully differential matched loading at its outputs. This prevents measurement errors due to loading effects of AUX-0025 filter on the class-D outputs.

图 7-2. Differential To Single Ended (D2S) Filter

## **8 Detailed Description**

## 8.1 Overview

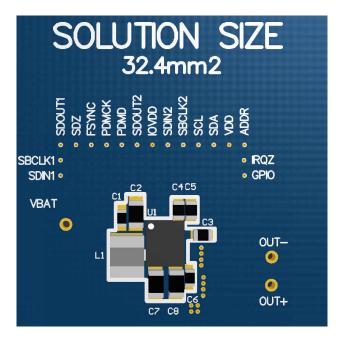

The TAS2563 is a mono digital input Class-D amplifier optimized for mobile applications where efficient battery operation and small solution size are crucial. It integrates speaker voltage and current sensing and battery tracking limiting with brown out prevention.

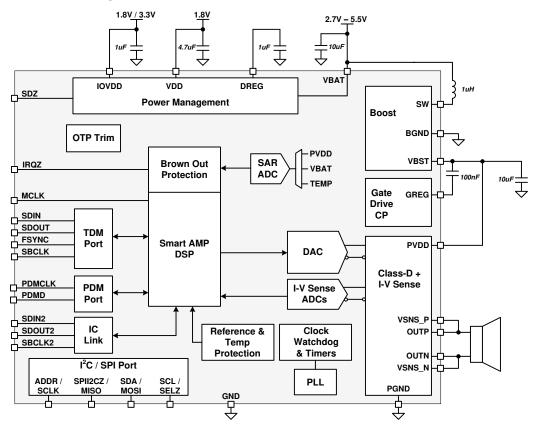

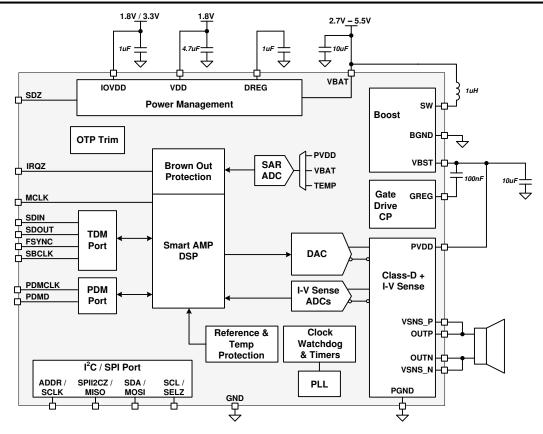

## 8.2 Functional Block Diagram

图 8-1. Functional Block Diagram

图 8-2. TAS2563 QFN Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 PurePath™ Console 3 Software