## 带集成式合成器的 LMX8410L 高性能混合器

### 1 特性

- 宽带射频输入: 4 至 10GHz

- 大型中频带宽: 直流至 1350MHz

- 输入 IP3: 5GHz 射频输入时为 28dBm

- 噪声系数: 5GHz 射频输入时为 15dB

- 高电压转换增益: 5GHz 射频输入时为 11dB

- 集成宽带射频输入平衡-非平衡变压器

- 自动离线直流失调电压校正为  $\pm 2\text{mV}$

- 可编程 IMRR 校准

- 针对多个器件的同步功能

- 高性能集成 LO 合成器: 5GHz 载波条件下具有 56.5dBc 的 DSB 集成噪声

- 外部 LO 模式: 可旁路绕开集成 LO 合成器; 支持外部 LO 注入

- 集成低噪声 LDO

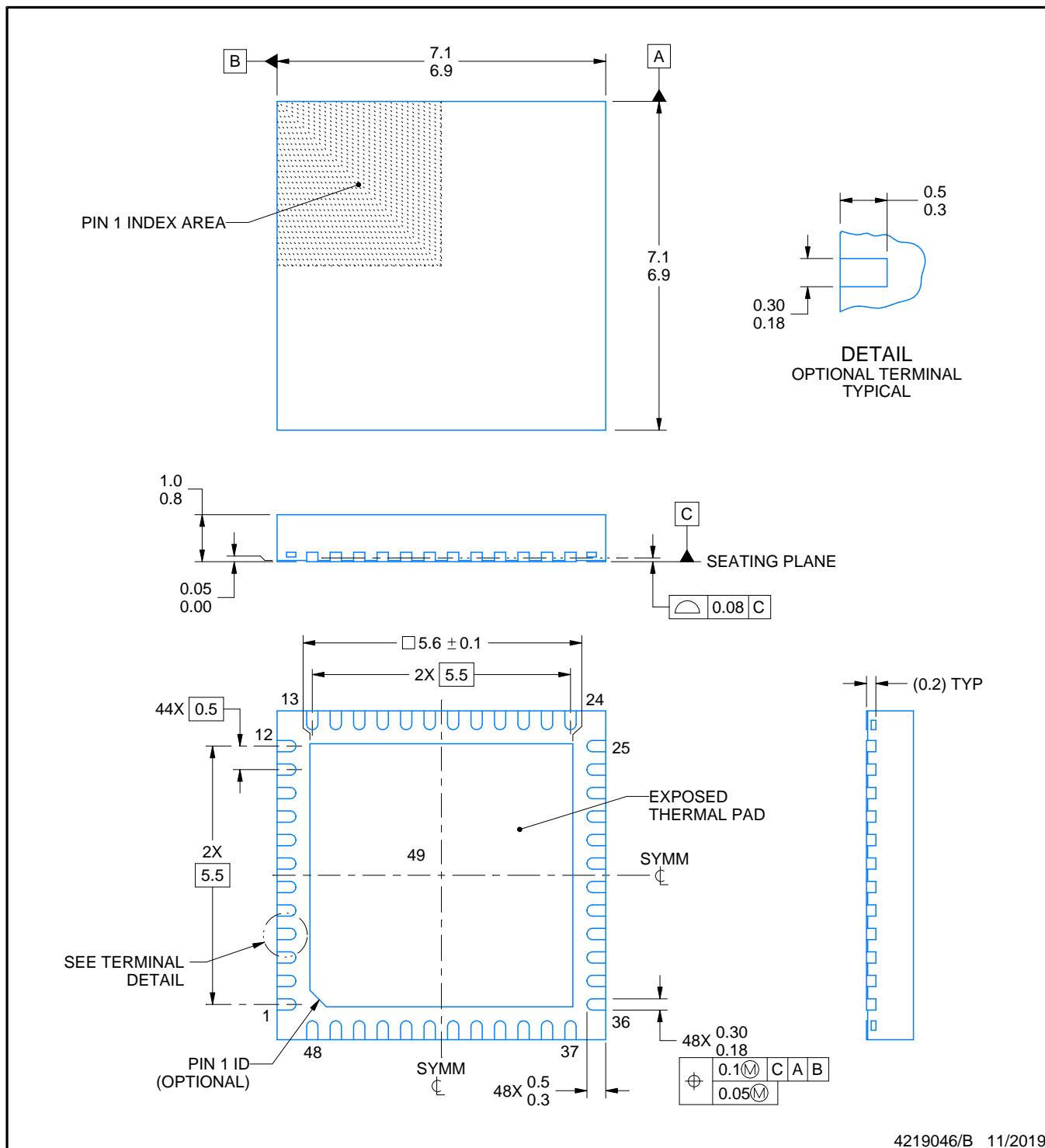

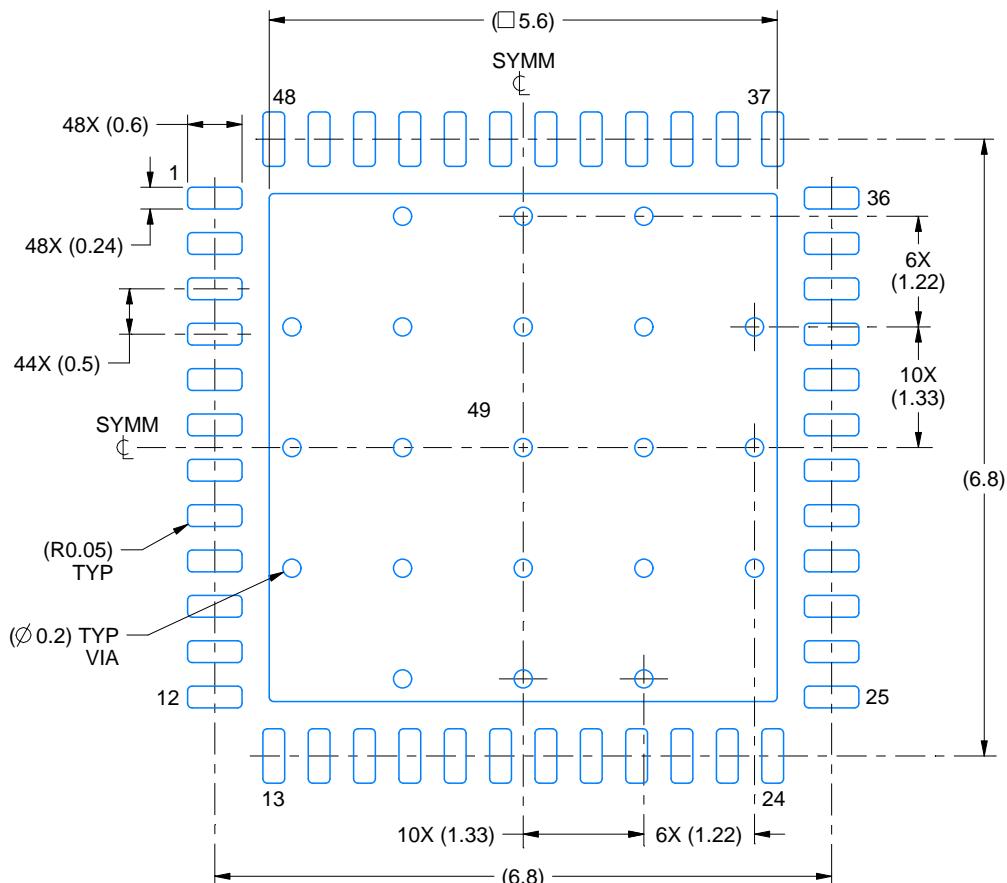

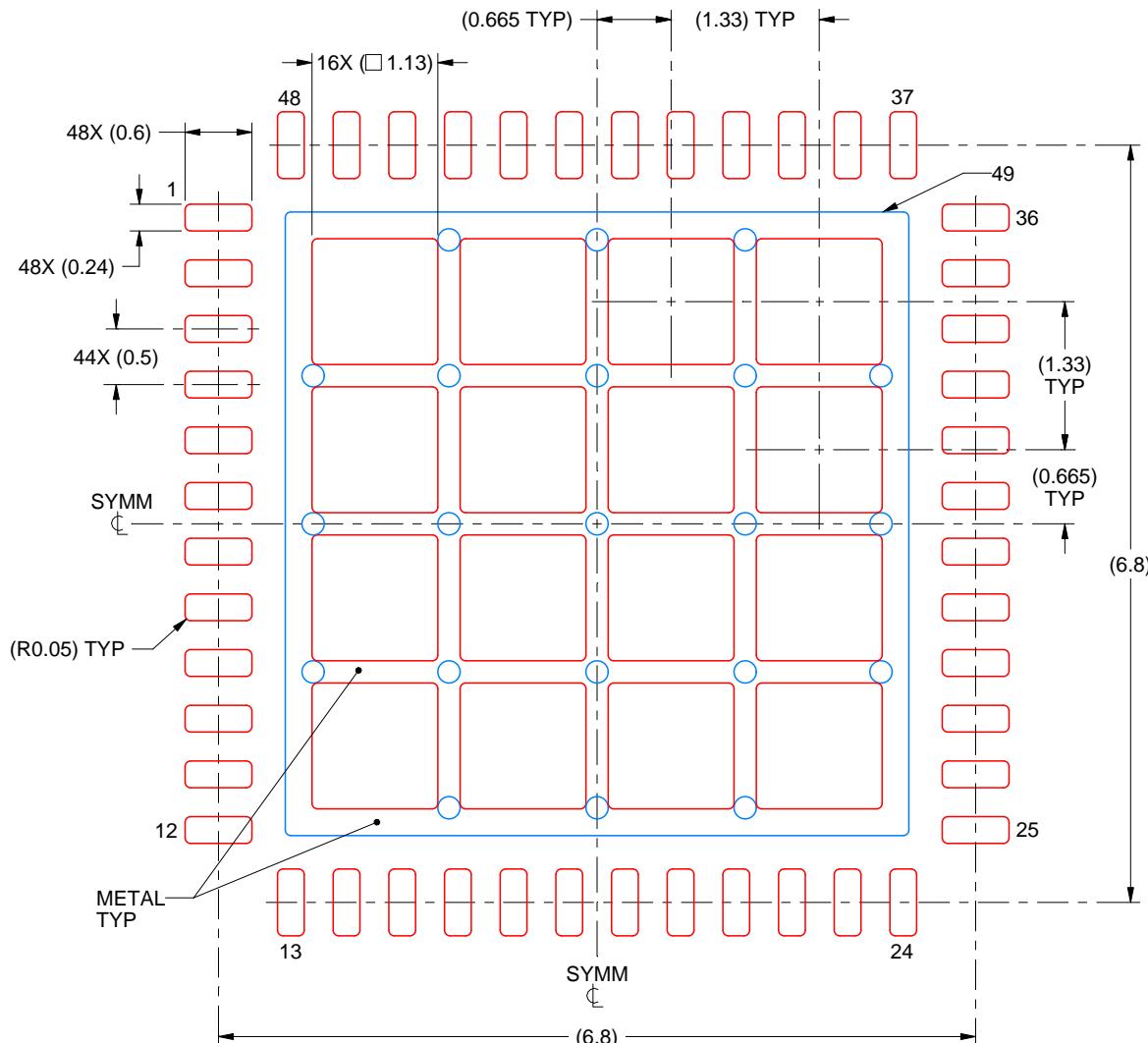

- 7mm x 7mm 48 引脚 QFN 封装

### 2 应用

- 测试和测量设备

- 无线基础设施

- 相控阵雷达

- 微波回程

- 卫星通信

- 软件定义无线电

### 3 说明

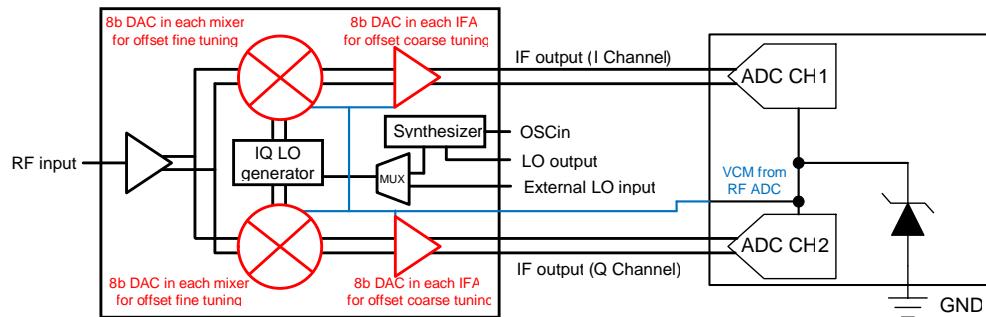

LMX8410L 是一款具有集成 LO 和 IF 放大器的高性能宽带（射频输入为 4 至 10GHz）I/Q 解调器。在 IIP3 为 28dBm 而 NF 为 15dB（频率均为 5GHz）的情况下，该器件可提供出色的动态范围，适用于高性能应用中使用 DP83869。该器件可提供 2.7GHz 的大型复杂带宽，适用于高数据速率应用。

LMX8410L 提供自动直流失调电压校正算法，可将失调电压降至  $\pm 2\text{mV}$  以下。使用 SPI 接口可以精确控制 I 和 Q 通道的增益和相位，从而实现高镜像抑制。

LMX8410L 具有高度集成度，可提供高性能，同时还能节省布板空间并降低复杂性。它集成了宽带射频输入平衡-非平衡变压器，因此无需外部平衡-非平衡变压器。它集成了高性能 PLL 和 VCO，因此无需外部 LO 和 LO 驱动器。该器件还集成了一个 IF 放大器和几个低噪声 LDO，进一步简化了电路板。

LMX8410L 集成了一个极低噪声的合成器，PLL FOM 为  $-236\text{dBc/Hz}$ ，在 5GHz 载波条件下提供高达 56.5dBc 的 DSB 集成噪声。LO 允许跨多个器件进行相位同步。高性能合成器输出可用于驱动另一级或数据转换器。对于共享外部 LO 的应用，可以旁路掉集成的 LO。

#### 器件信息<sup>(1)</sup>

| 器件型号     | 封装        | 封装尺寸（标称值）       |

|----------|-----------|-----------------|

| LMX8410L | VQFN (48) | 7.00mm x 7.00mm |

(1) 如需了解所有可用封装，请参阅产品说明书末尾的可订购产品附录。

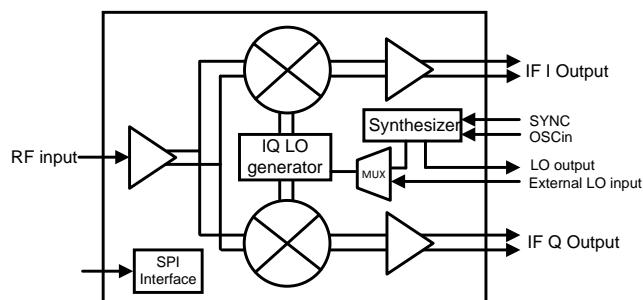

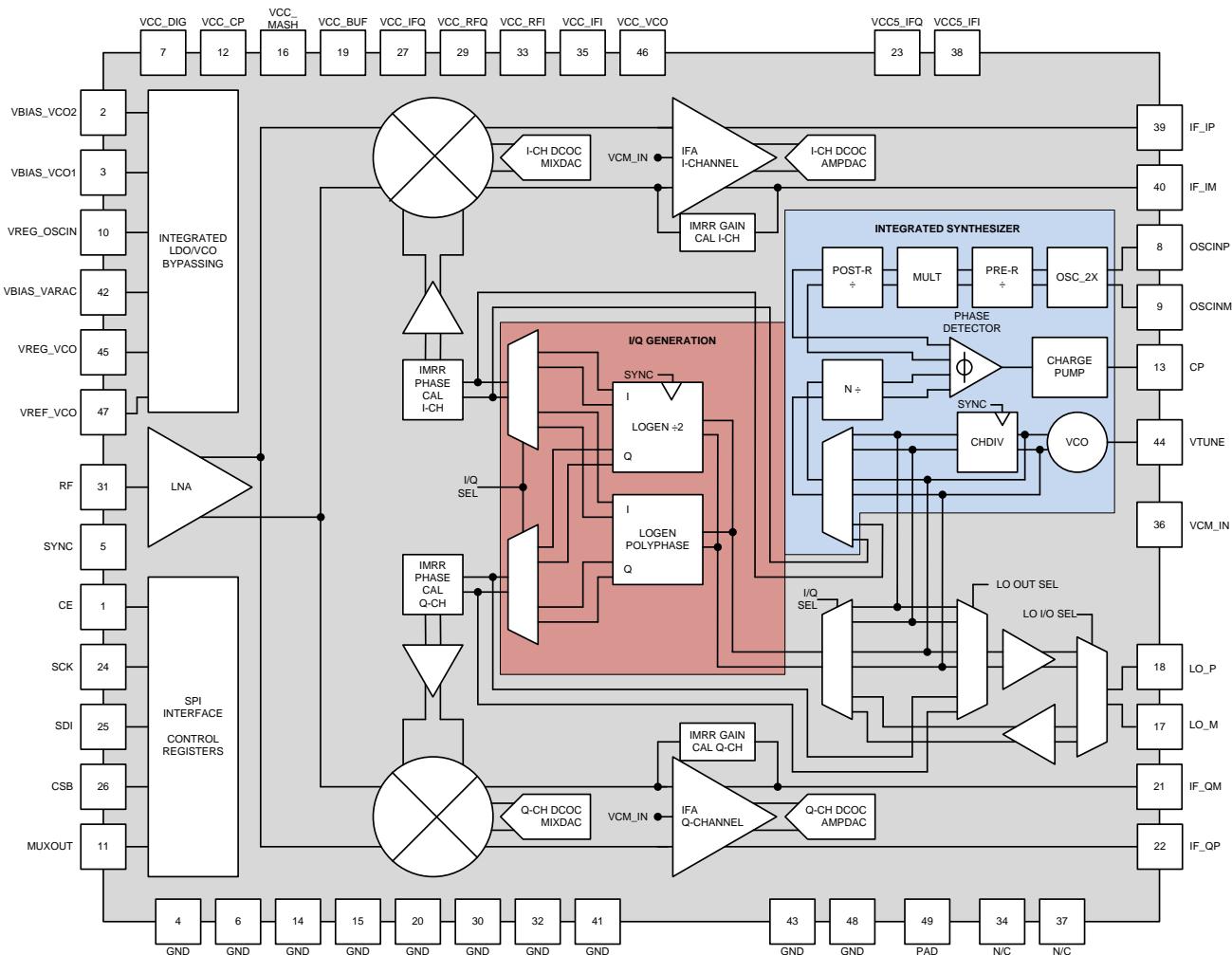

#### 简化方框图

## 目录

|     |                                        |    |      |                                       |    |

|-----|----------------------------------------|----|------|---------------------------------------|----|

| 1   | 特性                                     | 1  | 7.5  | Programming                           | 29 |

| 2   | 应用                                     | 1  | 7.6  | Register Map                          | 30 |

| 3   | 说明                                     | 1  | 8    | <b>Application and Implementation</b> | 53 |

| 4   | 修订历史记录                                 | 2  | 8.1  | Application Information               | 53 |

| 5   | <b>Pin Configuration and Functions</b> | 3  | 8.2  | Typical Application                   | 53 |

| 6   | <b>Specifications</b>                  | 6  | 9    | <b>Power Supply Recommendations</b>   | 56 |

| 6.1 | Absolute Maximum Ratings               | 6  | 10   | <b>Layout</b>                         | 56 |

| 6.2 | ESD Ratings                            | 6  | 10.1 | Layout Guidelines                     | 56 |

| 6.3 | Recommended Operating Conditions       | 6  | 10.2 | Layout Examples                       | 57 |

| 6.4 | Thermal Information                    | 6  | 11   | 器件和文档支持                               | 61 |

| 6.5 | Electrical Characteristics             | 7  | 11.1 | 文档支持                                  | 61 |

| 6.6 | Timing Requirements                    | 12 | 11.2 | 接收文档更新通知                              | 61 |

| 6.7 | Typical Characteristics                | 14 | 11.3 | 社区资源                                  | 61 |

| 7   | <b>Detailed Description</b>            | 22 | 11.4 | 商标                                    | 61 |

| 7.1 | Overview                               | 22 | 11.5 | 静电放电警告                                | 61 |

| 7.2 | Functional Block Diagram               | 22 | 11.6 | 术语表                                   | 61 |

| 7.3 | Feature Description                    | 23 | 12   | 机械、封装和可订购信息                           | 61 |

| 7.4 | Device Functional Modes                | 28 |      |                                       |    |

## 4 修订历史记录

注：之前版本的页码可能与当前版本有所不同。

| Changes from Original (March 2018) to Revision A                                                                                    | Page |

|-------------------------------------------------------------------------------------------------------------------------------------|------|

| • 首次发布生产数据产品说明书                                                                                                                     | 1    |

| • Changed many numbers in electrical specifications table                                                                           | 6    |

| • 已添加 typical performance characteristics section                                                                                   | 14   |

| • 已更改 and added significant details in detailed descriptions sections. Added sections, changed several portions of the register map | 22   |

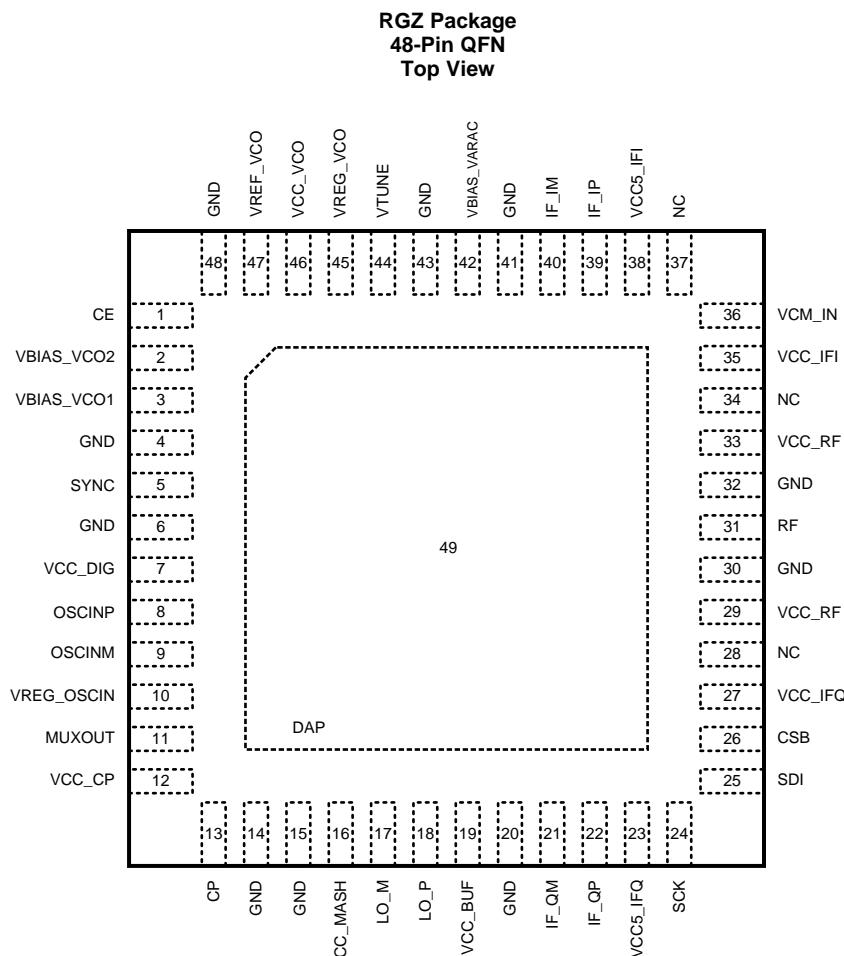

## 5 Pin Configuration and Functions

### Pin Functions

| PIN  |            | I/O    | DESCRIPTION                                                                                                                                                                                                  |

|------|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NAME       |        |                                                                                                                                                                                                              |

| 1    | CE         | Input  | Chip Enable input. Active HIGH powers on the device. 1.8V to 3.3V logic.                                                                                                                                     |

| 2    | VBIAS_VCO2 | Bypass | VCO bias. Requires connecting 10- $\mu$ F capacitor to VCO ground. Place close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode.               |

| 3    | VBIAS_VCO1 | Bypass | VCO bias. Requires connecting 10- $\mu$ F capacitor to VCO ground. Place close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode.               |

| 4    | GND        | Ground | VCO ground. VBIAS pin capacitors must bypass to this point.                                                                                                                                                  |

| 5    | SYNC       | Input  | Trigger pin for synchronizing multiple devices. If using external LO, tie this pin to GND.                                                                                                                   |

| 6    | GND        | Ground | Digital ground. VCC_DIG bypass capacitors must bypass to this point.                                                                                                                                         |

| 7    | VCC_DIG    | Supply | Digital supply. TI recommends connecting 0.1- $\mu$ F capacitor to digital ground.                                                                                                                           |

| 8    | OSCINP     | Input  | Reference input clock (+). High input impedance. Requires connecting series capacitor (0.1 $\mu$ F recommended). If using external LO, tie this pin to GND.                                                  |

| 9    | OSCINM     | Input  | Reference input clock (-). High input impedance. Requires connecting series capacitor (0.1 $\mu$ F recommended). If using external LO, tie this pin to GND.                                                  |

| 10   | VREG_OSCIN | Bypass | Internal LDO output. Requires connecting 1- $\mu$ F capacitor to digital ground. Place close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode. |

## Pin Functions (continued)

| PIN  |             | I/O          | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|------|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NAME        |              |                                                                                                                                                                                                                                                                                                                                                                                                 |

| 11   | MUXOUT      | Output       | Readback or lock detect output. Pin mode configured by internal register settings.                                                                                                                                                                                                                                                                                                              |

| 12   | VCC_CP      | Supply       | Charge pump supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to charge pump ground. Place close to pin. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                                    |

| 13   | CP          | Output       | Charge pump output. TI recommends connecting C1 of loop filter close to pin. If using external LO, this pin should either be floated or configured the same way as internal LO mode.                                                                                                                                                                                                            |

| 14   | GND         | Ground       | Charge pump ground. VCC_CP bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                                                         |

| 15   | GND         | Ground       | MASH engine ground. VCC_MASH bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                                                       |

| 16   | VCC_MASH    | Supply       | MASH engine supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to MASH engine ground. Place close to pin. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                                    |

| 17   | LO_M        | Input/Output | Internal LO differential output (–) or external LO differential input (–). In differential output mode, requires connecting 50- $\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin. In differential input mode, remove the pull up resistors or inductors. The input should be capacitively coupled with internal biasing. See <a href="#">LO Interface</a> for more information. |

| 18   | LO_P        | Input/Output | Internal LO differential output (+) or external LO differential input (+). In differential output mode, requires connecting 50- $\Omega$ resistor pullup to $V_{CC}$ as close as possible to pin. In differential input mode, remove the pull up resistors or inductors. The input should be capacitively coupled with internal biasing. See <a href="#">LO Interface</a> for more information. |

| 19   | VCC_BUF     | Supply       | LO buffer supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to VCO ground. This pin must be connected to VCC, even if using external LO.                                                                                                                                                                                                                                                  |

| 20   | GND         | Ground       | IF amplifier Q-channel ground. Q-channel VCC5 bypass capacitors must bypass to this point.                                                                                                                                                                                                                                                                                                      |

| 21   | IF_QM       | Output       | IF amplifier Q-channel differential output (–). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                             |

| 22   | IF_QP       | Output       | IF amplifier Q-channel differential output (+). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                             |

| 23   | VCC5_IFQ    | Supply       | IF amplifier Q-channel 5-V supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to IF amplifier Q-channel ground. Place close to pin.                                                                                                                                                                                                                                                        |

| 24   | SCK         | Input        | SPI clock signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                                              |

| 25   | SDI         | Input        | SPI data signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                                               |

| 26   | CSB         | Input        | SPI chip select signal. High impedance CMOS input. 1.8-V to 3.3-V logic.                                                                                                                                                                                                                                                                                                                        |

| 27   | VCC_IFQ     | Supply       | IF mixer Q-channel supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                   |

| 28   | NC          | N/A          | No connect. Pin is not internally connected and may be floated or shorted to other nodes.                                                                                                                                                                                                                                                                                                       |

| 29   | VCC_RFQ     | Supply       | RF Q-channel supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                         |

| 32   | GND         | Ground       | RF input path ground.                                                                                                                                                                                                                                                                                                                                                                           |

| 31   | RF          | Input        | RF input. Single-ended. Must be AC coupled.                                                                                                                                                                                                                                                                                                                                                     |

| 32   | GND         | Ground       | RF input path ground.                                                                                                                                                                                                                                                                                                                                                                           |

| 33   | VCC_RFI     | Supply       | RF I-channel supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                         |

| 34   | GND         | Ground       | Should be connected IF ground.                                                                                                                                                                                                                                                                                                                                                                  |

| 35   | VCCIFI      | Supply       | IF mixer I-channel supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to digital ground.                                                                                                                                                                                                                                                                                                   |

| 36   | VCM_IN      | Input        | Common-mode voltage input. When the VCM_CONFIG register is set to external (0xF), the voltage on this pin sets the common-mode voltage of the IF amplifiers.                                                                                                                                                                                                                                    |

| 37   | NC          | Ground       | Connect this pin to IF ground.                                                                                                                                                                                                                                                                                                                                                                  |

| 38   | VCC5IFI     | Supply       | IF amplifier I-channel 5-V supply. TI recommends connecting 0.1 $\mu$ F and 100 pF to IF amplifier I-channel ground. Place close to pin.                                                                                                                                                                                                                                                        |

| 39   | IF_IP       | Output       | IF amplifier I-channel differential output (+). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                             |

| 40   | IF_IM       | Output       | IF amplifier I-channel differential output (–). TI recommends connecting series 50- $\Omega$ resistor close to pin.                                                                                                                                                                                                                                                                             |

| 41   | GND         | Ground       | IF amplifier I-channel ground. I-channel VCC5 bypass capacitors should bypass to this point.                                                                                                                                                                                                                                                                                                    |

| 42   | VBIAS_VARAC | Bypass       | VCO varactor bias. Requires connecting 10 $\mu$ F capacitor to VCO ground. If using external LO, this pin should either be floated or configured the same way as internal LO mode.                                                                                                                                                                                                              |

| 43   | GND         | Ground       | VCO ground. Varactor bias bypass capacitor should bypass to this point.                                                                                                                                                                                                                                                                                                                         |

**Pin Functions (continued)**

| PIN  |          | I/O    | DESCRIPTION                                                                                                                                                                             |

|------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME | NAME     |        |                                                                                                                                                                                         |

| 44   | VTUNE    | Input  | VCO tuning voltage input. If using internal LO, connect the output of the loop filter to this point. If using external LO, tie this pin to GND.                                         |

| 45   | VREG_VCO | Bypass | VCO LDO output node. Requires connecting 10- $\mu$ F capacitor to VCO ground. Place close to pin. This capacitor must be present even if used in external LO mode.                      |

| 46   | VCC_VCO  | Supply | VCO supply. TI recommends connecting 0.1- $\mu$ F and 100-pF capacitors to VCO ground. This pin must be connected to VCC, even if using external LO.                                    |

| 47   | VREF_VCO | Bypass | VCO LDO reference node. Requires connecting 1- $\mu$ F capacitor to VCO ground. If using external LO, this pin should either be floated or configured the same way as internal LO mode. |

| 48   | GND      | Ground | VCO ground. VCO LDO, LDO reference, and supply bypass capacitors must bypass to this point.                                                                                             |

| 49   | PAD      | Ground | Die attach pad. Internally connected to ground. TI recommends shorting ground pins to this pad on the same plane, if possible.                                                          |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                  | MIN  | MAX | UNIT |

|------------------|----------------------------------|------|-----|------|

| V <sub>CC</sub>  | Power supply voltage, 3.3-V rail | –0.3 | 3.6 | V    |

| V <sub>CC5</sub> | Power supply voltage, 5-V rail   | –0.3 | 5.3 | V    |

| P <sub>D</sub>   | Power dissipation                |      | 5   | W    |

| T <sub>J</sub>   | Junction temperature             | –40  | 150 | °C   |

| T <sub>stg</sub> | Storage temperature              | –65  | 150 | °C   |

(1) Stresses beyond those listed under *Absolute Maximum Rating* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Condition*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         | VALUE                                                                     | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins              | 2500 |

|                    |                         | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins | 500  |

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                 | MIN  | NOM | MAX  | UNIT |

|------------------|---------------------------------|------|-----|------|------|

| V <sub>CC</sub>  | Power supply voltage, 3.3V rail | 3.15 | 3.3 | 3.45 | V    |

| V <sub>CC5</sub> | Power supply voltage, 5V rail   | 4.75 | 5   | 5.25 | V    |

| T <sub>A</sub>   | Ambient temperature             | –40  | 25  | 85   | °C   |

| T <sub>J</sub>   | Junction temperature            |      |     | 125  | °C   |

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1) (2)</sup> |                                              | LMX8410L   | UNIT |

|-----------------------------------|----------------------------------------------|------------|------|

|                                   |                                              | RGZ (VQFN) |      |

|                                   |                                              | 48 PINS    |      |

| R <sub>θJA</sub>                  | Junction-to-ambient thermal resistance       | 21.9       | °C/W |

| R <sub>θJC(top)</sub>             | Junction-to-case (top) thermal resistance    | 9.4        | °C/W |

| R <sub>θJB</sub>                  | Junction-to-board thermal resistance         | 5.6        | °C/W |

| Ψ <sub>JT</sub>                   | Junction-to-top characterization parameter   | 0.1        | °C/W |

| Ψ <sub>JB</sub>                   | Junction-to-board characterization parameter | 5.6        | °C/W |

| R <sub>θJC(bot)</sub>             | Junction-to-case (bottom) thermal resistance | 0.4        | °C/W |

(1) For more information about traditional and new thermal metrics, see the [Semiconductor and IC Package Thermal Metrics](#) application report.

(2) Thermal model based on JEDEC standard coupon, 50.8 mm × 50.8 mm × 1.6 mm, six-layer Cu, 0.5 oz top layer, 2 oz else. 6 × 6 thermal vias in DAP, 0.2 mm diameter.

## 6.5 Electrical Characteristics

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER                  |                                                      | TEST CONDITIONS | MIN  | TYP   | MAX  | UNIT |

|----------------------------|------------------------------------------------------|-----------------|------|-------|------|------|

| <b>POWER SUPPLY</b>        |                                                      |                 |      |       |      |      |

| $V_{CC}$                   | Power supply voltage, 3.3-V rail                     |                 | 3.15 | 3.3   | 3.45 | V    |

| $I_{CC}$                   | Power supply current, 3.3-V rail                     | Internal LO     |      | 650   |      | mA   |

|                            |                                                      | External LO     |      | 330   |      |      |

| $V_{CC5}$                  | Power supply voltage, 5-V rail                       |                 | 4.75 | 5     | 5.25 | V    |

| $I_{CC5}$                  | Power supply current both channels I and Q, 5-V rail |                 |      | 130   |      | mA   |

| <b>FREQUENCY RANGES</b>    |                                                      |                 |      |       |      |      |

| $F_{RF}$                   | RF port frequency range                              |                 | 4000 | 10000 |      | MHz  |

| $F_{LO}$                   | LO port frequency range                              |                 | 4000 | 10000 |      | MHz  |

| $F_{IF}$                   | IF port frequency range (3dB bandwidth)              |                 | DC   | 1350  |      | MHz  |

| <b>DYNAMIC PERFORMANCE</b> |                                                      |                 |      |       |      |      |

| NF                         | Noise figure                                         | RF = 4 GHz      |      | 15    |      | dB   |

|                            |                                                      | RF = 5 GHz      |      | 15    |      |      |

|                            |                                                      | RF = 6 GHz      |      | 16    |      |      |

|                            |                                                      | RF = 7 GHz      |      | 17    |      |      |

|                            |                                                      | RF = 8 GHz      |      | 18    |      |      |

|                            |                                                      | RF = 9 GHz      |      | 19    |      |      |

|                            |                                                      | RF = 10 GHz     |      | 19    |      |      |

| G                          | Voltage gain <sup>(1)</sup>                          | RF = 4 GHz      |      | 11    |      | dB   |

|                            |                                                      | RF = 5 GHz      |      | 11    |      |      |

|                            |                                                      | RF = 6 GHz      |      | 10.5  |      |      |

|                            |                                                      | RF = 7 GHz      |      | 9.5   |      |      |

|                            |                                                      | RF = 8 GHz      |      | 9     |      |      |

|                            |                                                      | RF = 9 GHz      |      | 8     |      |      |

|                            |                                                      | RF = 10 GHz     |      | 7     |      |      |

| IIP3                       | Input intercept point, 3rd order <sup>(2)</sup>      | RF = 4 GHz      |      | 28    |      | dBm  |

|                            |                                                      | RF = 5 GHz      |      | 28    |      |      |

|                            |                                                      | RF = 6 GHz      |      | 26.5  |      |      |

|                            |                                                      | RF = 7 GHz      |      | 27    |      |      |

|                            |                                                      | RF = 8 GHz      |      | 26.5  |      |      |

|                            |                                                      | RF = 9 GHz      |      | 27    |      |      |

|                            |                                                      | RF = 10 GHz     |      | 27    |      |      |

| IIP2                       | Input intercept point, 2nd order (uncalibrated)      | RF = 4 GHz      |      | 48    |      | dBm  |

|                            |                                                      | RF = 5 GHz      |      | 48    |      |      |

|                            |                                                      | RF = 6 GHz      |      | 46    |      |      |

|                            |                                                      | RF = 7 GHz      |      | 44    |      |      |

|                            |                                                      | RF = 8 GHz      |      | 45    |      |      |

|                            |                                                      | RF = 9 GHz      |      | 44    |      |      |

|                            |                                                      | RF = 10 GHz     |      | 42    |      |      |

(1) For measurements that require RF input, RF input power is -10dBm unless otherwise specified.

(2) For two-tone measurements, tone separation is 17MHz.

## Electrical Characteristics (continued)

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER             |                                      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------------|--------------------------------------|-----------------|-----|-----|-----|------|

| SP <sub>2x2</sub>     | 2x2 spur [RF input power at -10 dBm] | RF = 4 GHz      |     | -58 |     | dBc  |

|                       |                                      | RF = 5 GHz      |     | -58 |     |      |

|                       |                                      | RF = 6 GHz      |     | -58 |     |      |

|                       |                                      | RF = 7 GHz      |     | -54 |     |      |

|                       |                                      | RF = 8 GHz      |     | -52 |     |      |

|                       |                                      | RF = 9 GHz      |     | -50 |     |      |

|                       |                                      | RF = 10 GHz     |     | -48 |     |      |

| SP <sub>3x3</sub>     | 3x3 spur [RF input power at -10 dBm] | RF = 4 GHz      |     | -75 |     | dBc  |

|                       |                                      | RF = 5 GHz      |     | -75 |     |      |

|                       |                                      | RF = 6 GHz      |     | -75 |     |      |

|                       |                                      | RF = 7 GHz      |     | -75 |     |      |

|                       |                                      | RF = 8 GHz      |     | -75 |     |      |

|                       |                                      | RF = 9 GHz      |     | -75 |     |      |

|                       |                                      | RF = 10 GHz     |     | -75 |     |      |

| O <sub>P1dB</sub>     | Output 1-dB compression point        | RF = 4 GHz      |     | 12  |     | dBm  |

|                       |                                      | RF = 5 GHz      |     | 12  |     |      |

|                       |                                      | RF = 6 GHz      |     | 12  |     |      |

|                       |                                      | RF = 7 GHz      |     | 12  |     |      |

|                       |                                      | RF = 8 GHz      |     | 12  |     |      |

|                       |                                      | RF = 9 GHz      |     | 12  |     |      |

|                       |                                      | RF = 10 GHz     |     | 12  |     |      |

| IRR                   | Image rejection ratio [calibrated]   | RF = 4 GHz      |     | 43  |     | dB   |

|                       |                                      | RF = 5 GHz      |     | 43  |     |      |

|                       |                                      | RF = 6 GHz      |     | 44  |     |      |

|                       |                                      | RF = 7 GHz      |     | 44  |     |      |

|                       |                                      | RF = 8 GHz      |     | 43  |     |      |

|                       |                                      | RF = 9 GHz      |     | 42  |     |      |

|                       |                                      | RF = 10 GHz     |     | 36  |     |      |

| ISO <sub>RFxIF</sub>  | RF to IF isolation                   | RF = 4 GHz      |     | 40  |     | dB   |

|                       |                                      | RF = 5 GHz      |     | 40  |     |      |

|                       |                                      | RF = 6 GHz      |     | 40  |     |      |

|                       |                                      | RF = 7 GHz      |     | 40  |     |      |

|                       |                                      | RF = 8 GHz      |     | 40  |     |      |

|                       |                                      | RF = 9 GHz      |     | 40  |     |      |

|                       |                                      | RF = 10 GHz     |     | 40  |     |      |

| LEAK <sub>RFxIF</sub> | LO to IF leakage                     | LO = 4 GHz      |     | -35 |     | dBm  |

|                       |                                      | LO = 5 GHz      |     | -35 |     |      |

|                       |                                      | LO = 6 GHz      |     | -35 |     |      |

|                       |                                      | LO = 7 GHz      |     | -35 |     |      |

|                       |                                      | LO = 8 GHz      |     | -35 |     |      |

|                       |                                      | LO = 9 GHz      |     | -35 |     |      |

|                       |                                      | LO = 10 GHz     |     | -35 |     |      |

## Electrical Characteristics (continued)

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER                               | TEST CONDITIONS                                     | MIN                                                             | TYP   | MAX  | UNIT |   |

|-----------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------|-------|------|------|---|

| LEAK <sub>LoRF</sub>                    | LO = 4 GHz                                          |                                                                 | -60   |      | dBm  |   |

|                                         | LO = 5 GHz                                          |                                                                 | -60   |      |      |   |

|                                         | LO = 6 GHz                                          |                                                                 | -52   |      |      |   |

|                                         | LO = 7 GHz                                          |                                                                 | -50   |      |      |   |

|                                         | LO = 8 GHz                                          |                                                                 | -50   |      |      |   |

|                                         | LO = 9 GHz                                          |                                                                 | -45   |      |      |   |

|                                         | LO = 10 GHz                                         |                                                                 | -40   |      |      |   |

| <b>PERFORMANCE TUNING</b>               |                                                     |                                                                 |       |      |      |   |

| G <sub>IQ_CAL</sub>                     | I/Q gain calibration range                          | IMRR_GCAL register full range                                   | ±0.5  |      | dB   |   |

| G <sub>IQ_STEP</sub>                    | I/Q gain calibration step size                      |                                                                 | 0.05  |      | dB   |   |

| PH <sub>IQ_CAL</sub>                    | I/Q phase calibration range                         | IMRR_PCAL register full range                                   | ±20   |      | Deg  |   |

| PH <sub>IQ_STEP</sub>                   | I/Q phase calibration step size                     | Step size can be made reduced to 0.25 deg in fine accuracy mode | 0.45  |      | Deg  |   |

| V <sub>DCOC</sub>                       | calibrated differential DC offset                   |                                                                 | ±/- 2 |      | mV   |   |

| <b>PORTS</b>                            |                                                     |                                                                 |       |      |      |   |

| S11 <sub>RF</sub>                       | RF return loss                                      | RF = 4 GHz                                                      | 8     |      | dB   |   |

|                                         |                                                     | RF = 5 GHz                                                      | 19    |      | dB   |   |

|                                         |                                                     | RF = 6 GHz                                                      | 21    |      | dB   |   |

|                                         |                                                     | RF = 7 GHz                                                      | 16    |      | dB   |   |

|                                         |                                                     | RF = 8 GHz                                                      | 10    |      | dB   |   |

|                                         |                                                     | RF = 9 GHz                                                      | 9     |      | dB   |   |

|                                         |                                                     | RF = 10 GHz                                                     | 9     |      | dB   |   |

| S11 <sub>LO</sub>                       | LO return loss (differential measurement)           | RF = 4 GHz                                                      | 15    |      | dB   |   |

|                                         |                                                     | RF = 5 GHz                                                      | 15    |      | dB   |   |

|                                         |                                                     | RF = 6 GHz                                                      | 20    |      | dB   |   |

|                                         |                                                     | RF = 7 GHz                                                      | 17    |      | dB   |   |

|                                         |                                                     | RF = 8 GHz                                                      | 18    |      | dB   |   |

|                                         |                                                     | RF = 9 GHz                                                      | 17    |      | dB   |   |

|                                         |                                                     | RF = 10 GHz                                                     | 12    |      | dB   |   |

| P <sub>LO_IN</sub>                      | External LO input power                             | 8 GHz RF <sub>IN</sub>                                          | 6     |      | dBm  |   |

| P <sub>LO_OUT</sub>                     | External LO output power <sup>(3)</sup>             | <7 GHz RFout                                                    | 2     |      | dBm  |   |

|                                         |                                                     | <10 GHz RFout                                                   | -1    |      | dBm  |   |

| V <sub>IF_RANGE</sub>                   | IF output voltage swing (differential)              |                                                                 | 2     |      | VPP  |   |

| V <sub>CM</sub>                         | IF common mode voltage, internal or external source |                                                                 | 1.2   | 1.7  | 2    | V |

| P <sub>in_RF</sub>                      | RF input power                                      |                                                                 |       | 5    | dBm  |   |

| <b>LO SYNTHESIZER INPUT SIGNAL PATH</b> |                                                     |                                                                 |       |      |      |   |

| F <sub>OSCIN</sub>                      | Reference oscillator port frequency range           | OSC_2X = 0                                                      | 5     | 1400 | MHz  |   |

|                                         |                                                     | OSC_2X = 1                                                      | 5     | 200  |      |   |

| V <sub>OSCIN</sub>                      | Reference input voltage                             | AC-coupled required <sup>(4)</sup>                              | 0.2   | 2    | Vpp  |   |

| F <sub>MULT</sub>                       | Multiplier frequency (when multiplier enabled)      | Input range                                                     | 30    | 70   | MHz  |   |

|                                         |                                                     | Output range                                                    | 180   | 250  |      |   |

(3) Output power, spurs, and harmonics can vary based on board layout and components.

(4) For lower VCO frequencies, the N divider minimum value can limit the phase detector frequency.

## Electrical Characteristics (continued)

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER                                            |                                                             | TEST CONDITIONS                                                     | MIN   | TYP  | MAX | UNIT   |

|------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------------------|-------|------|-----|--------|

| <b>LO SYNTHESIZER PHASE DETECTOR AND CHARGE PUMP</b> |                                                             |                                                                     |       |      |     |        |

| F <sub>PD</sub>                                      | Phase detector frequency                                    | Integer Mode (FRAC_ORDER = 0)                                       | 0.125 | 400  |     | MHz    |

|                                                      |                                                             | Fractional Mode (FRAC_ORDER = 1,2,3)                                | 5     | 300  |     |        |

|                                                      |                                                             | Fractional Mode (FRAC_ORDER = 4)                                    | 5     | 240  |     |        |

| I <sub>CPOUT</sub>                                   | Charge pump leakage current                                 | CPG = 0                                                             |       | 15   |     | nA     |

|                                                      | Effective charge pump current (sum of up and down currents) | CPG = 4                                                             |       | 3    |     | mA     |

|                                                      |                                                             | CPG = 1                                                             |       | 6    |     |        |

|                                                      |                                                             | CPG = 5                                                             |       | 9    |     |        |

|                                                      |                                                             | CPG = 3                                                             |       | 12   |     |        |

|                                                      |                                                             | CPG = 7                                                             |       | 15   |     |        |

| PN <sub>1/F</sub>                                    | Normalized PLL flicker noise                                | F <sub>PD</sub> = 100 MHz, F <sub>VCO</sub> = 12 GHz <sup>(5)</sup> |       | -129 |     | dBc/Hz |

| PN <sub>FLAT</sub>                                   | Normalized PLL thermal noise floor                          |                                                                     |       | -236 |     | dBc/Hz |

(5) The PLL noise contribution is measured using a clean reference and a wide loop bandwidth and is composed into flicker and flat components.  $PLL_{FLAT} = PLL_{FOM} + 20\log(F_{VCO} / F_{PD}) + 10\log(F_{PD} / 1Hz)$ .  $PLL_{FLICKER}(\text{offset}) = PLL_{FLICKER\_NORM} + 20\log(F_{VCO} / 1GHz) - 10\log(\text{offset frequency} / 10kHz)$ . Once these two components are found, the total PLL noise can be calculated as  $PLL_{NOISE} = 10\log(10^{PLL_{FLAT}/10} + 10^{PLL_{FLICKER}/10})$ .

## Electrical Characteristics (continued)

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER                 |                                                                                                                                      | TEST CONDITIONS              | MIN  | TYP | MAX | UNIT   |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-----|-----|--------|

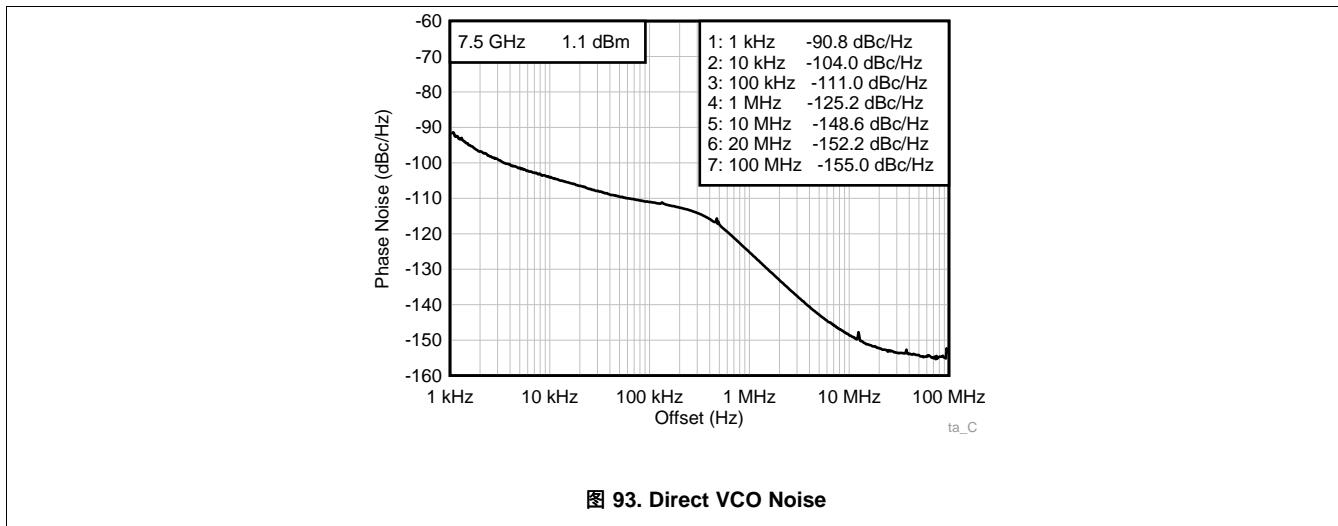

| <b>LO SYNTHESIZER VCO</b> |                                                                                                                                      |                              |      |     |     |        |

| PNvco                     | Open loop VCO phase noise                                                                                                            | 8 GHz VCO, 10 kHz offset     | -80  |     |     |        |

|                           |                                                                                                                                      | 8 GHz VCO, 100 kHz offset    | -107 |     |     |        |

|                           |                                                                                                                                      | 8 GHz VCO, 1 MHz offset      | -128 |     |     |        |

|                           |                                                                                                                                      | 8 GHz VCO, 10 MHz offset     | -148 |     |     |        |

|                           |                                                                                                                                      | 8 GHz VCO, 90 MHz offset     | -157 |     |     |        |

|                           |                                                                                                                                      | 9.2 GHz VCO, 10 kHz offset   | -79  |     |     |        |

|                           |                                                                                                                                      | 9.2 GHz VCO, 100 kHz offset  | -105 |     |     |        |

|                           |                                                                                                                                      | 9.2 GHz VCO, 1 MHz offset    | -127 |     |     |        |

|                           |                                                                                                                                      | 9.2 GHz VCO, 10 MHz offset   | -147 |     |     |        |

|                           |                                                                                                                                      | 9.2 GHz VCO, 90 MHz offset   | -157 |     |     |        |

|                           |                                                                                                                                      | 10.3 GHz VCO, 10 kHz offset  | -77  |     |     |        |

|                           |                                                                                                                                      | 10.3 GHz VCO, 100 kHz offset | -104 |     |     |        |

|                           |                                                                                                                                      | 10.3 GHz VCO, 1 MHz offset   | -126 |     |     |        |

|                           |                                                                                                                                      | 10.3 GHz VCO, 10 MHz offset  | -147 |     |     |        |

|                           |                                                                                                                                      | 10.3 GHz VCO, 90 MHz offset  | -157 |     |     |        |

|                           |                                                                                                                                      | 11.3 GHz VCO, 10 kHz offset  | -76  |     |     |        |

|                           |                                                                                                                                      | 11.3 GHz VCO, 100 kHz offset | -103 |     |     |        |

|                           |                                                                                                                                      | 11.3 GHz VCO, 1 MHz offset   | -125 |     |     | dBc/Hz |

|                           |                                                                                                                                      | 11.3 GHz VCO, 10 MHz offset  | -145 |     |     |        |

|                           |                                                                                                                                      | 11.3 GHz VCO, 90 MHz offset  | -158 |     |     |        |

|                           |                                                                                                                                      | 12.5 GHz VCO, 10 kHz offset  | -74  |     |     |        |

|                           |                                                                                                                                      | 12.5 GHz VCO, 100 kHz offset | -100 |     |     |        |

|                           |                                                                                                                                      | 12.5 GHz VCO, 1 MHz offset   | -123 |     |     |        |

|                           |                                                                                                                                      | 12.5 GHz VCO, 10 MHz offset  | -144 |     |     |        |

|                           |                                                                                                                                      | 12.5 GHz VCO, 90 MHz offset  | -157 |     |     |        |

|                           |                                                                                                                                      | 13.3 GHz VCO, 10 kHz offset  | -73  |     |     |        |

|                           |                                                                                                                                      | 13.3 GHz VCO, 100 kHz offset | -100 |     |     |        |

|                           |                                                                                                                                      | 13.3 GHz VCO, 1 MHz offset   | -122 |     |     |        |

|                           |                                                                                                                                      | 13.3 GHz VCO, 10 MHz offset  | -143 |     |     |        |

|                           |                                                                                                                                      | 13.3 GHz VCO, 90 MHz offset  | -155 |     |     |        |

|                           |                                                                                                                                      | 14.5 GHz VCO, 10 kHz offset  | -73  |     |     |        |

|                           |                                                                                                                                      | 14.5 GHz VCO, 100 kHz offset | -99  |     |     |        |

|                           |                                                                                                                                      | 14.5 GHz VCO, 1 MHz offset   | -121 |     |     |        |

|                           |                                                                                                                                      | 14.5 GHz VCO, 10 MHz offset  | -143 |     |     |        |

|                           |                                                                                                                                      | 14.5 GHz VCO, 90 MHz offset  | -152 |     |     |        |

| t <sub>VCO_CAL</sub>      | VCO calibration speed, switch across the entire frequency band, F <sub>OSC</sub> = 200 MHz, F <sub>PD</sub> = 100 MHz <sup>(6)</sup> | No assist                    | 50   |     |     | μs     |

|                           |                                                                                                                                      | Close frequency              | 20   |     |     |        |

(6) See Application and Implementation for more details on the different VCO calibration modes.

## Electrical Characteristics (continued)

Measurements are done at 25 degree C. Parameters are measured at IF = 65MHz with high side injection, unless otherwise noted. Measurements are done with external VCM = 1.7V.

| PARAMETER                                                  |                                                           | TEST CONDITIONS                            | MIN        | TYP  | MAX | UNIT  |

|------------------------------------------------------------|-----------------------------------------------------------|--------------------------------------------|------------|------|-----|-------|

| K <sub>VCO</sub>                                           | VCO gain                                                  | 8 GHz                                      |            | 89   |     | MHz/V |

|                                                            |                                                           | 9.2 GHz                                    |            | 93   |     |       |

|                                                            |                                                           | 10.3 GHz                                   |            | 110  |     |       |

|                                                            |                                                           | 11.3 GHz                                   |            | 124  |     |       |

|                                                            |                                                           | 12.5 GHz                                   |            | 189  |     |       |

|                                                            |                                                           | 13.3 GHz                                   |            | 182  |     |       |

|                                                            |                                                           | 14.5 GHz                                   |            | 205  |     |       |

| ΔT <sub>CL</sub>                                           | Allowable temperature drift when VCO is not re-calibrated |                                            |            | 125  |     | °C    |

| H2                                                         | VCO second harmonic                                       | F <sub>VCO</sub> = 8 GHz, divider disabled |            | -30  |     | dBc   |

| H3                                                         | VCO third harmonic                                        | F <sub>VCO</sub> = 8 GHz, divider disabled |            | -40  |     |       |

| <b>SYNC PIN AND PHASE ALIGNMENT</b>                        |                                                           |                                            |            |      |     |       |

| F <sub>OSCIN_SYNC</sub>                                    | Maximum usable OSCIN frequency with SYNC pin              | Category 3 (int LO mode)                   | 0          | 100  |     | MHz   |

|                                                            |                                                           | Category 1 or 2                            | 0          | 1400 |     |       |

| <b>DIGITAL INTERFACE (SCK, SDI, CSB, MUXOUT, SYNC, CE)</b> |                                                           |                                            |            |      |     |       |

| V <sub>IH</sub>                                            | High level input voltage                                  |                                            | 1.4        | VCC  | V   |       |

| V <sub>IL</sub>                                            | Low level input voltage                                   |                                            | 0          | 0.4  | V   |       |

| I <sub>IH</sub>                                            | High level input current                                  |                                            | -50        | 50   | μA  |       |

| I <sub>IL</sub>                                            | Low level input current                                   |                                            | -50        | 50   | μA  |       |

| V <sub>OH</sub>                                            | High level output voltage                                 | I <sub>L</sub> = -5 mA                     | VCC – 0.55 |      | V   |       |

| V <sub>OL</sub>                                            | High level output current                                 | I <sub>L</sub> = 5 mA                      |            | 0.55 | V   |       |

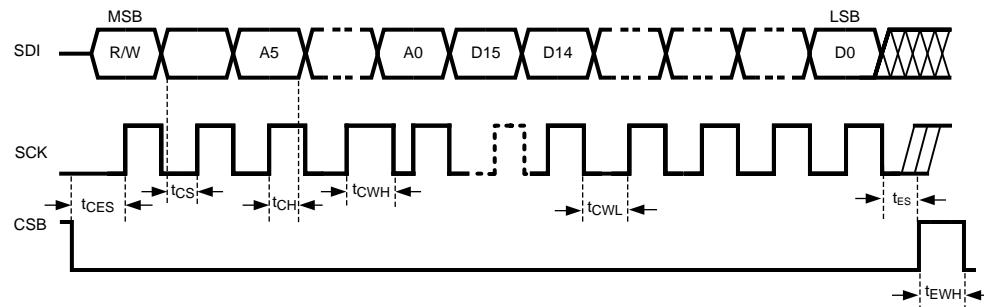

## 6.6 Timing Requirements

|                                                 |                                                  | MIN | NOM | MAX | UNIT |

|-------------------------------------------------|--------------------------------------------------|-----|-----|-----|------|

| <b>SYNC</b>                                     |                                                  |     |     |     |      |

| t <sub>SETUP</sub>                              | Setup time for pin relative to OSCIN rising edge | 2.5 |     |     | ns   |

| t <sub>HOLD</sub>                               | Hold time for pin relative to OSCIN rising edge  | 2   |     |     | ns   |

| <b>DIGITAL WRITE INTERFACE<sup>(1)</sup></b>    |                                                  |     |     |     |      |

| F <sub>SPI_WRITE</sub>                          | SPI write speed                                  |     |     | 50  | MHz  |

| t <sub>ES</sub>                                 | Clock to enable low time                         | 5   |     |     | ns   |

| t <sub>CS</sub>                                 | Data to clock setup time                         | 2   |     |     | ns   |

| t <sub>CH</sub>                                 | Data to clock hold time                          | 2   |     |     | ns   |

| t <sub>CWH</sub>                                | Clock pulse width high                           | 5   |     |     | ns   |

| t <sub>CWL</sub>                                | Clock pulse width low                            | 10  |     |     | ns   |

| t <sub>CES</sub>                                | Enable to clock setup time                       | 10  |     |     | ns   |

| t <sub>EWH</sub>                                | Enable pulse width high                          | 10  |     |     | ns   |

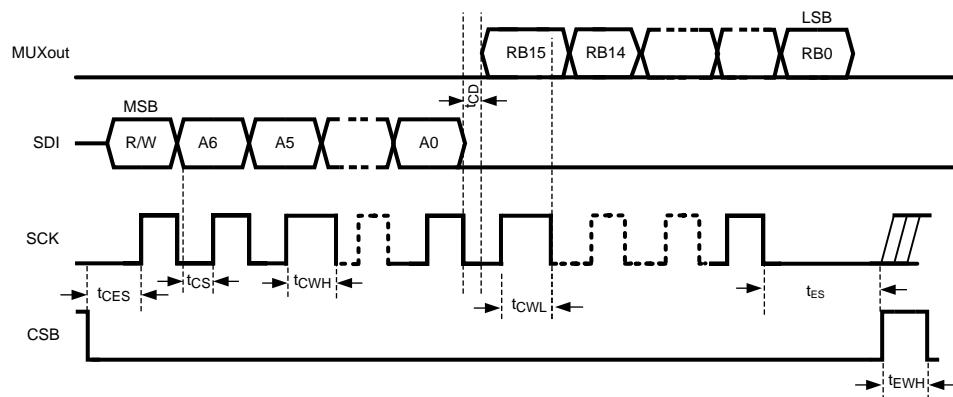

| <b>DIGITAL READBACK INTERFACE<sup>(2)</sup></b> |                                                  |     |     |     |      |

| F <sub>SPI_READ</sub>                           | SPI readback speed                               |     |     | 50  | MHz  |

| t <sub>ES</sub>                                 | Clock to enable low time                         | 10  |     |     | ns   |

| t <sub>CS</sub>                                 | Clock to data wait time                          |     |     | 10  | ns   |

| t <sub>CWH</sub>                                | Clock pulse width high                           | 10  |     |     | ns   |

| t <sub>CWL</sub>                                | Clock pulse width low                            | 10  |     |     | ns   |

| t <sub>CES</sub>                                | Enable to clock setup time                       | 10  |     |     | ns   |

(1) See Figure 1

(2) See Figure 2

## Timing Requirements (continued)

|           |                         | MIN | NOM | MAX | UNIT |

|-----------|-------------------------|-----|-----|-----|------|

| $t_{EWH}$ | Enable pulse width high | 10  |     |     | ns   |

图 1. Serial Data Input Timing Diagram

There are several other considerations for writing on the SPI:

- The R/W bit must be set to 0.

- The signal on the SDI pin is clocked into a shift register on each rising edge of the SCK pin.

- The CSB must be held low for data to be clocked. Device ignores clock pulses if CSB is held high.

- The CSB transition from high to low must occur when SCK is low.

- When SCK and SDI lines are shared between devices, TI recommends holding the CSB line high on any devices besides the intended programming target.

图 2. Serial Data Readback Timing Diagram

There are several other considerations for SPI readback:

- The R/W bit must be set to 1.

- The MUXOUT pin is always for the address portion of the transaction.

- The address on the SDI pin is clocked into a shift register on each rising edge of the SCK pin.

- The data portion of the transaction on the SDI line is always ignored.

- The data on the MUXOUT pin should be considered valid on each rising edge of the SCK pin, provided all timing requirements are met.

- All CSB considerations for SPI writing also apply to SPI readback.

## 6.7 Typical Characteristics

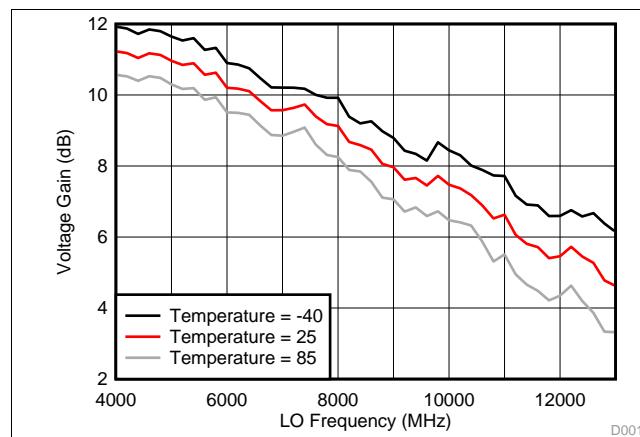

图 3. Voltage Gain Across LO Frequency for Internal LO Mode

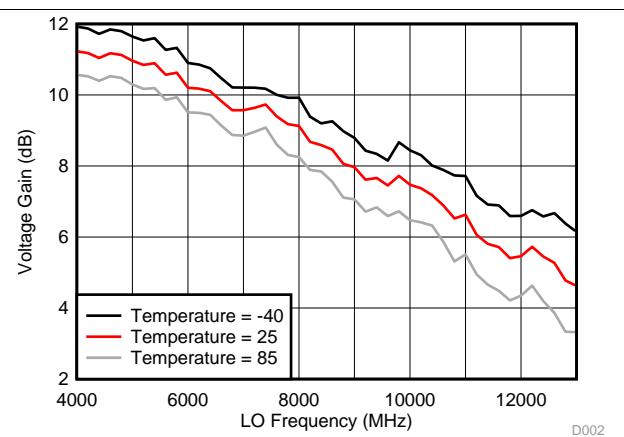

图 4. Voltage Gain Across LO frequency for External LO Mode

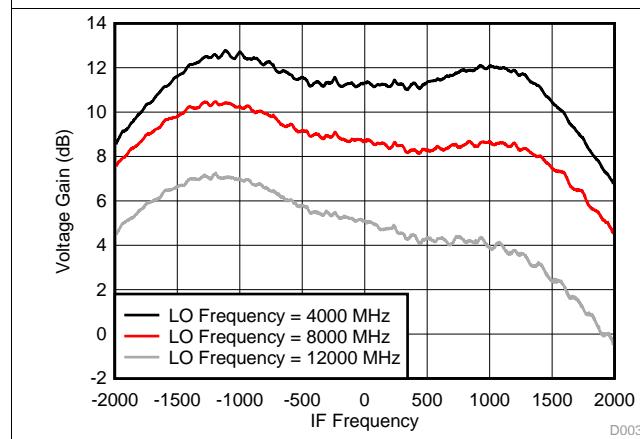

图 5. Voltage Gain Across IF Frequency for Internal LO Mode

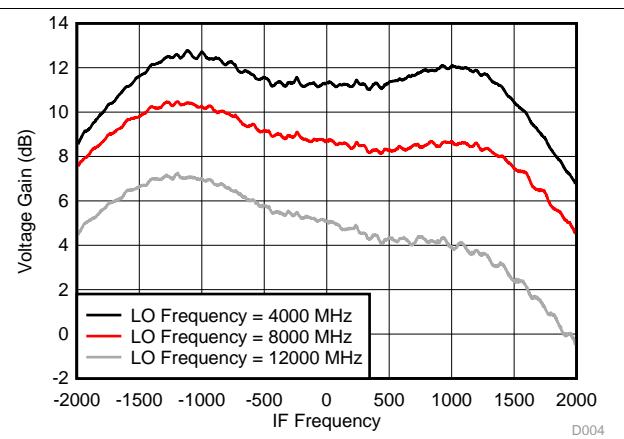

图 6. Voltage Gain Across IF Frequency for External LO Mode

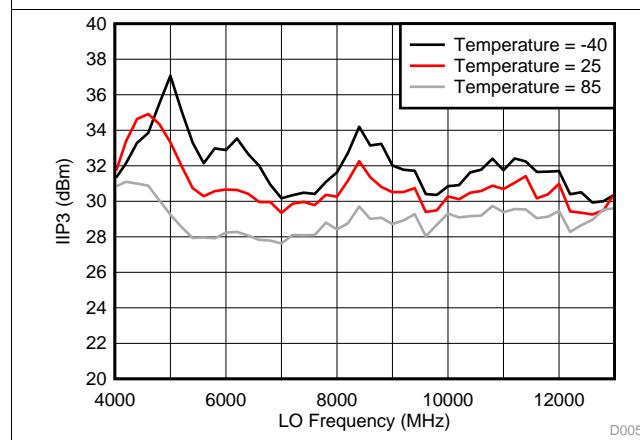

图 7. IIP3 Across LO Frequency for Internal LO Mode

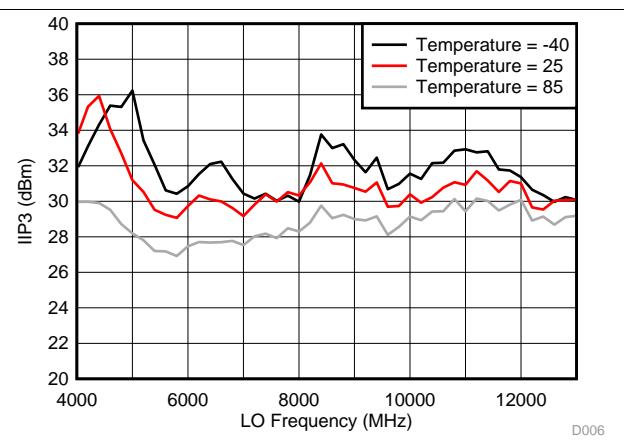

图 8. IIP3 Across LO Frequency for External LO Mode

## Typical Characteristics (接下页)

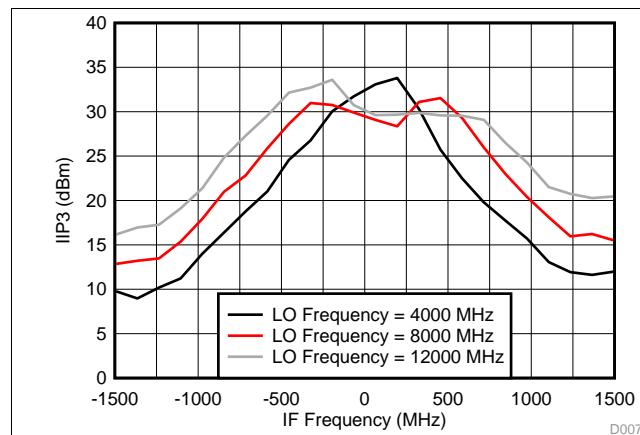

图 9. IIP3 Across IF Frequency for Internal LO Mode

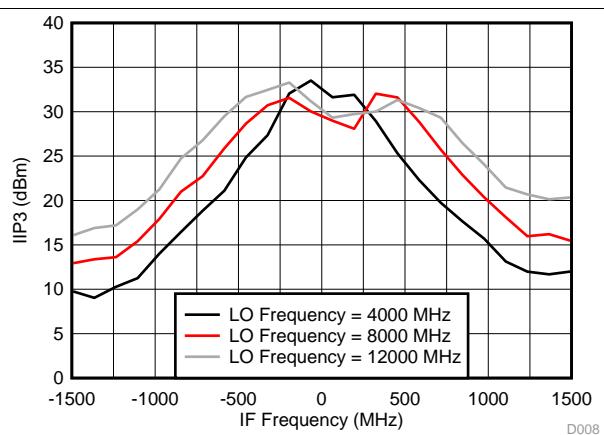

图 10. IIP3 Across IF Frequency for External LO Mode

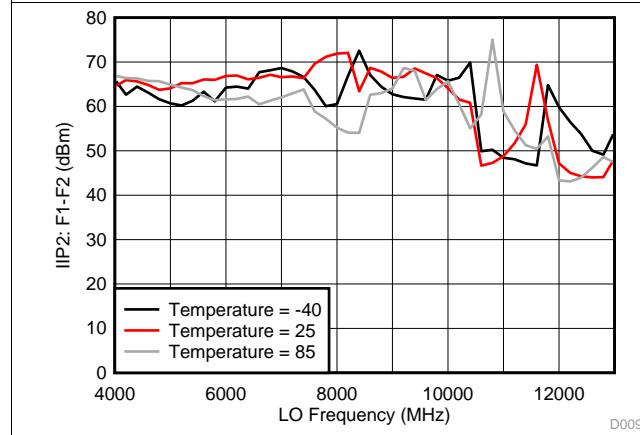

图 11. IIP2: F1-F2 Across LO Frequency for Internal LO Mode

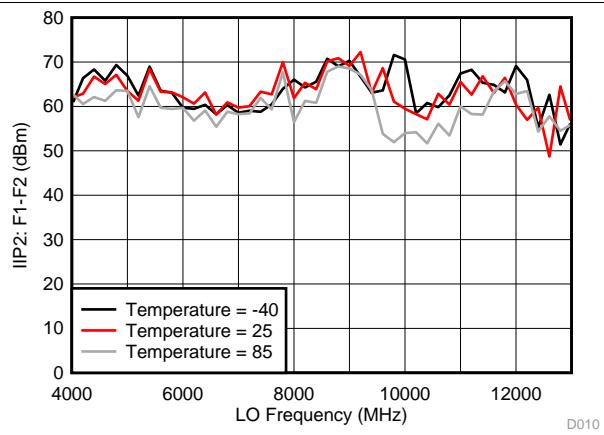

图 12. IIP2: F1-F2 Across LO Frequency for External LO Mode

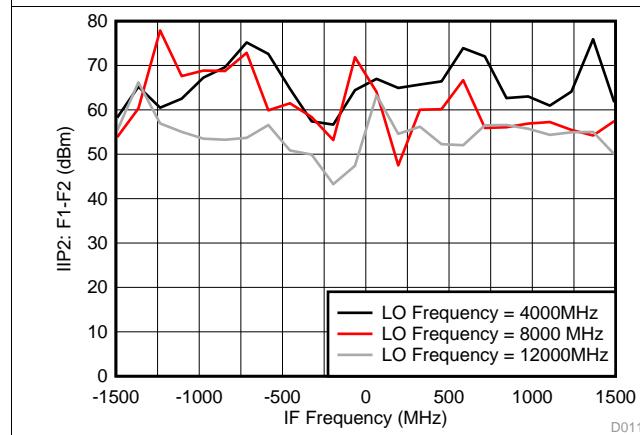

图 13. IIP2: F1-F2 Across IF Frequency for Internal LO Mode

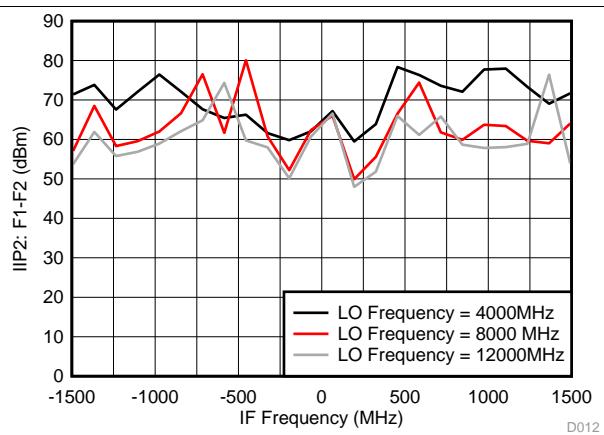

图 14. IIP2: F1-F2 Across IF Frequency for External LO Mode

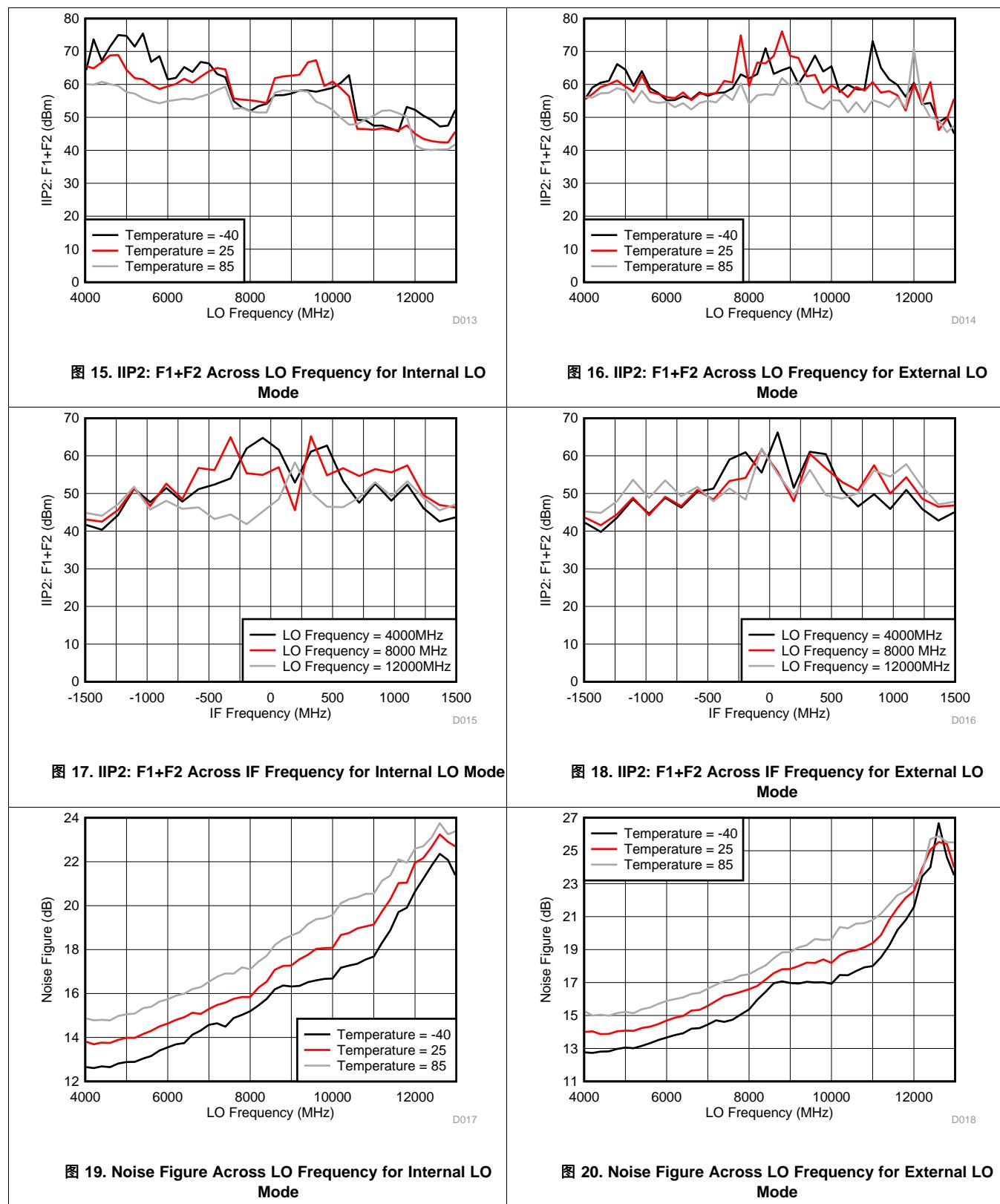

**Typical Characteristics (接下页)**

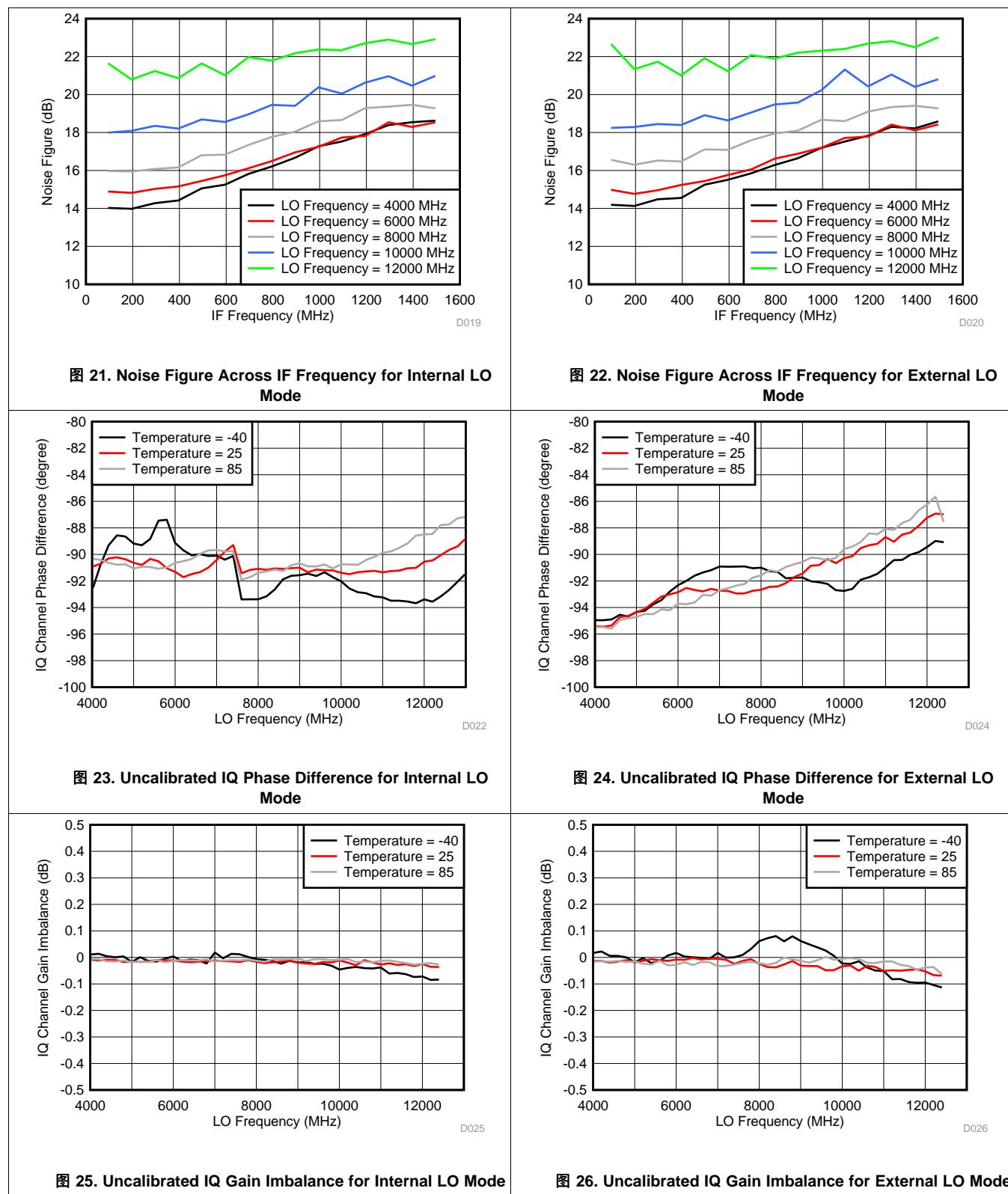

## Typical Characteristics (接下页)

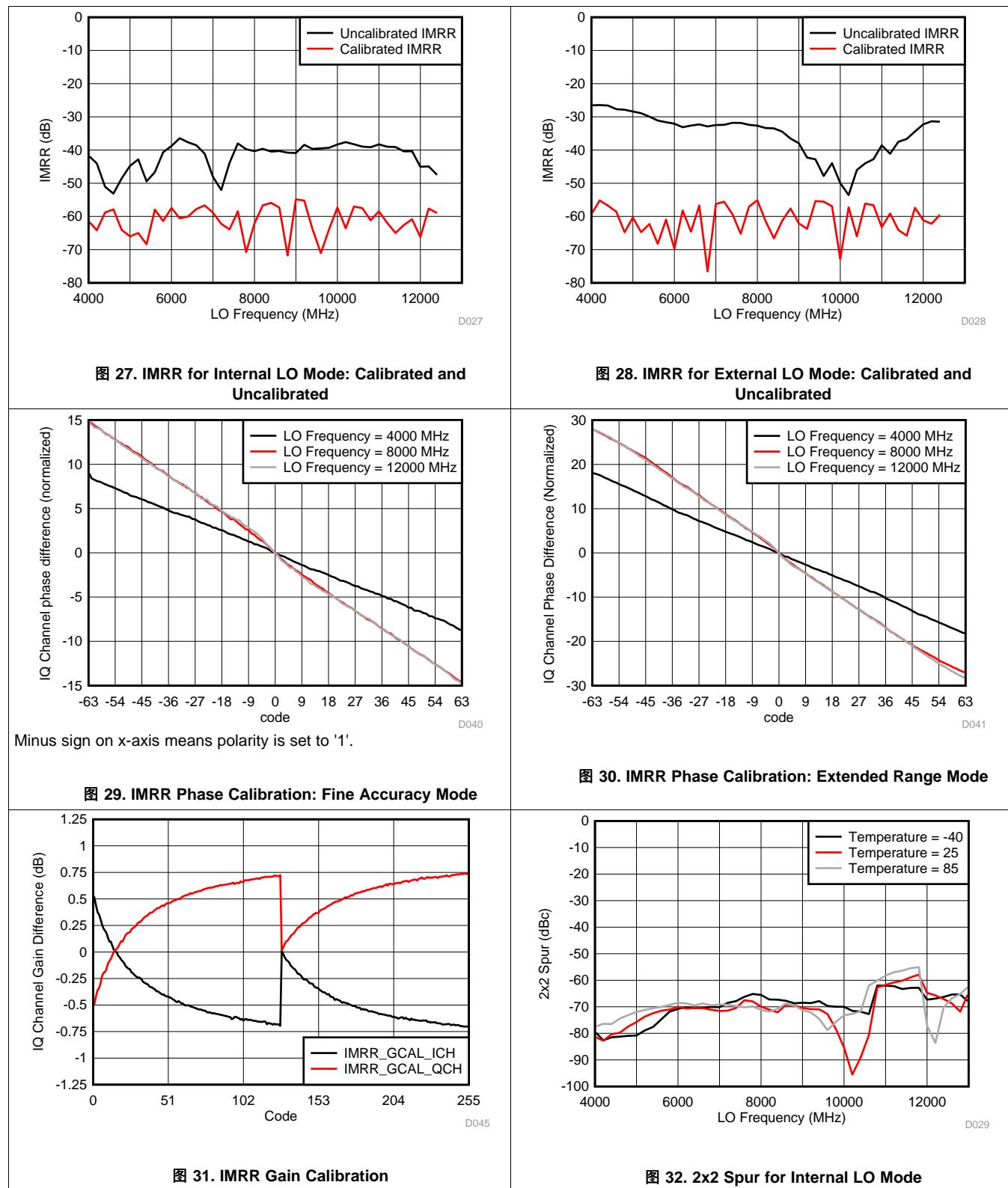

## Typical Characteristics (接下页)

## Typical Characteristics (接下页)

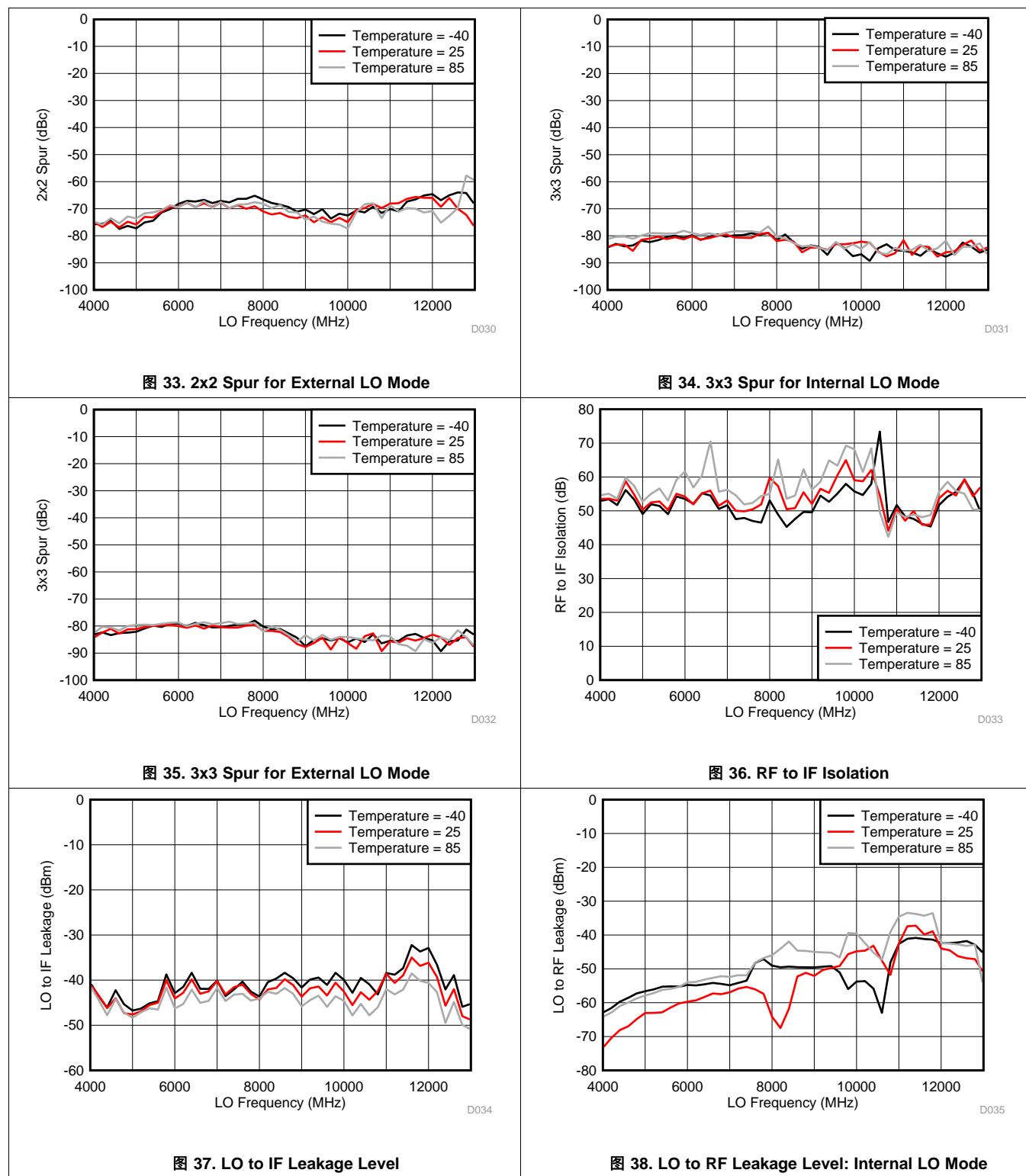

图 33. 2x2 Spur for External LO Mode

图 34. 3x3 Spur for Internal LO Mode

图 35. 3x3 Spur for External LO Mode

图 36. RF to IF Isolation

图 37. LO to IF Leakage Level

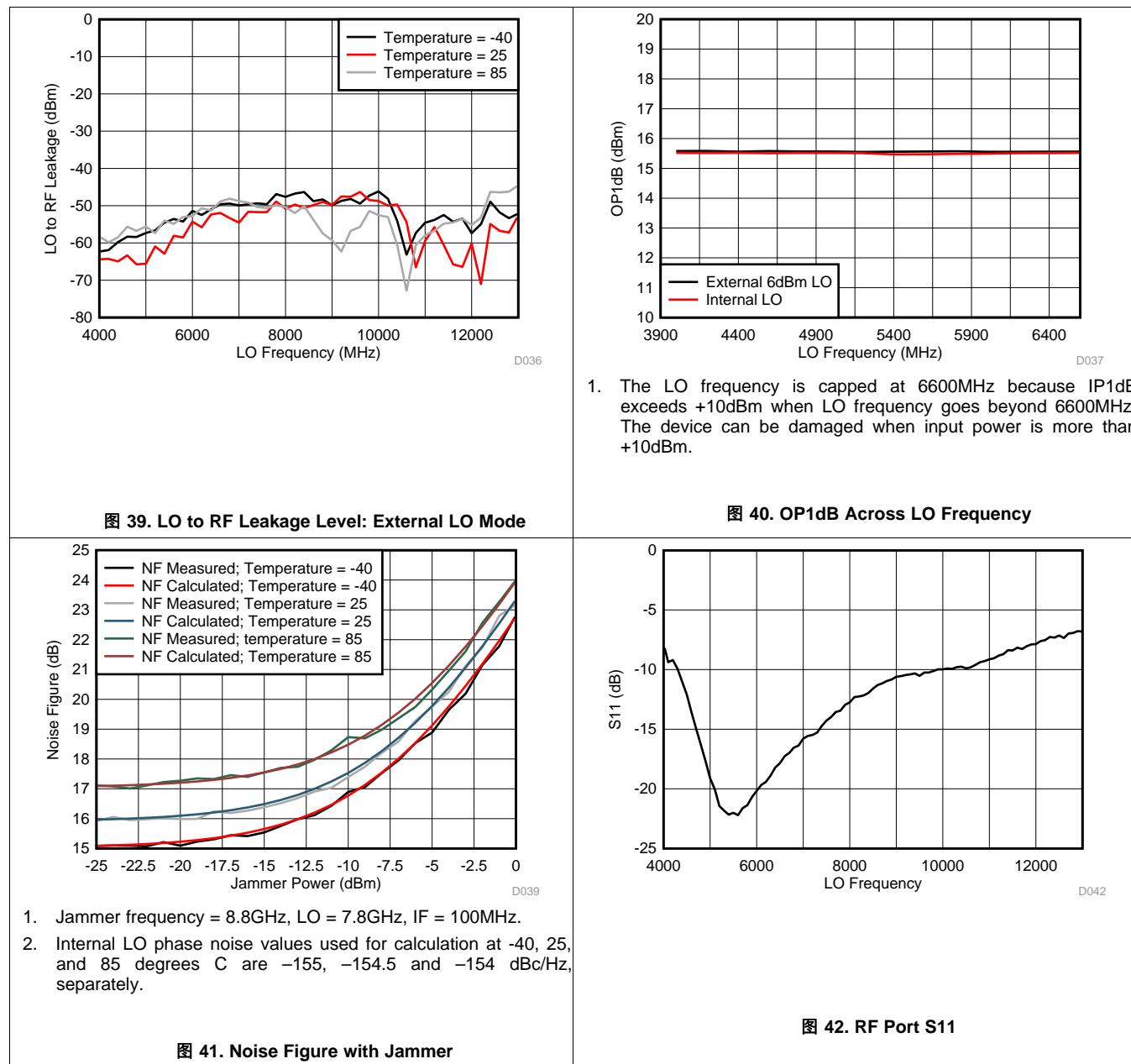

图 38. LO to RF Leakage Level: Internal LO Mode

**Typical Characteristics (接下页)**

## Typical Characteristics (接下页)

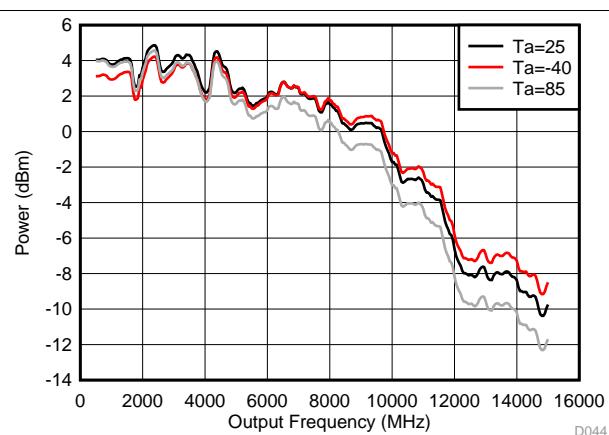

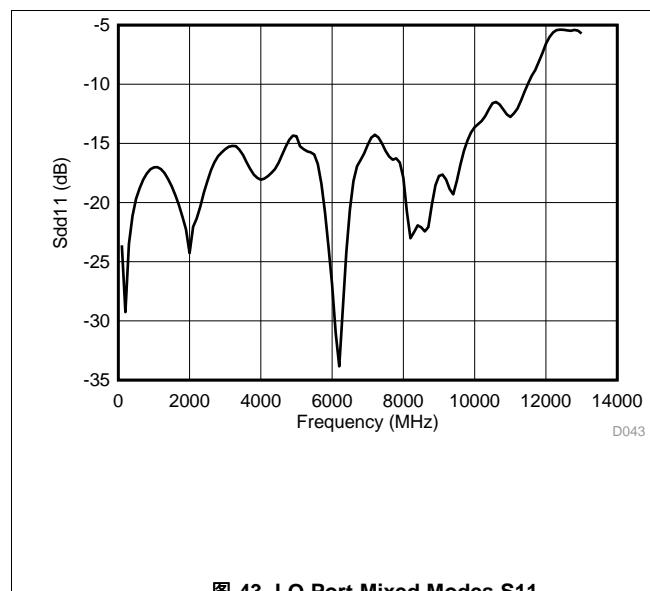

1. Board losses and mismatch are not subtracted out. True output power may be higher. This plot shows single-ended LO output power only. Differential output power can be higher.

Measurements are done at 25 degree C unless temperature is specified in the plots.

For measurements across LO frequency, IF = 65MHz, and LO injection type is high side injection. For measurements across IF frequency, high side injection is applied

For all measurements that require RF input, RF input power = -10 dBm unless otherwise specified.

For two-tone measurements, the separation between two tones is 17MHz.

For all measurements, internal 1.7V VCM is applied.

For all external LO mode measurements, LO power = +6 dBm.

IF baluns used for measurements are: ADT2-18+ from Mini-Circuits™.

LO balun used for measurements is: BIB-100G from PPM-Test™.

RF combiner used for measurements of IP2, IP3 and NF with jammer is: 4426-2 from Narda-MITEQ™.

All path losses are calibrated out.

## 7 Detailed Description

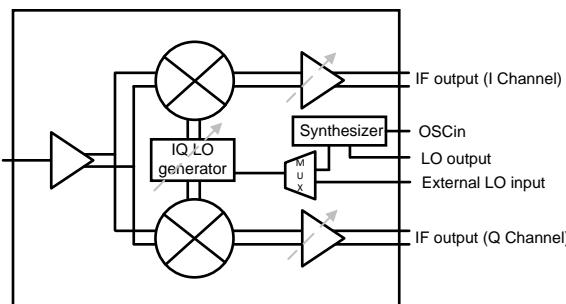

### 7.1 Overview

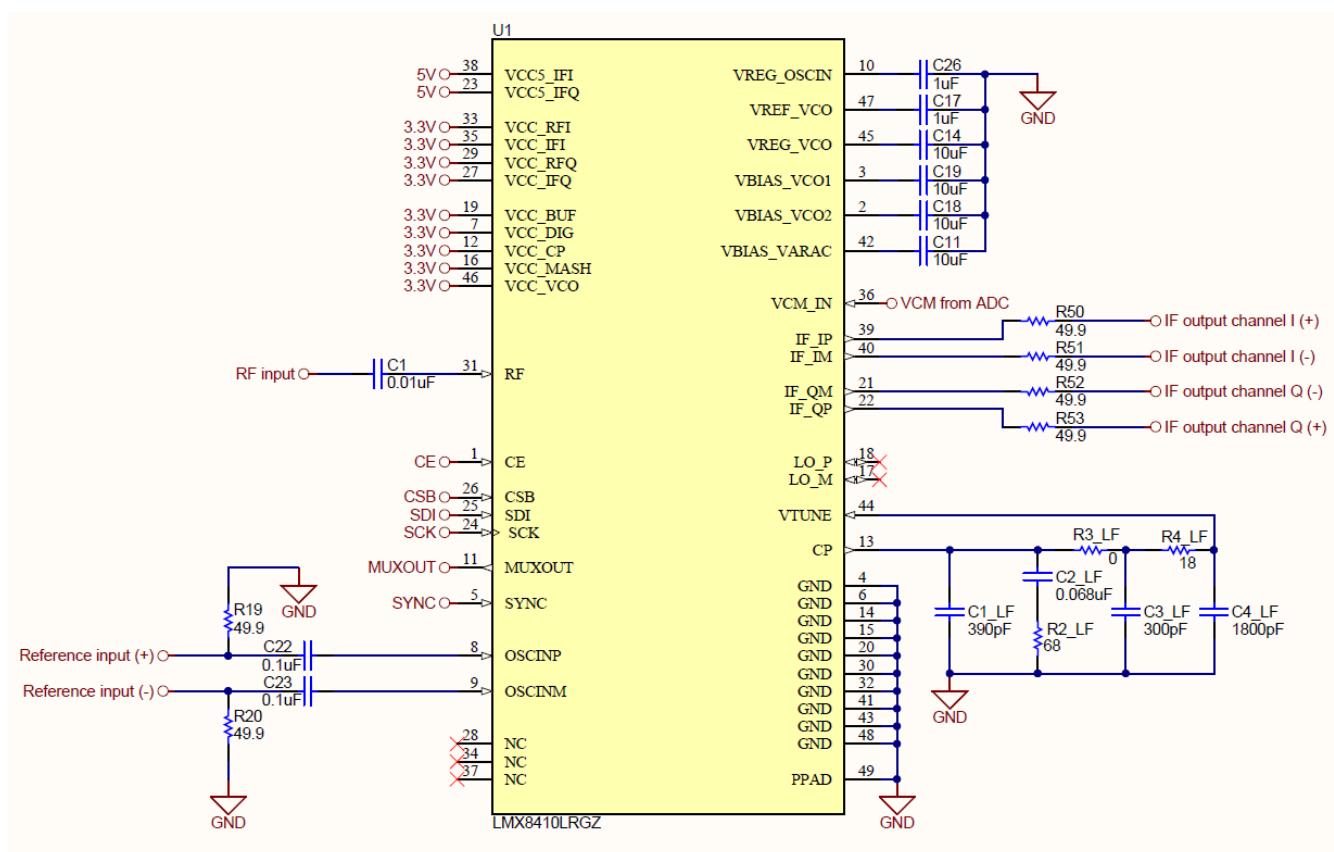

The LMX8410L is a high-performance I/Q demodulator with an RF input range of 4 to 10 GHz and an IF output range of DC to 1350 MHz. This device integrates many components to allow high system performance as well as simplified design. There is an integrated synthesizer that generates wide-band frequencies at very low phase noise, with signal carefully conditioned for driving the mixer LO port. The RF input is single ended, enabled by an integrated wide-band RF balun at the front end. The two mixers on each I/Q channel are highly linear with optimized filtering and interfacing with components on each port. The IF amplifier is a high gain and high linearity component, saving users from matching discrete amplifiers and being restricted by common mode voltages typically encountered when interfacing mixers and ADC's. In addition to high linearity and low noise performance, the LMX8410L comes equipped with many features to further optimize certain parameters. The automatic DC offset calibration is run by an internal automatic algorithm which will sense and tune the DC offset between the N and P sides of the differential signal of each IF amplifier, thus ensuring optimal performance when directly DC coupled to the ADC. The I/Q calibration knob allows tuning blocks within the mixer and IF amplifier to balance both the gain and the phase of the I/Q output signals, thus giving the user capability to adjust and achieve high image rejection. The internal synthesizer also has a feature of synchronization, which allows multiple LMX8410L designed in parallel to have synchronized LO signal phase.

### 7.2 Functional Block Diagram

## 7.3 Feature Description

### 7.3.1 Device Configurations and Feature Description

#### 7.3.1.1 RF, LO and IF Interfaces

##### 7.3.1.1.1 RF Interface

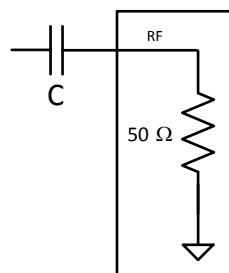

LMX8410 RF input stage provides a wideband input matching in complete RF frequency range. The RF interface requires an external DC block capacitor.

图 45. RF Interface

##### 7.3.1.1.2 LO Interface

LO interface for LMX8410 serves dual functionality:

1. Drive the VCO or channel divider output to pin LO\_M and LO\_P.

2. Inject external LO signal in external LO mode where on-chip synthesizer needs to be bypassed.

##### 7.3.1.1.2.1 LO Interface as Output Port

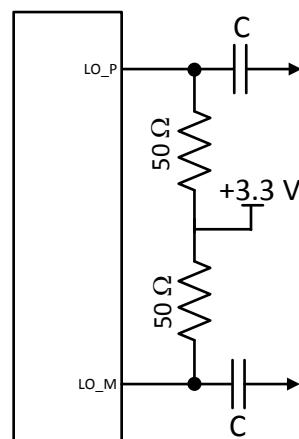

When LO interface operates as output port, it drives either VCO or Channel Divider output to the port. The device provides open collector output. Therefore, a pair of off-chip load resistors or inductors are needed in order to have LO output power.

图 46. LO Port Operating In Output Mode Requires Load Resistors Or Inductors

##### 7.3.1.1.2.2 LO Interface as Input Port

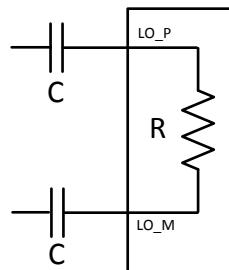

When LO interface operates as input port, the pull-up resistors or inductors must be removed. Device pins must be AC coupled with DC block. LO pins offer wideband differential 100 Ohm termination to enable port matching. The value of termination can be set to 100Ohm, 200Ohm or high impedance through register EXTLO\_INT\_MATCH\_RES (R123<1:0>). It is recommended to keep the termination setting to 100 ohm during external LO injection and to high impedance mode while LO is brought out from the device.

## Feature Description (接下页)

图 47. LO Port Operating In Input Mode

### 7.3.1.1.3 Baseband Interface

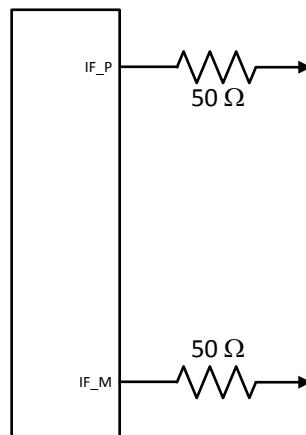

LMX8410 has a low impedance output driver capable of driving the resistive as well as capacitive loads. Therefore, a pair of 50 ohm off-chip resistors can be placed in both IF\_P and IF\_M paths to provide 100Ohm differential matching if IF port matching is required.

图 48. IF Interface Requires External Resistors for 100Ohm Differential Matching

### 7.3.1.2 Device Configurations Overview

Follow below steps to configure the device successfully.

#### 7.3.1.2.1 Initialize the Device

After the device is powered on, follow below setups in sequence.

1. Set R127 = 0x0003

2. Set R6 = 0x0100

3. Set R127 = 0x0000

4. Load device configuration bits.

#### 7.3.1.2.2 Configure LO Modes

Refer to [表 5](#) to set up correct LO modes. After LO mode is configured, In case of internal LO mode, lock the integrated synthesizer and jump to [Perform DCOC \(DC Offset Correction\)](#). In case of external LO mode, go to [Set Up External LO Clock](#).

## Feature Description (接下页)

### 7.3.1.2.3 Set Up External LO Clock

Follow below steps to set up external LO clock:

1. Set external LO divider. Refer to [State Machine Clock](#)

2. Provide external LO signal on the pin.

3. Enable the divider by setting EXTLO\_CLK\_DIV\_EN (R81<7:6>) to 3. This step should be done only after valid external LO signal is driven on the pin.

4. Select SM clock source towards external LO driven SM clock by setting SM\_CLK\_SEL (R81<0>) = 1.

5. Wait for 100 usec before performing DCOC.

### 7.3.1.2.4 Perform DCOC (DC Offset Correction)

Perform DCOC for both I and Q channels. Refer to [DCOC \(DC Offset Correction\)](#) for detailed instructions.

### 7.3.1.2.5 Turn Off SM Clock

Turn off SM clock after DCOC to remove coupling spurs from clock signals.

1. In internal LO mode, set SM\_CLK\_EN (R2<10>) to 0.

2. In external LO mode, set EXTLO\_CLK\_DIV\_EN (R81<7:6>) to 0.

### 7.3.1.2.6 Perform IMRR (Image Rejection Ratio) Calibration

Refer to [Image Rejection Calibration](#) for detailed instructions.

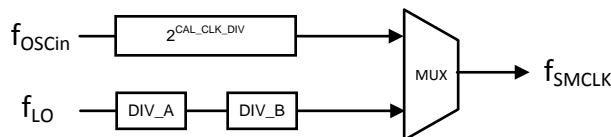

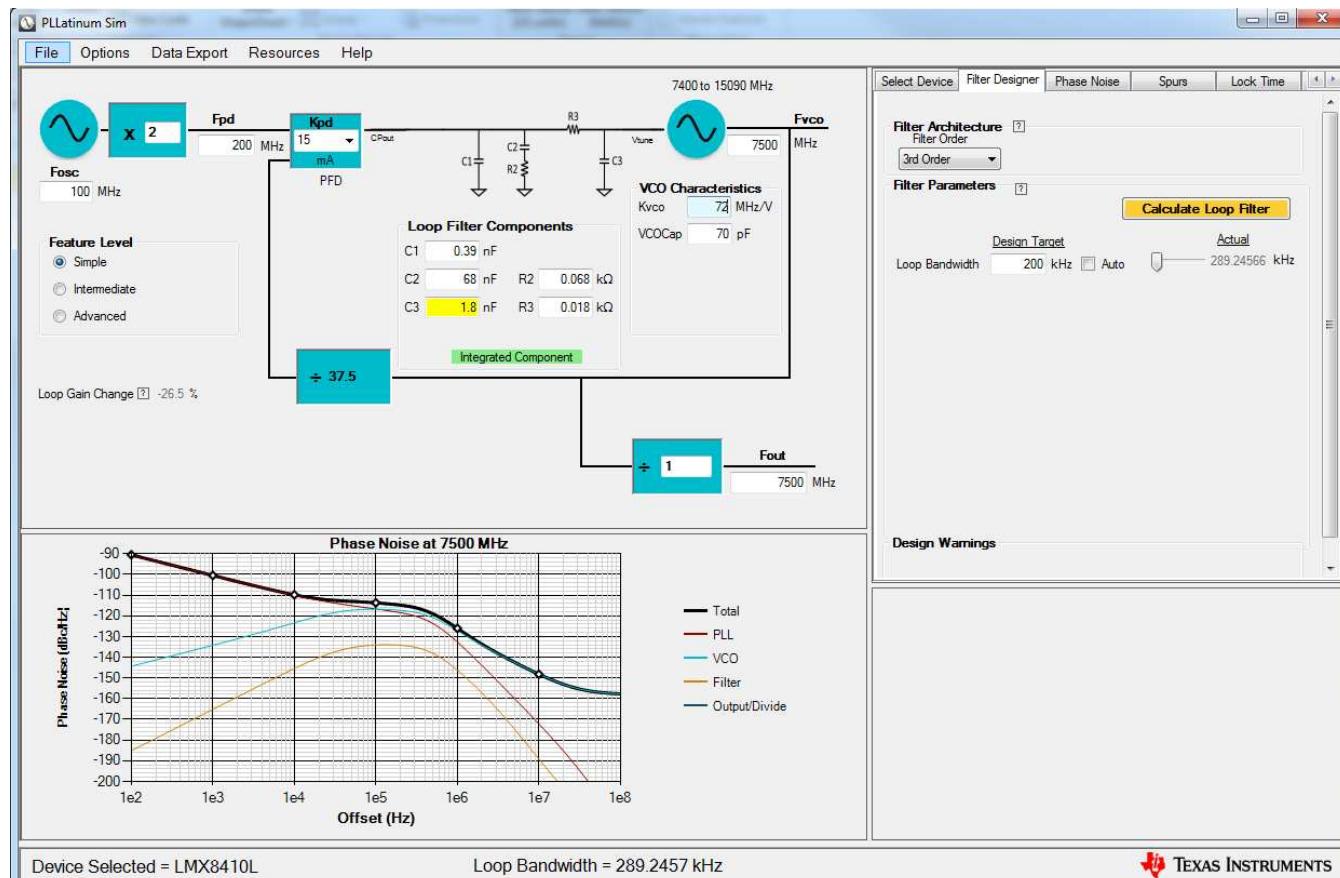

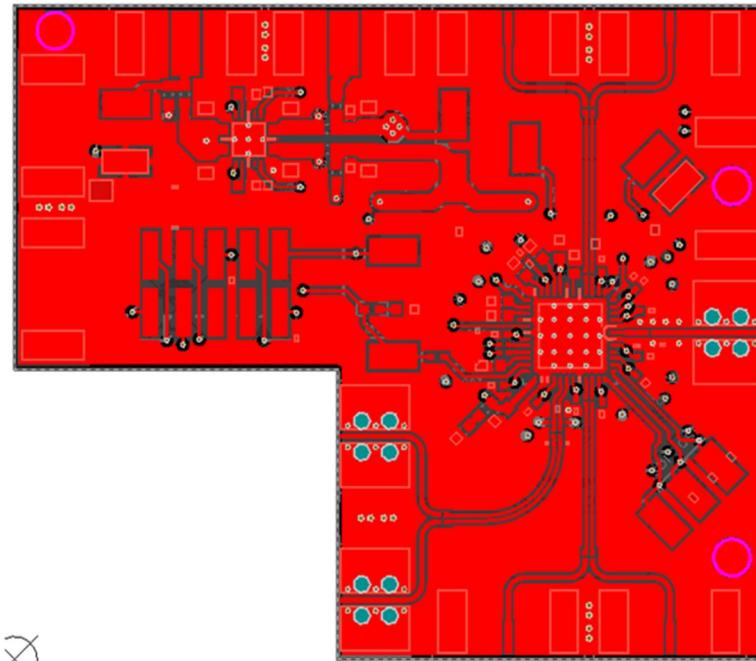

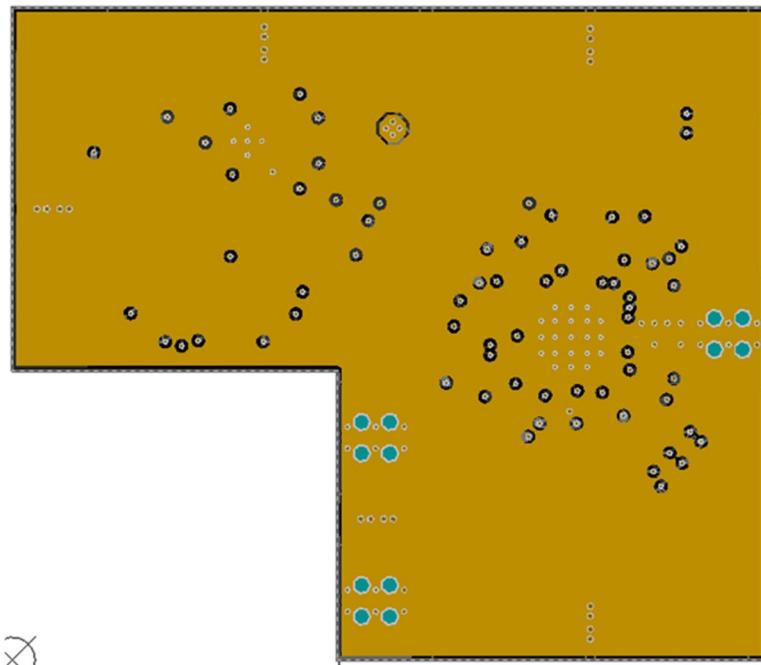

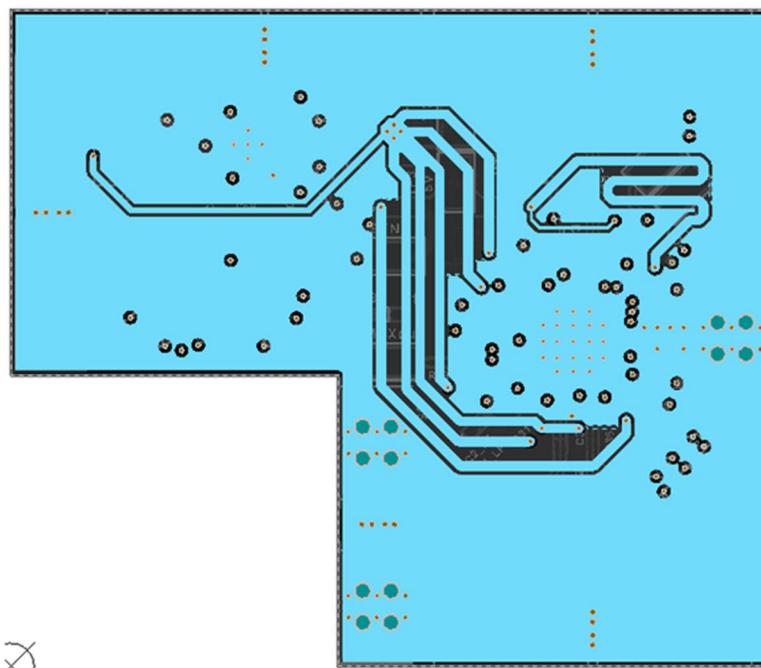

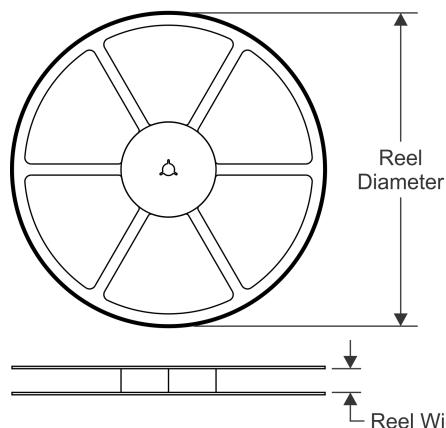

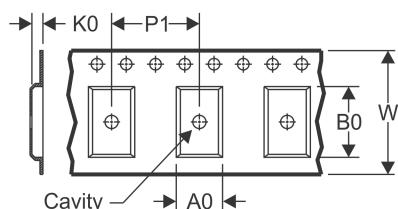

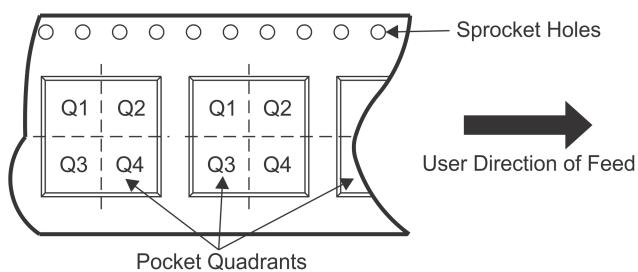

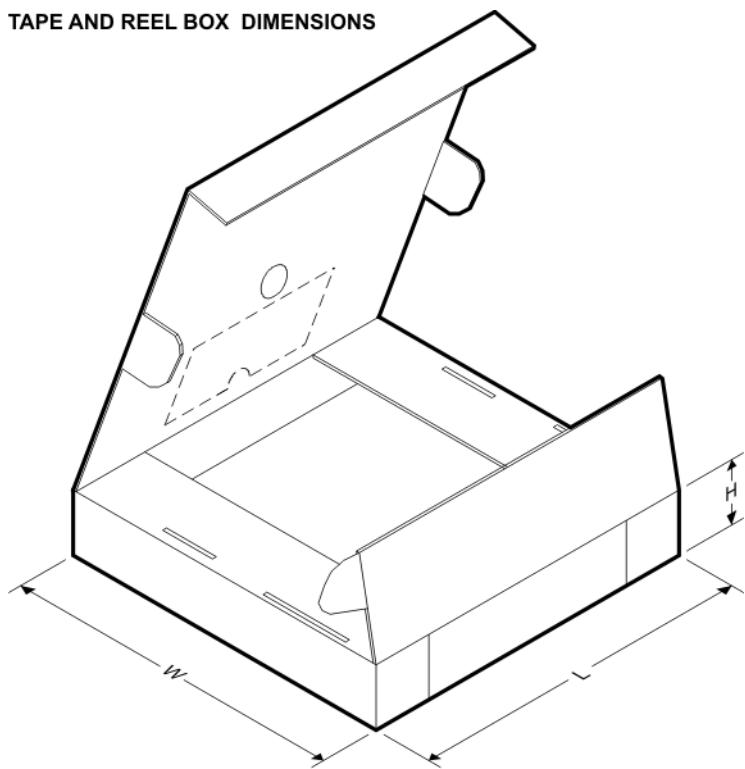

### 7.3.1.3 State Machine Clock