# DLPC230S-Q1 Automotive DMD Controller for the DLP553x-Q1 Chipset

#### 1 Features

- Qualified for automotive applications

- AEC-Q100 qualified with the following results:

- Device temperature grade 2: –40°C to +105°C ambient operating temperature

- Device HBM ESD classification level 2

- Device CDM ESD classification level C4B

- **Functional Safety Quality-Managed**

- Documentation available to aid ISO 26262 functional safety system design up to ASIL-B

- DMD display controller supporting:

- DLP5530S-Q1 automotive interior display chipset

- Video processing

- Scales input image to match DMD resolution

- Bezel adjustment up ±50% vertical image position and ±10% horizontal reducing the need for mechanical alignment (HUD)

- Support for pixel doubling or quadrupling to allow low resolution video input

- Gamma correction

- Embedded processor with error correction (ECC)

- On-chip diagnostic and self-test capability

- System diagnostics including temperature monitoring, device interface monitoring, and photodiode monitoring

- Integrated management of smooth dimming

- Configurable GPIO

- No external RAM required, internal SRAM for image processing

- 600-MHz sub-LVDS DMD interface for low power and emission

- Spread spectrum clocking for reduced EMI

- Video input interface

- Single OpenLDI (FPD-Link I) port up to 110 MHz

- 24-bit RGB parallel interface up to 110 MHz

- Configurable host control interface

- Serial peripheral interface (SPI) 10 MHz

- $I^2C (400 \text{ kHz})$

- Host IRQ signal to provide real-time feedback for critical system errors

- Interface to TPS99000S-Q1 system management and illumination controller

### 2 Applications

- Wide field of view and augmented reality head-up display (HUD)

- Digital cluster, navigation, and infotainment windshield displays

### 3 Description

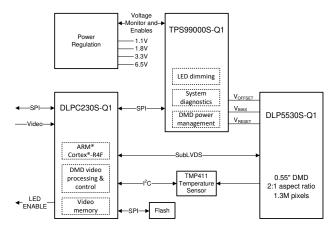

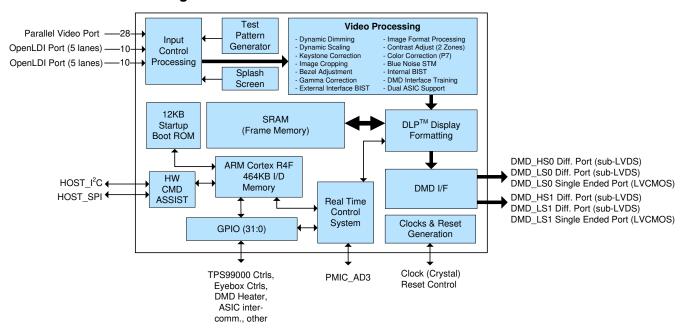

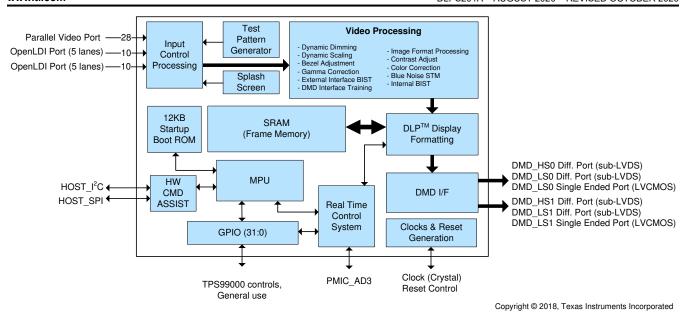

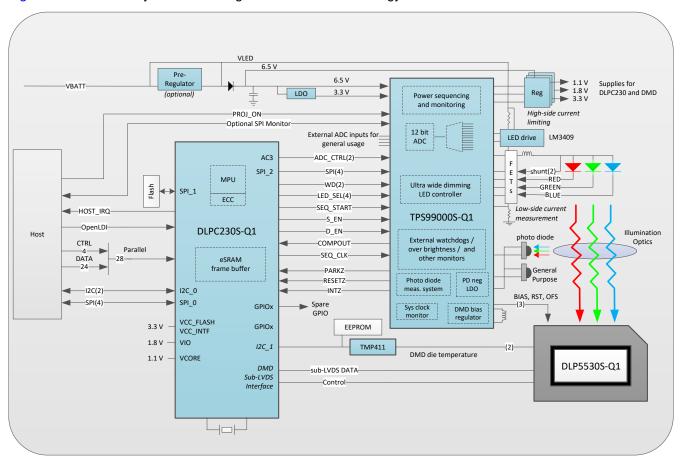

The DLPC230S-Q1 DMD Display Controller for automotive applications is part of the DLP5530S-Q1 chipset which is used for interior display applications with a functional safety requirement (such as augmented reality HUDs and windshield clusters). The chipset also includes a 0.55" DMD and the TPS99000S-Q1 System Management Illumination controller. The DLPC230S-Q1 integrates an embedded processor with error code correction (SECDED ECC), enabling host control and real-time feedback, on-chip diagnostics, and system monitoring functions. On-chip SRAM is included to remove the need for external DRAM. Combined with TPS99000S-Q1, the DLPC230S-Q1 supports high dynamic range dimming of over 5000:1 for HUD applications. Sub-LVDS 600-MHz DMD interface allows high DMD refresh rates to generate seamless and brilliant digital images, while simultaneously reducing radiated emissions.

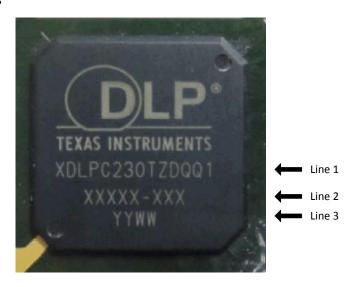

#### **Device Information**

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)     |

|-------------|------------------------|---------------------|

| DLPC230S-Q1 | BGA (324)              | 23.00 mm × 23.00 mm |

For all available packages, see the orderable addendum at the end of the data sheet.

DLP553x-Q1 TI DLP® Chipset System Block Diagram

### **Table of Contents**

| 1 Features                                           | 1                 | 6.17 Host/Diagnostic Port I <sup>2</sup> C Interface Timing      |    |

|------------------------------------------------------|-------------------|------------------------------------------------------------------|----|

| 2 Applications                                       | 1                 | Requirements                                                     |    |

| 3 Description                                        |                   | 6.18 Flash Interface Timing Requirements                         | 31 |

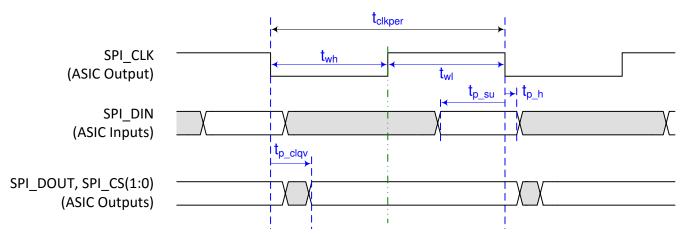

| 4 Revision History                                   | <mark>2</mark>    | 6.19 TPS99000S-Q1 SPI Interface Timing                           |    |

| 5 Pin Configuration and Functions                    | 3                 | Requirements                                                     | 33 |

| Pin Functions – Board Level Test, Debug, and         |                   | 6.20 TPS99000S-Q1 AD3 Interface Timing                           |    |

| Initialization                                       | 3                 | Requirements                                                     |    |

| Pin Functions – Parallel Port Input Data and Control | 6                 | 6.21 Master I <sup>2</sup> C Port Interface Timing Requirements. |    |

| Pin Functions – OpenLDI Ports Input Data and         |                   | 6.22 Chipset Component Usage Specification                       | 37 |

| Control                                              | 7                 | 7 Parameter Measurement Information                              | 38 |

| Pin Functions – DMD Reset and Bias Control           |                   | 7.1 HOST_IRQ Usage Model                                         |    |

| Interfaces                                           | 8                 | 7.2 Input Source                                                 | 38 |

| Pin Functions – DMD Sub-LVDS Interfaces              | 8                 | 8 Detailed Description                                           | 40 |

| Pin Functions – Peripheral Interfaces                | 10                | 8.1 Overview                                                     | 40 |

| Pin Functions – GPIO Peripheral Interface            | 12                | 8.2 Functional Block Diagram                                     | 40 |

| Pin Functions - Clock and PLL Support                |                   | 8.3 Feature Description                                          | 41 |

| Pin Functions – Power and Ground                     | 13                | 8.4 Device Functional Modes                                      | 54 |

| 6 Specifications                                     | 16                | 9 Application and Implementation                                 | 55 |

| 6.1 Absolute Maximum Ratings                         | 16                | 9.1 Application Information                                      | 55 |

| 6.2 ESD Ratings                                      |                   | 9.2 Typical Application                                          | 56 |

| 6.3 Recommended Operating Conditions                 | 17                | 10 Power Supply Recommendations                                  | 58 |

| 6.4 Thermal Information                              | 17                | 10.1 Power Supply Management                                     | 58 |

| 6.5 Electrical Characteristics                       | 18                | 10.2 Hot Plug Usage                                              | 58 |

| 6.6 Electrical Characteristics for Fixed Voltage I/O | 19                | 10.3 Power Supply Filtering                                      | 58 |

| 6.7 DMD High-Speed Sub-LVDS Electrical               |                   | 11 Layout                                                        | 60 |

| Characteristics                                      | 21                | 11.1 Layout Guidelines                                           | 60 |

| 6.8 DMD Low-Speed Sub-LVDS Electrical                |                   | 11.2 Thermal Considerations                                      | 68 |

| Characteristics                                      | 23                | 12 Device and Documentation Support                              | 69 |

| 6.9 OpenLDI LVDS Electrical Characteristics          | 24                | 12.1 Device Support                                              | 69 |

| 6.10 Power Dissipation Characterisics                | 24                | 12.2 Trademarks                                                  | 70 |

| 6.11 System Oscillators Timing Requirements          | 24                | 12.3 Electrostatic Discharge Caution                             | 70 |

| 6.12 Power Supply and Reset Timing Requirements      | 25                | 12.4 Glossary                                                    | 70 |

| 6.13 Parallel Interface General Timing Requirements  | 26                | 13 Mechanical, Packaging, and Orderable                          |    |

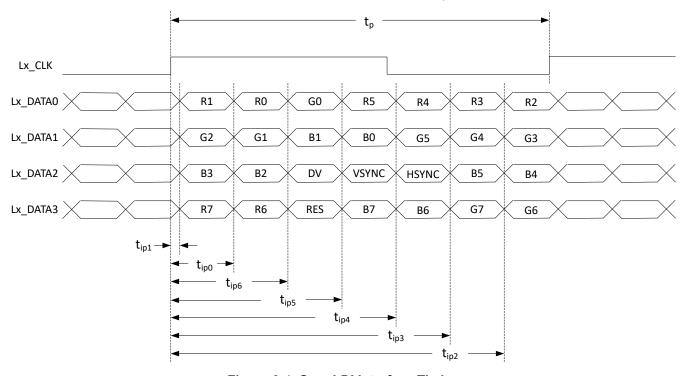

| 6.14 OpenLDI Interface General Timing Requirement    | s <mark>27</mark> | Information                                                      | 71 |

| 6.15 Parallel/OpenLDI Interface Frame Timing         |                   | 13.1 DLPC230S-Q1 Mechanical Data                                 | 72 |

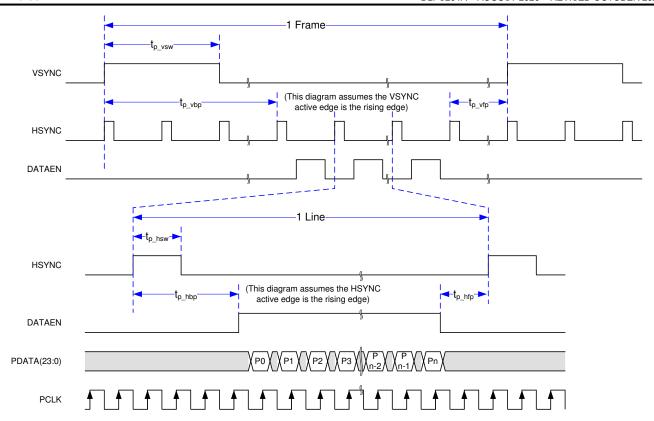

| Requirements                                         | 28                |                                                                  |    |

| 6.16 Host/Diagnostic Port SPI Interface Timing       |                   |                                                                  |    |

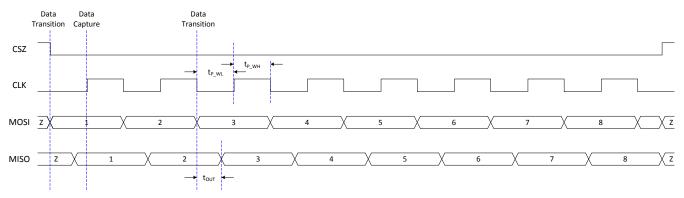

| Requirements                                         | 30                |                                                                  |    |

|                                                      |                   |                                                                  |    |

## **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| C | changes from Revision * (August 2020) to Revision A (October 2020) | Page |

|---|--------------------------------------------------------------------|------|

| • | Changed device status from Advance Information to Production Data  | 1    |

## **5 Pin Configuration and Functions**

|    | 1                 | 2                        | 3                        | 4                        | 5                        | 6                 | 7                        | 8                        | 9                | 10                       | 11                      | 12                | 13                       | 14                       | 15                       | 16                       | 17              | 18                       | 19                       | 20                       | 21                       | 22              |

|----|-------------------|--------------------------|--------------------------|--------------------------|--------------------------|-------------------|--------------------------|--------------------------|------------------|--------------------------|-------------------------|-------------------|--------------------------|--------------------------|--------------------------|--------------------------|-----------------|--------------------------|--------------------------|--------------------------|--------------------------|-----------------|

| А  | GND18A_<br>LVDS   | DMD_HS1<br>_WDATA0<br>_N | DMD_HS1<br>_WDATA1<br>_N | DMD_HS1<br>_WDATA2<br>_N | DMD_HS1<br>_WDATA3<br>_N | DMD_HS1<br>_CLK_N | DMD_HS1<br>_WDATA4<br>_N | DMD_HS1<br>_WDATA5<br>_N |                  | DMD_HS1<br>_WDATA7<br>_N | DMD_LS0<br>_WDATA_<br>N | DMD_LS0<br>_CLK_N | DMD_HS0<br>_WDATA7<br>_N | DMD_HS0<br>_WDATA6<br>_N | DMD_HS0<br>_WDATA5<br>_N | DMD_HS0<br>_WDATA4<br>_N |                 |                          | DMD_HS0<br>_WDATA2<br>_N | DMD_HS0<br>_WDATA1<br>_N | DMD_HS0<br>_WDATA0<br>_N | GND18A_<br>LVDS |

| В  | VCC18A_L<br>VDS   | DMD_HS1<br>_WDATA0<br>_P | DMD_HS1<br>_WDATA1<br>_P | DMD_HS1<br>_WDATA2<br>_P |                          | DMD_HS1<br>_CLK_P | DMD_HS1<br>_WDATA4<br>_P | DMD_HS1<br>_WDATA5<br>_P |                  | DMD_HS1<br>_WDATA7<br>_P | DMD_LS0<br>_WDATA_<br>P | DMD_LS0<br>_CLK_P | DMD_HS0<br>_WDATA7<br>_P | DMD_HS0<br>_WDATA6<br>_P | DMD_HS0<br>_WDATA5<br>_P | DMD_HS0<br>_WDATA4<br>_P |                 | DMD_HS0<br>_WDATA3<br>_P | DMD_HS0<br>_WDATA2<br>_P |                          | DMD_HS0<br>_WDATA0<br>_P | VCC18A_L<br>VDS |

| С  | VCC18A_L<br>VDS   | GND18A_<br>LVDS          | GND18A_<br>LVDS          | GND18A_<br>LVDS          | GND18A_<br>LVDS          | GND18A_<br>LVDS   | GND18A_<br>LVDS          | DMD_LS1<br>RDATA         | DMD_LS0<br>RDATA | DMD_LS0<br>WDATA         | DMD_LS0<br>CLK          | GND11AD<br>PLLD   | GND11AD<br>PLLM          | GNDIOLA<br>COSC          | VCC3IO_C                 | GND18A_<br>LVDS          | GND18A_<br>LVDS | GND18A_<br>LVDS          | GND18A_<br>LVDS          | GND18A_<br>LVDS          | GND18A_<br>LVDS          | VCC18A_L<br>VDS |

| D  | PMIC_SPI<br>DOUT  | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | RPI_1             | VCC18A_L<br>VDS          | GND18A_<br>LVDS          | RPI_LS           | VCC18IO                  | DMD_DE<br>N ARSTZ       | VCC11AD<br>PLLD   | VCC11AD<br>PLLM          | PLL_REFC<br>LK O         | PLL_REFC<br>LK I         | OSC_BYP<br>ASS           | RPI_0           | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | VCC18A_L<br>VDS          | GPIO_31         |

| Е  | PMIC_SPI<br>CLK   | PMIC_SPI<br>CSZ 0        | PMIC_PA<br>RKZ           | VCC11A_<br>DDI 1         |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCC11A_<br>DDI 0         | VCC18A_L<br>VDS          | GPIO_30                  | GPIO_29         |

| F  | PMIC_SPI<br>DIN   | PMIC_LED<br>SEL 0        | RESETZ                   | VCC11A_<br>DDI_1         |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCC11A_<br>DDI 0         | GPIO_28                  | GPIO_27                  | GPIO_26         |

| G  | PMIC_LED<br>SEL 1 | PMIC_LED<br>SEL 2        | PMIC_INT<br>Z            | VCCK                     |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCC3IO-2                 | JTAGTDO<br>3             | JTAGTMS<br>1             | JTAGTCK         |

| н  | PMIC_LED<br>SEL 3 | PMIC_AD<br>3 CLK         | HWTEST_<br>EN            | VCC3IO_<br>MVGP          |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCCK                     | JTAGTDO<br>2             | VSYNC                    | HSYNC           |

| J  | PMIC_AD<br>3 MOSI | PMIC_AD<br>3 MISO        | GPIO_00                  | VCC3IO                   |                          |                   |                          |                          | GND              | GND                      | VCCK                    | GND               | GND                      | GND                      |                          |                          |                 |                          | VCCK                     | JTAGTDO<br>1             | PDATA_2<br>3             | PDATA_2<br>2    |

| к  | GPIO_01           | GPIO_02                  | GPIO_03                  | VCC3IO                   |                          |                   |                          |                          | GND              | GND                      | GND                     | GND               | GND                      | GND                      |                          |                          |                 |                          | VCC3IO_I<br>NTF          | JTAGTDI                  | PDATA_2<br>1             | PDATA_2<br>0    |

| L  | GPIO_04           | GPIO_05                  | GPIO_06                  | VCCK                     |                          |                   |                          |                          | GND              | GND                      | GND                     | GND               | GND                      | GND                      |                          |                          |                 |                          | VCC3IO_I<br>NTF          | JTAGTRST<br>Z            | PDATA_1<br>9             | PDATA_1<br>8    |

| М  | GPIO_07           | GPIO_08                  | GPIO_09                  | VCC3IO                   |                          |                   |                          |                          | GND              | GND                      | GND                     | GND               | GND                      | GND                      |                          |                          |                 |                          | VCC3IO_I<br>NTF          | JTAGTMS<br>3             | PDATA_1<br>7             | PDATA_1<br>6    |

| N  | GPIO_10           | GPIO_11                  | GPIO_12                  | VCC3IO                   |                          |                   |                          |                          | GND              | GND                      | GND                     | GND               | GND                      | GND                      |                          |                          |                 |                          | VCCK                     | JTAGTMS<br>2             | PDATA_1<br>4             | PDATA_1<br>5    |

| Р  | GPIO_13           | GPIO_14                  | GPIO_15                  | VCC3IO                   |                          |                   |                          |                          | GND              | GND                      | GND                     | GND               | GND                      | GND                      |                          |                          |                 |                          | VCCK                     | HOST_IIC<br>SDA          | DATEN                    | PDATA_1<br>3    |

| R  | GPIO_16           | GPIO_17                  | GPIO_18                  | HOST_IF_<br>SEL          |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCC3IO_I<br>NTF          | HOST_IIC<br>_SCL         | PDATA_1<br>1             | PCLK            |

| Т  | GPIO_19           | GPIO_20                  | GPIO_21                  | VCCK                     |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCC3IO_I<br>NTF          | HOST_IR<br>Q             | PDATA_9                  | PDATA_1<br>2    |

| U  | GPIO_22           | GPIO_23                  | GPIO_24                  | VCCK                     |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCCK                     | HOST_SPI<br>DOUT         | PDATA_7                  | PDATA_1<br>0    |

| v  | HOST_SPI<br>_MODE | FLSH_SPI_<br>DIO_0       | GPIO_25                  | VCC3IO_F<br>LSH          |                          |                   |                          |                          |                  |                          |                         |                   |                          |                          |                          |                          |                 |                          | VCCK                     | HOST_SPI<br>_DIN         | PDATA_5                  | PDATA_8         |

| w  | FLSH_SPI_<br>CLK  | FLSH_SPI_<br>DIO_1       | FLSH_SPI_<br>DIO_3       | VCC3IO                   | VCC3IO                   | VCCK              | EFUSE_VD<br>DQ           | VCCK                     | VCC33A_L<br>VDS  | VCCK                     | VCC11A_L<br>VDS         | VCC11A_L<br>VDS   | VCC33A_L<br>VDS          | GND33A_<br>LVDS          | VCC33A_L<br>VDS          | VCCK                     | VCC11A_L<br>VDS | VCC11A_L<br>VDS          | VCC33A_L<br>VDS          | HOST_SPI<br>_CSZ         | PDATA_3                  | PDATA_6         |

| Y  | FLSH_SPI_<br>CSZ  | FLSH_SPI_<br>DIO_2       | GND                      | TSTPT_0                  | TSTPT_2                  | TSTPT_4           | TSTPT_6                  | EFUSE_PO<br>R33          | VCC33A_L<br>VDS  | GND11A_<br>LVDS          | GND11A_<br>LVDS         | GND11A_<br>LVDS   | VCC33A_L<br>VDS          | GND33A_<br>LVDS          | VCC33A_L<br>VDS          | GND11A_<br>LVDS          | GND11A_<br>LVDS | GND11A_<br>LVDS          | VCC33A_L<br>VDS          | HOST_SPI<br>_CLK         | PDATA_2                  | PDATA_4         |

| AA | GND               | GND                      | RTPPUB_<br>ENZ           | TSTPT_1                  | TSTPT_3                  | TSTPT_5           | TSTPT_7                  | GND33A_<br>LVDS          | L1_DATA0<br>_N   | L1_DATA1<br>_N           | L1_CLK_N                | L1_DATA2<br>_N    | L1_DATA3<br>_N           | GND33A_<br>LVDS          | L2_DATA0<br>_N           | L2_DATA1<br>_N           | L2_CLK_N        | L2_DATA2<br>_N           | L2_DATA3<br>_N           | GND33A_<br>LVDS          | PDATA_0                  | PDATA_1         |

| AB | GND               | GND                      | CRCZ_CH<br>KSM_SEL       | MSTR_SC<br>L             | MSTR_SD<br>A             | ETM_TRA<br>CECLK  | ETM_TRA<br>CECTL         | GND33A_<br>LVDS          | L1_DATA0<br>_P   | L1_DATA1<br>_P           | L1_CLK_P                | L1_DATA2<br>_P    | L1_DATA3<br>_P           | GND33A_<br>LVDS          | L2_DATA0<br>_P           | L2_DATA1<br>_P           | L2_CLK_P        | L2_DATA2<br>_P           | L2_DATA3<br>_P           | GND33A_<br>LVDS          | GND33A_<br>LVDS          | GND             |

Note that there is one VCCK power ball located in the thermal ball array.

Figure 5-1. ZDQ Package 324-Pin BGA Top View

### Pin Functions - Board Level Test, Debug, and Initialization

| PIN        | PIN    |                    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|------------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME       | NUMBER | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| RESETZ     | F3     | l <sub>7</sub>     | Active low power-on reset for the DLPC230S-Q1. A low-to-high transition starts self-configuration and initialization of the ASIC. ('0' = Reset, '1' = Normal Operation) All ASIC power and input clocks must be stable before this reset is de-asserted high. The signals listed below should be forced low by external pull-down, and will then be driven low as the power supplies stabilize with RESETZ asserted.  PMIC_LEDSEL_0, PMIC_LEDSEL_1, PMIC_LEDSEL_2, PMIC_LEDSEL_3, DMD_DEN_ARSTZ, PMIC_AD3_CLK, and PMIC_AD3_MOSI All other bi-directional and output signals will be tri-stated while reset is asserted. External pull-ups or pull-downs must be added where necessary to protect external devices that would typically be driven by the ASIC to prevent device malfunction. This pin includes hysteresis. Specific timing requirements for this signal are shown in Section 6.12. |  |  |

| PMIC_PARKZ | E3     | I <sub>7</sub>     | DMD Park Control ('0' = Park, '1' = Un-Park) The TI TPS99000S-Q1 device is used to control this signal. As part of this function, it monitors power to the DLPC230S-Q1 watching for an imminent power loss condition, upon which it will drive the PMIC_PARKZ signal accordingly. The specific timing requirements for this signal are shown in Section 6.12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| PIN             |             | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|-----------------|-------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME            | NAME NUMBER |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| HOST_IF_SEL     | R4          | B <sub>13,14</sub> | Selects which input interface port will be used for Host Command and Control. The port that is not selected as the Host Command and Control port will be available as a Diagnostic Processor monitoring port. ('0' = Host SPI, '1' = Host I^2C) This pin includes a weak internal pull-down. If a pull-up is used to obtain a '1' value, the pull-up value must be $\leq 8~k\Omega$ . Tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 $\mu s$ after RESETZ is de-asserted. It may be driven as an output for TI debug use after sampling.                                                                     |  |  |

| HOST_SPI_MODE   | V1          | B <sub>13,14</sub> | Selects the SPI mode (clock phase and polarity) that will be used with the HOST SPI interface. This value is applicable regardless of whether the Host SPI interface is used for Host Command and Control, or for the Diagnostic Processor monitoring port. ('0' = SPI Mode 0 or 3, '1' = SPI Mode 1 or 2) This pin includes a weak internal pull-down. If a pull-up is used to obtain a '1' value, the pull-up value must be $\leq 8~\mathrm{k}\Omega$ . Tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 $\mu$ s after RESETZ is de-asserted. It may be driven as an output for TI debug use after sampling. |  |  |

| RTPPUB_ENZ      | AA3         | B <sub>13,14</sub> | TI internal use. Must be left unconnected. Includes a weak pull-down.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| CRCZ_CHKSUM_SEL | AB3         | B <sub>13,14</sub> | Selects whether the Host will use 8-bit CRC or Checksum on the Host Command and Control interface. This value is only applicable for the Host Command and Control interface. The value for the Diagnostic Processor monitoring port will be specified in Flash. ('0' = 8-bit CRC, '1' = 8-bit Checksum) This pin includes a weak internal pull-down. If a pull-up is used to obtain a '1' value, the pull-up value must be $\leq 8~k\Omega$ . Tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 $\mu s$ after RESETZ is de-asserted. It may be driven as an output for TI debug use after sampling.             |  |  |

| ETM_TRACECLK    | AB6         | O <sub>13</sub>    | TI internal use. Must be left unconnected. (Clock for Trace Debug)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| ETM_TRACECTL    | AB7         | O <sub>13</sub>    | TI internal use. Must be left unconnected. (Control for Trace Debug)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| TSTPT_0         | Y4          | B <sub>13,14</sub> | Test pin 0 / STAY-IN-BOOT: Selects whether the system should stay in the Boot Application, or proceed with the normal load of the Main Application. ('0' = Load Main Application, '1' = Stay in Boot Application) This pin includes a weak internal pull-down. If a pull-up is being used to obtain a '1' value, the pull-up value must be $\leq 8~k\Omega$ . Tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 $\mu s$ after RESETZ is de-asserted. It may be driven as an output for debug use after sampling as described in Section 8.3.11.                                                                 |  |  |

| TSTPT_1         | AA4         | B <sub>13,14</sub> | Test pin 1 : This pin must be externally pulled down, left open or unconnected. Includes a weak pull-down. It may be driven as an output for debug use as described in Section 8.3.11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TSTPT_2         | Y5          | B <sub>13,14</sub> | Test pin 2 : This pin must be externally pulled down, left open or unconnected. Includes a weak pull-down. It may be driven as an output for debug use as described in Section 8.3.11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TSTPT_3         | AA5         | B <sub>13,14</sub> | Test pin 3 : This pin must be externally pulled down, left open or unconnected. Includes a weak pull-down. It may be driven as an output for debug use as described in Section 8.3.11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| TSTPT_4         | Y6          | B <sub>13,14</sub> | Test pin 4: This pin must be externally pulled down, left open or unconnected. Includes a weak pull-down. It may be driven as an output for debug use as described in Section 8.3.11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PIN NAME NUMBER |     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------|-----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 |     | 1/0(-/             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| TSTPT_5         | AA6 | B <sub>13,14</sub> | Test pin 5 / Spread Spectrum Disable: Selects whether spread spectrum flash settings are used or whether spread spectrum clocking will be disabled. ('0' = Spread Spectrum Disabled, '1' = Use flash Spread Spectrum settings) This pin includes a weak internal pull-down. If a pull-up is being used to obtain a '1' value, the pull-up value must be $\leq 8~\rm k\Omega$ . This signal is tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 $\mu s$ after RESETZ is de-asserted. It may be driven as an output for debug use after sampling as described in Section 8.3.11. |  |

| TSTPT_6         | Y7  | B <sub>13,14</sub> | Test pin 6: An external pull-up resistor must be used (≤ 8 kΩ since pin includes a weak pull-down). This signal is tri-stated while RESETZ is asserted low, and is sampled as a host directive approximately 1.5 μs after RESETZ is de-asserted. It may be driven as an output for debug use after sampling as described in Section 8.3.11.                                                                                                                                                                                                                                                                                 |  |

| TSTPT_7         | AA7 | B <sub>13,14</sub> | Test pin 7: This pin must be externally pulled down, left open or unconnected. Includes a weak pull-down. It may be driven as an output for debug use as described in Section 8.3.11.                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| HWTEST_EN       | НЗ  | I <sub>14</sub>    | Manufacturing test enable signal. This signal must be connected directly to ground on the PCB. Includes weak internal pull-down and hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| JTAGTCK         | G22 | I <sub>11</sub>    | JTAG Serial Data Clock<br>Includes a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| JTAGTMS1        | G21 | I <sub>11</sub>    | JTAG Test Mode Select<br>Includes weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| JTAGTRSTZ       | L20 | I <sub>11</sub>    | JTAG Reset Includes a weak internal pull-up and Hysteresis. For normal operation, this pin must be pulled to ground through an external 8 k $\Omega$ or less resistor. Failure to pull this pin low during normal operation will cause start-up and initialization problems. For JTAG Boundary Scan, this pin must be pulled-up or left disconnected.                                                                                                                                                                                                                                                                       |  |

| JTAGTDI         | K20 | I <sub>11</sub>    | JTAG Serial Data In Includes a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| JTAGTDO1        | J20 | B <sub>10,11</sub> | JTAG Serial Data Out<br>Includes weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| JTAGTDO2        | H20 | B <sub>10,11</sub> | This pin must be left open or unconnected. Includes a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| JTAGTDO3        | G20 | B <sub>10,11</sub> | This pin must be left open or unconnected. Includes a weak internal pull-up.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| JTAGTMS2        | N20 | I <sub>11</sub>    | This pin must be left open or unconnected. Includes a weak internal pull-up. See Section 8.3.11 for important debug access considerations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| JTAGTMS3        | M20 | I <sub>11</sub>    | This pin must be left open or unconnected. Includes a weak internal pull-up. See Section 8.3.11 for important debug access considerations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

<sup>(1)</sup> See Table 5-1 for more information on I/O definitions.

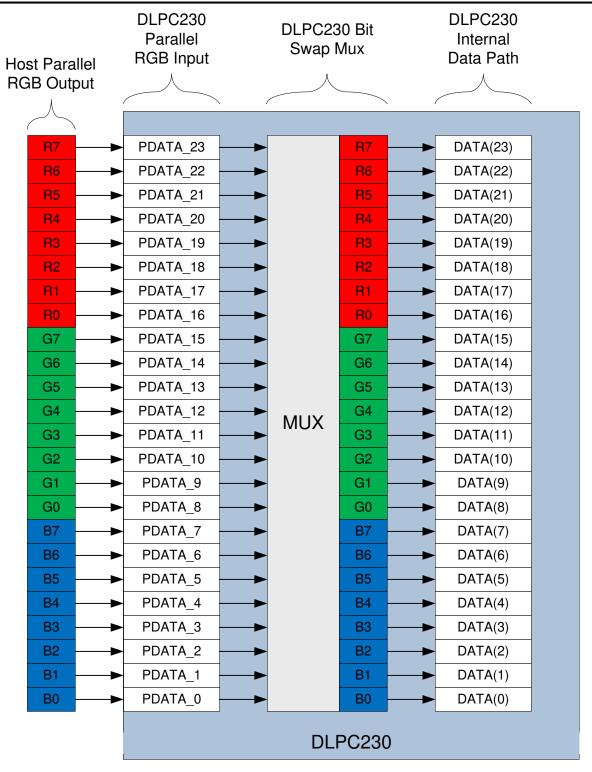

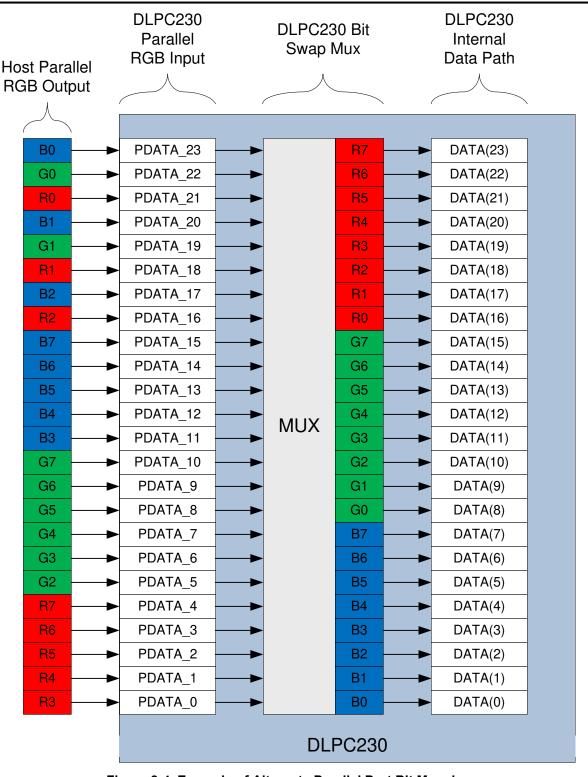

## Pin Functions – Parallel Port Input Data and Control

| PIN <sup>(1)</sup>                                                                                       |                                                        | I/O <sup>(2)</sup> | DESCRIPTION                                                                                                                                                                  |  |  |

|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                                                                                                     | NUMBER                                                 | 1/0(-/             | PARALLEL RGB MODE                                                                                                                                                            |  |  |

| PCLK                                                                                                     | R22                                                    | I <sub>11</sub>    | Pixel clock                                                                                                                                                                  |  |  |

| VSYNC                                                                                                    | H21                                                    | I <sub>11</sub>    | Vsync <sup>(3)</sup>                                                                                                                                                         |  |  |

| HSYNC                                                                                                    | H22                                                    | I <sub>11</sub>    | Hsync <sup>(3)</sup>                                                                                                                                                         |  |  |

| DATEN                                                                                                    | P21                                                    | I <sub>11</sub>    | Data Valid                                                                                                                                                                   |  |  |

|                                                                                                          |                                                        |                    | (TYPICAL RGB 888)                                                                                                                                                            |  |  |

| PDATA_0<br>PDATA_1<br>PDATA_2<br>PDATA_3<br>PDATA_4<br>PDATA_5<br>PDATA_6<br>PDATA_7                     | AA21<br>AA22<br>Y21<br>W21<br>Y22<br>V21<br>W22<br>U21 | I <sub>11</sub>    | Blue (bit weight 1) Blue (bit weight 2) Blue (bit weight 4) Blue (bit weight 8) Blue (bit weight 16) Blue (bit weight 32) Blue (bit weight 64) Blue (bit weight 128)         |  |  |

|                                                                                                          |                                                        |                    | (TYPICAL RGB 888)                                                                                                                                                            |  |  |

| PDATA_8 PDATA_9 PDATA_10 PDATA_11 PDATA_12 PDATA_13 PDATA_14 PDATA_15                                    | V22<br>T21<br>U22<br>R21<br>T22<br>P22<br>N21<br>N22   | I <sub>11</sub>    | Green (bit weight 1) Green (bit weight 2) Green (bit weight 4) Green (bit weight 8) Green (bit weight 16) Green (bit weight 32) Green (bit weight 64) Green (bit weight 128) |  |  |

|                                                                                                          |                                                        |                    | (TYPICAL RGB 888)                                                                                                                                                            |  |  |

| PDATA_16<br>PDATA_17<br>PDATA_18<br>PDATA_19<br>PDATA_20<br>PDATA_21<br>PDATA_21<br>PDATA_22<br>PDATA_23 | M22<br>M21<br>L22<br>L21<br>K22<br>K21<br>J22<br>J21   | I <sub>11</sub>    | Red (bit weight 1) Red (bit weight 2) Red (bit weight 4) Red (bit weight 8) Red (bit weight 16) Red (bit weight 32) Red (bit weight 64) Red (bit weight 128)                 |  |  |

<sup>(1)</sup> Unused inputs should be grounded or pulled down to ground through an external resistor ( $\leq$  10 k $\Omega$ ).

<sup>(2)</sup> See Table 5-1 for more information on I/O definitions.

<sup>(3)</sup> VSYNC and HSYNC polarity are software programmable.

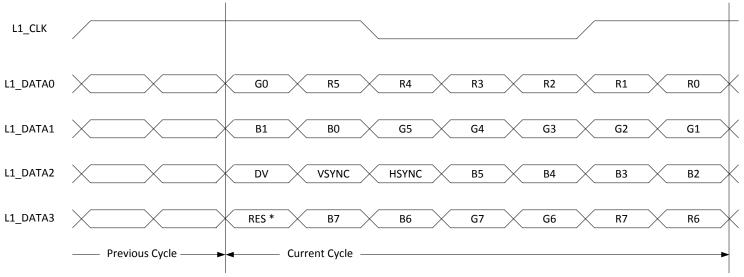

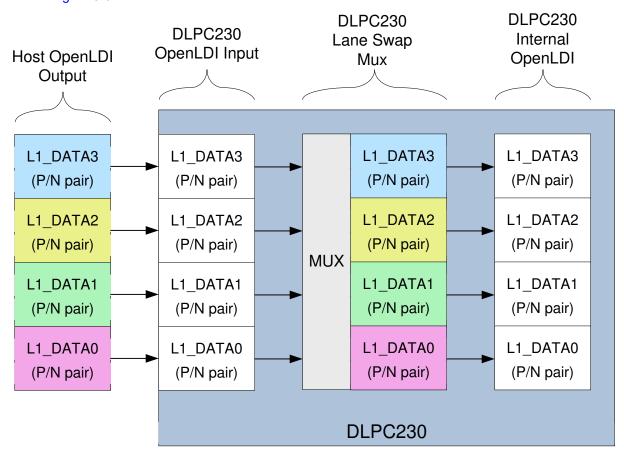

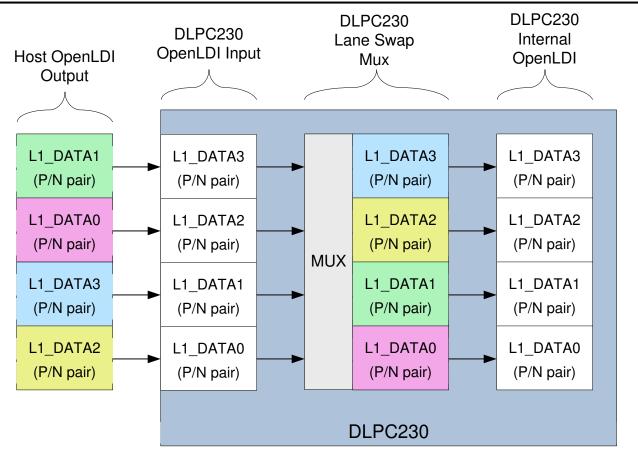

## Pin Functions - OpenLDI Ports Input Data and Control

| PIN <sup>(1) (2)</sup>                                                                  |                                                              | I/O <sup>(3)</sup> | DESCRIPTION                                                                                                                                         |  |

|-----------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                                                                                    | NUMBER                                                       |                    | DESCRIPTION                                                                                                                                         |  |

| L1_CLK_P<br>L1_CLK_N                                                                    | AB11<br>AA11                                                 | I <sub>18</sub>    | OpenLDI (FPD Link I) Port 1 Clock Lane                                                                                                              |  |

| L1_DATA0_P L1_DATA0_N L1_DATA1_P L1_DATA1_N L1_DATA2_P L1_DATA2_N L1_DATA3_P L1_DATA3_N | AB9<br>AA9<br>AB10<br>AA10<br>AB12<br>AA12<br>AB13<br>AA13   | I <sub>18</sub>    | OpenLDI (FPD Link I) Port 1 Data Lanes: Intra-port data lane swapping can be done on a product configuration basis to support board considerations. |  |

| L2_CLK_P<br>L2_CLK_N                                                                    | AB17<br>AA17                                                 | I <sub>18</sub>    | OpenLDI (FPD Link I) Port 2 Clock Lane                                                                                                              |  |

| L2_DATA0_P L2_DATA0_N L2_DATA1_P L2_DATA1_N L2_DATA2_P L2_DATA2_N L2_DATA3_P L2_DATA3_N | AB15<br>AA15<br>AB16<br>AA16<br>AB18<br>AA18<br>AB19<br>AA19 | I <sub>18</sub>    | OpenLDI (FPD Link I) Port 2 Data Lanes: Intra-port data lane swapping can be done on a product configuration basis to support board considerations. |  |

<sup>(1)</sup> The system only supports the operational use of one port. As two ports are available, the host can select which port they wish to be active (to optimize board routing as an example).

<sup>(2)</sup> The inputs for any un-used port(s) should be left unconnected, and will be powered down by the system.

<sup>(3)</sup> See Table 5-1 for more information on I/O definitions.

### Pin Functions - DMD Reset and Bias Control Interfaces

| PIN <sup>(1)</sup> <sup>(2)</sup>  |            | I/O <sup>(3)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|------------------------------------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME                               | NUMBER     | 1/0(4)             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| DMD_DEN_ARSTZ                      | D11        | O <sub>1</sub>     | DMD driver enable signal ('1' = Enabled, '0' = Reset) This signal will be driven low after the DMD is parked and before power is removed from the DMD. If the 1.8-V power to the DLPC230S-Q1 is independent of the 1.8-V power to the DMD, then an external pull-down resistor ( $\leq$ 2.2 k $\Omega$ ) must be used to hold the signal low in the event DLPC230S-Q1 power is inactive while DMD power is applied. |  |

| DMD_LS0_CLK                        | C11        | O <sub>2</sub>     | TI internal use. Must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_LS0_WDATA                      | C10        | O <sub>2</sub>     | TI internal use. Must be left unconnected.                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_LS0_RDATA                      | C9         | l <sub>3</sub>     | DMD, low-speed single-ended serial read data                                                                                                                                                                                                                                                                                                                                                                        |  |

| DMD_LS1_RDATA                      | C8         | l <sub>3</sub>     | DMD, low-speed single-ended serial read data (Training data response for second port of DMD)                                                                                                                                                                                                                                                                                                                        |  |

| DMD_LS0_CLK_P<br>DMD_LS0_CLK_N     | B12<br>A12 | O <sub>4</sub>     | DMD low-speed differential interface clock                                                                                                                                                                                                                                                                                                                                                                          |  |

| DMD_LS0_WDATA_P<br>DMD_LS0_WDATA_N | B11<br>A11 | O <sub>4</sub>     | DMD low-speed differential interface write data                                                                                                                                                                                                                                                                                                                                                                     |  |

- (1) The low-speed write control interface to the DMD is differential.

- (2) All control interface reads will make use of the single-ended low-speed signals. The read data will be clocked by the write clock .

- (3) See Table 5-1 for more information on I/O definitions.

### Pin Functions - DMD Sub-LVDS Interfaces

| PIN                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME                                                                                                                                                                                                                                                                                                                                                                 | NUMBER                                                                                                       | 1/0(1)             | DESCRIPTION                                                                                                                                                                         |

| DMD_HS0_CLK_P<br>DMD_HS0_CLK_N                                                                                                                                                                                                                                                                                                                                       | B17<br>A17                                                                                                   | O <sub>4</sub>     | DMD high-speed interface, Port 0 Clock Lane.                                                                                                                                        |

| DMD_HS0_WDATA0_P DMD_HS0_WDATA1_P DMD_HS0_WDATA1_P DMD_HS0_WDATA1_N DMD_HS0_WDATA2_P DMD_HS0_WDATA2_N DMD_HS0_WDATA3_P DMD_HS0_WDATA3_P DMD_HS0_WDATA4_P DMD_HS0_WDATA4_P DMD_HS0_WDATA4_P DMD_HS0_WDATA4_N DMD_HS0_WDATA5_P DMD_HS0_WDATA5_N DMD_HS0_WDATA6_P DMD_HS0_WDATA6_P DMD_HS0_WDATA6_P DMD_HS0_WDATA6_N DMD_HS0_WDATA7_P DMD_HS0_WDATA7_P DMD_HS0_WDATA7_N | B21<br>A21<br>B20<br>A20<br>B19<br>A19<br>B18<br>A18<br>B16<br>A16<br>B15<br>A16<br>B15<br>A15<br>B14<br>A14 | O <sub>4</sub>     | DMD high-speed interface, Port 0 Data Lanes: The true numbering and application of the DMD_HS_DATA pins are software configuration dependent as discussed in <i>Section 8.3.3</i> . |

| DMD_HS1_CLK_P<br>DMD_HS1_CLK_N                                                                                                                                                                                                                                                                                                                                       | B6<br>A6                                                                                                     | O <sub>4</sub>     | DMD high-speed interface, Port 1 Clock Lane.                                                                                                                                        |

Product Folder Links: DLPC230S-Q1

www.ti.com

| PIN                                                                                                   |                                    | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                 |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                                                                                                  | NUMBER                             |                    | DESCRIPTION                                                                                                                                                                 |  |  |  |

| DMD_HS1_WDATA0_P DMD_HS1_WDATA0_N DMD_HS1_WDATA1_P DMD_HS1_WDATA1_N DMD_HS1_WDATA2_P                  | B2<br>A2<br>B3<br>A3<br>B4         |                    |                                                                                                                                                                             |  |  |  |

| DMD_HS1_WDATA2_N<br>DMD_HS1_WDATA3_P<br>DMD_HS1_WDATA3_N<br>DMD_HS1_WDATA4_P<br>DMD_HS1_WDATA4_N      | A4<br>B5<br>A5<br>B7<br>A7         | O <sub>4</sub>     | DMD high-speed interface, Port 1 Data Lanes: The true numbering and application of the DMD_HS_DATA pins are software configuration dependent as discussed in Section 8.3.3. |  |  |  |

| DMD_HS1_WDATA5_P DMD_HS1_WDATA5_N DMD_HS1_WDATA6_P DMD_HS1_WDATA6_N DMD_HS1_WDATA7_P DMD_HS1_WDATA7_N | B8<br>A8<br>B9<br>A9<br>B10<br>A10 |                    |                                                                                                                                                                             |  |  |  |

<sup>(1)</sup> See Table 5-1 for more information on I/O definitions.

## Pin Functions - Peripheral Interfaces

| PIN                      |        | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------------------------|--------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME                     | NUMBER | 1/0                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                         |  |  |

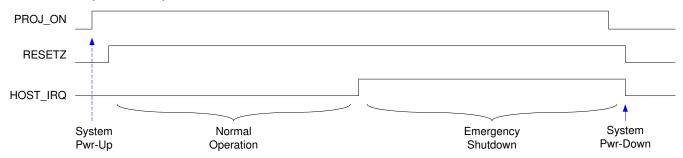

| HOST_IRQ <sup>(2)</sup>  | T20    | O <sub>10</sub>    | Host interrupt (output active HIGH) This signal is used to indicate that the DLPC230S-Q1 has detected a serious error for which the ASIC has initiated an Emergency Shutdown. This is discussed further in Section 7.1. The DLPC230S-Q1 tri-states this output during reset. An external pull-down ( $\leq$ 10 k $\Omega$ ) is required to drive this signal to its inactive state. |  |  |

| HOST_IIC_SCL             | R20    | B <sub>12</sub>    | I <sup>2</sup> C Port (Slave), Host Command and Control to ASIC, SCL (bidirectional, open-drain): An external pull-up is required.                                                                                                                                                                                                                                                  |  |  |

| HOST_IIC_SDA             | P20    | B <sub>12</sub>    | I <sup>2</sup> C Port (Slave), Host Command and Control to ASIC, SDA. (bidirectional, open-drain): An external pull-up is required.                                                                                                                                                                                                                                                 |  |  |

| HOST_SPI_CLK             | Y20    | I <sub>11</sub>    | SPI Port (Slave), Host Command and Control to ASIC, clock                                                                                                                                                                                                                                                                                                                           |  |  |

| HOST_SPI_CSZ             | W20    | I <sub>11</sub>    | SPI Port (Slave), Host Command and Control to ASIC, chip select (active low input) An external pull-up resistor (≤ 2.2 kΩ) is required to avoid a floating chip select input to the ASIC                                                                                                                                                                                            |  |  |

| HOST_SPI_DIN             | V20    | I <sub>11</sub>    | SPI Port (Slave), Host Command and Control to ASIC, receive data in                                                                                                                                                                                                                                                                                                                 |  |  |

| HOST_SPI_DOUT            | U20    | O <sub>10</sub>    | SPI Port (Slave), Host Command and Control to ASIC, transmit data out                                                                                                                                                                                                                                                                                                               |  |  |

| FLSH_SPI_CSZ             | Y1     | O <sub>8</sub>     | SPI Port (Master), Control Interface to Flash device, chip select (active low output) An external pullup resistor (≤ 10 kΩ) is required to avoid a floating chip select input to the Flash                                                                                                                                                                                          |  |  |

| FLSH_SPI_CLK             | W1     | O <sub>8</sub>     | SPI Port (Master), Control Interface to Flash device, clock                                                                                                                                                                                                                                                                                                                         |  |  |

| FLSH_SPI_DIO_0           | V2     | B <sub>8,9</sub>   | SPI Port (Master), Control Interface to Flash device, transmit and receive data An external pullup resistor (≤ 10 kΩ) is required                                                                                                                                                                                                                                                   |  |  |

| FLSH_SPI_DIO_1           | W2     | B <sub>8,9</sub>   | SPI Port (Master), Control Interface to Flash device, transmit and receive data An external pullup resistor (≤ 10 kΩ) is required                                                                                                                                                                                                                                                   |  |  |

| FLSH_SPI_DIO_2           | Y2     | B <sub>8,9</sub>   | SPI Port (Master), Control Interface to Flash device, transmit and receive data An external pullup resistor ( $\leq 3.3~\text{k}\Omega$ ) is required                                                                                                                                                                                                                               |  |  |

| FLSH_SPI_DIO_3           | W3     | B <sub>8,9</sub>   | SPI Port (Master), Control Interface to Flash device, transmit and receive data An external pullup resistor ( $\leq 3.3~\text{k}\Omega$ ) is required                                                                                                                                                                                                                               |  |  |

| PMIC_INTZ <sup>(2)</sup> | G3     | I <sub>7</sub>     | TPS99000S-Q1 interrupt (input with hysteresis) The ASIC provides a weak internal pull-up                                                                                                                                                                                                                                                                                            |  |  |

| PMIC_SPI_CLK             | E1     | O <sub>6</sub>     | SPI Port (Master), General Control Interface to TPS99000S-Q1, clock                                                                                                                                                                                                                                                                                                                 |  |  |

| PMIC_SPI_CSZ0            | E2     | O <sub>6</sub>     | SPI Port (Master), General Control Interface to TPS99000S-Q1, chip select 0 (active low output) An external pullup resistor (≤ 10 kΩ) must be used to avoid floating chip select inputs to the external SPI device during ASIC reset assertion.                                                                                                                                     |  |  |

| PMIC_SPI_DIN             | F1     | I <sub>7</sub>     | SPI Port (Master), General Control Interface to TPS99000S-Q1, receive data in                                                                                                                                                                                                                                                                                                       |  |  |

| PMIC_SPI_DOUT            | D1     | O <sub>6</sub>     | SPI Port (Master), General Control Interface to TPS99000S-Q1, transmit data out                                                                                                                                                                                                                                                                                                     |  |  |

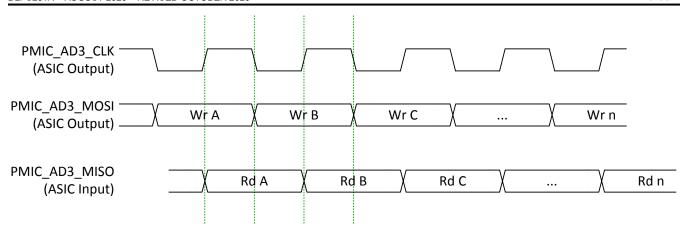

| PMIC_AD3_CLK             | H2     | O <sub>20</sub>    | Sequencer Clock / TPS99000S-Q1 primary system clock An external pull-down resistor ( $\leq$ 10 k $\Omega$ ) must be used to avoid uncontrolled behavior during ASIC reset assertion.                                                                                                                                                                                                |  |  |

| PMIC_AD3_MISO            | J2     | I <sub>14</sub>    | Measurement control interface to TPS99000S-Q1, receive data in                                                                                                                                                                                                                                                                                                                      |  |  |

| PMIC_AD3_MOSI            | J1     | O <sub>20</sub>    | Measurement control interface to TPS99000S-Q1, transmit data out An external pull-down resistor ( $\leq$ 10 k $\Omega$ ) must be used to avoid uncontrolled behavior during ASIC reset assertion.                                                                                                                                                                                   |  |  |

| PMIC_LEDSEL_0            | F2     | O <sub>6</sub>     | LED Control Interface to TPS99000S-Q1 An external pull-down resistor ( $\leq$ 10 k $\Omega$ ) must be used to avoid uncontrolled illumination during ASIC reset assertion.                                                                                                                                                                                                          |  |  |

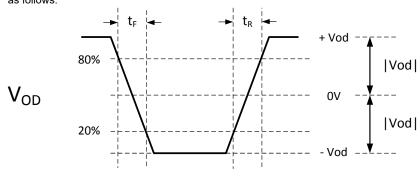

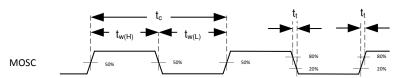

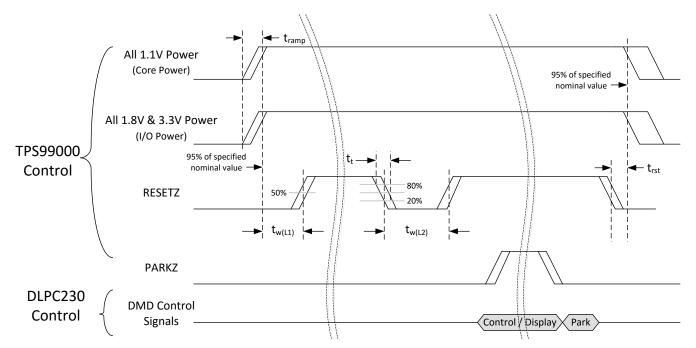

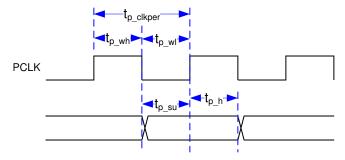

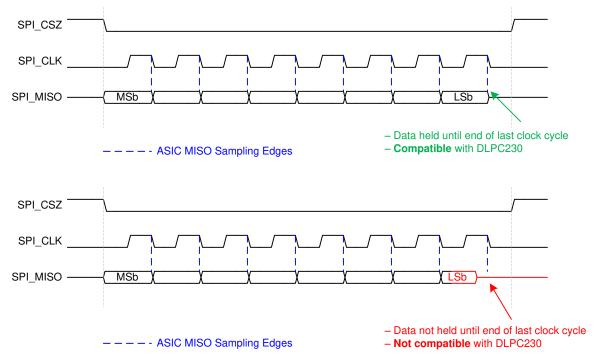

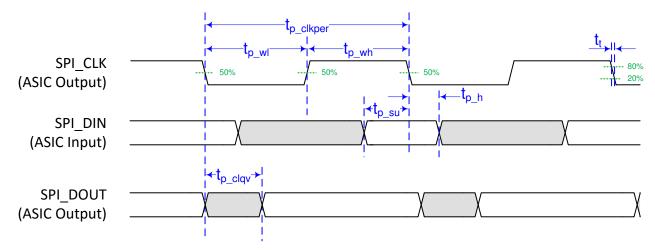

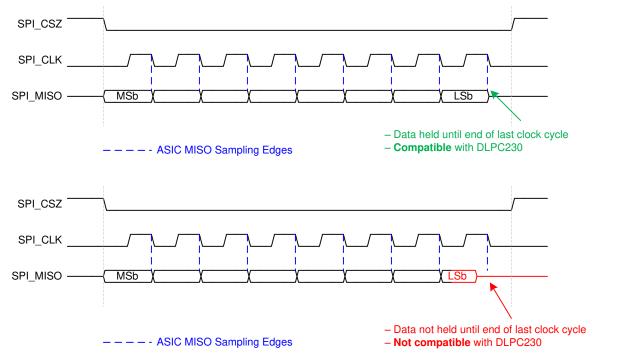

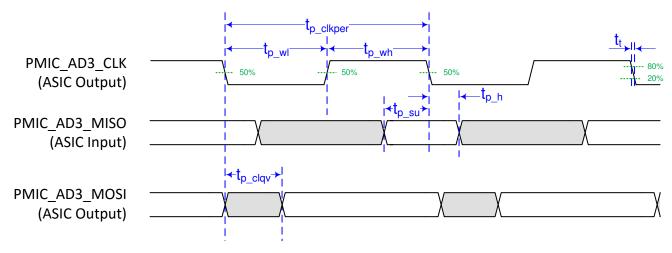

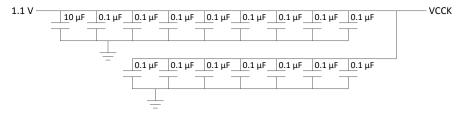

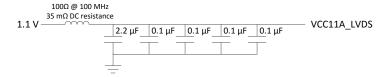

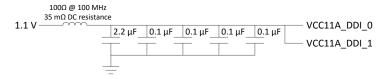

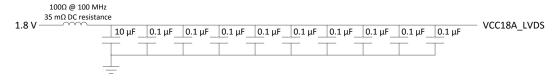

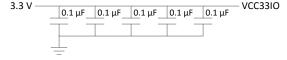

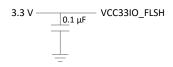

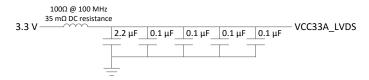

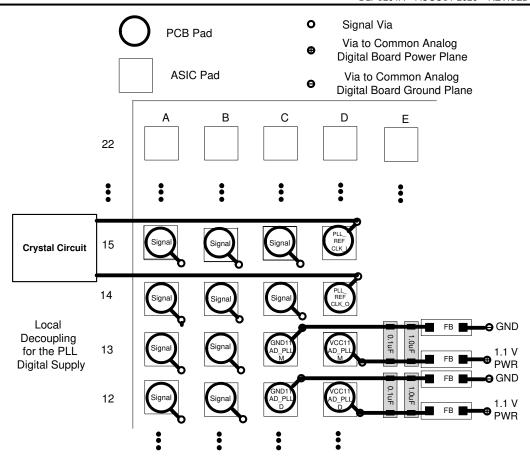

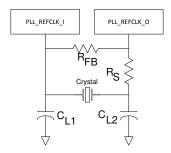

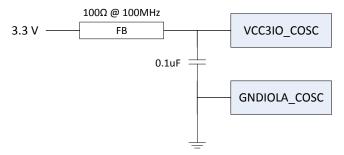

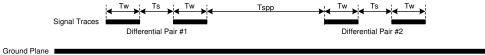

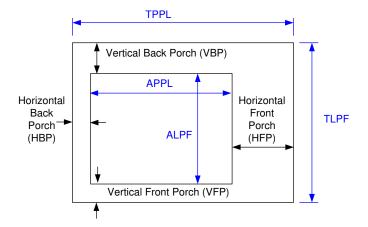

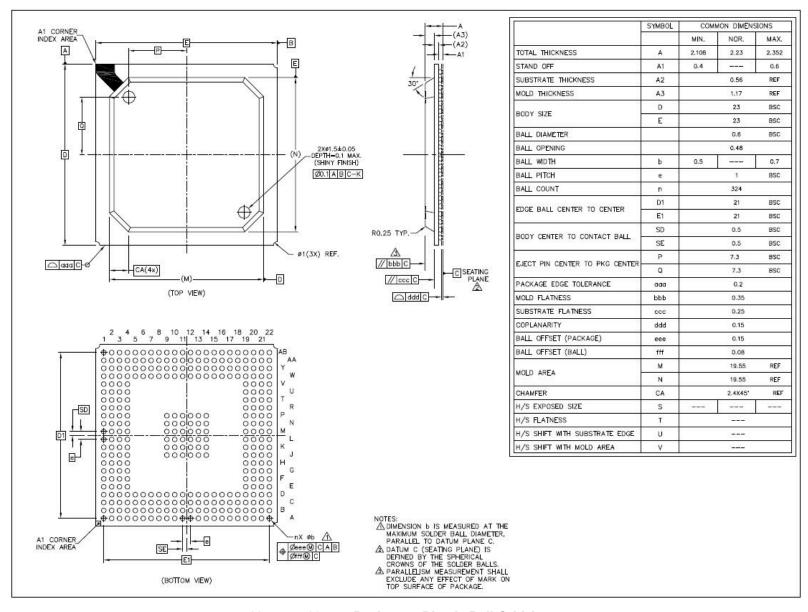

| PMIC_LEDSEL_1            | G1     | O <sub>6</sub>     | LED Control Interface to TPS99000S-Q1 An external pull-down resistor ( $\leq$ 10 k $\Omega$ ) must be used to avoid uncontrolled illumination during ASIC reset assertion.                                                                                                                                                                                                          |  |  |