# LM3533 用于智能手机的完整照明电源解决方案

## 1 特性

- 驱动两个并联高电压发光二极管 (LED) 灯串为显示屏和键盘提供照明

- 能够支持高达 40V 输出电压的高压灯串，并且效率高达 90%

- 每灌电流高达 30mA (背光和指示灯)

- 采用 8 位可编程背光代码实现 14 位指数调光

- 可选择带有 128 个可编程增益设置电阻的模拟环境光传感器 (ALS) 输入或者带有内部低通滤波器的脉宽调制 (PWM) ALS 输入

- 针对内容可调亮度控制的 PWM 输入

- 五个用于指示器 LED 的低压电流阱

- 用于提高效率和  $V_{IN}$  工作范围的集成电荷泵

- 内部图案生成引擎

- 完全可编程 LED 分组和控制

- 4 个可配置过压保护阈值 (16V, 24V, 32V 和 40V)

- 500kHz 和 1MHz 可编程开关频率

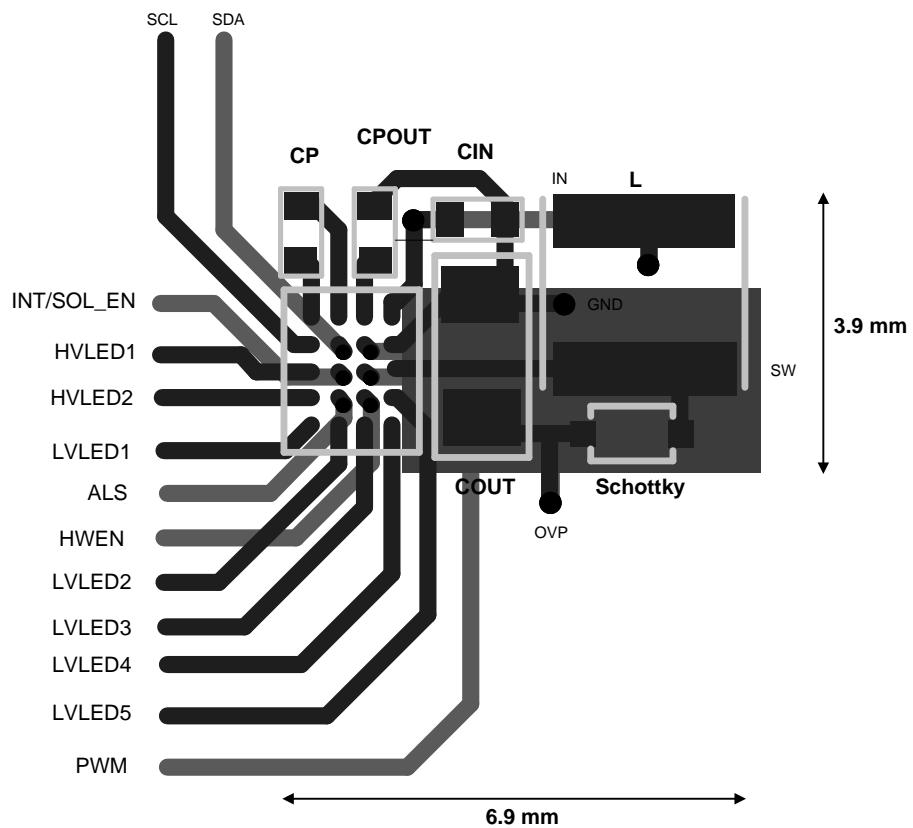

- 27mm<sup>2</sup> 总体解决方案尺寸

## 2 应用范围

- 用于智能手机照明的电源

- 显示器、键区和指示器照明

- RGB 指示器驱动器

## 3 说明

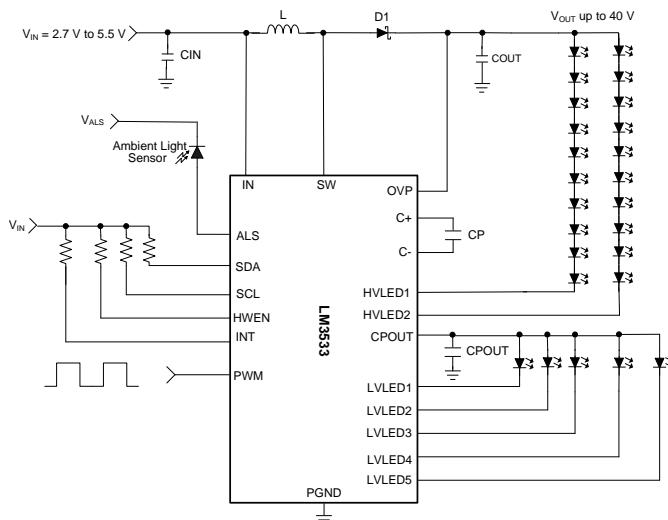

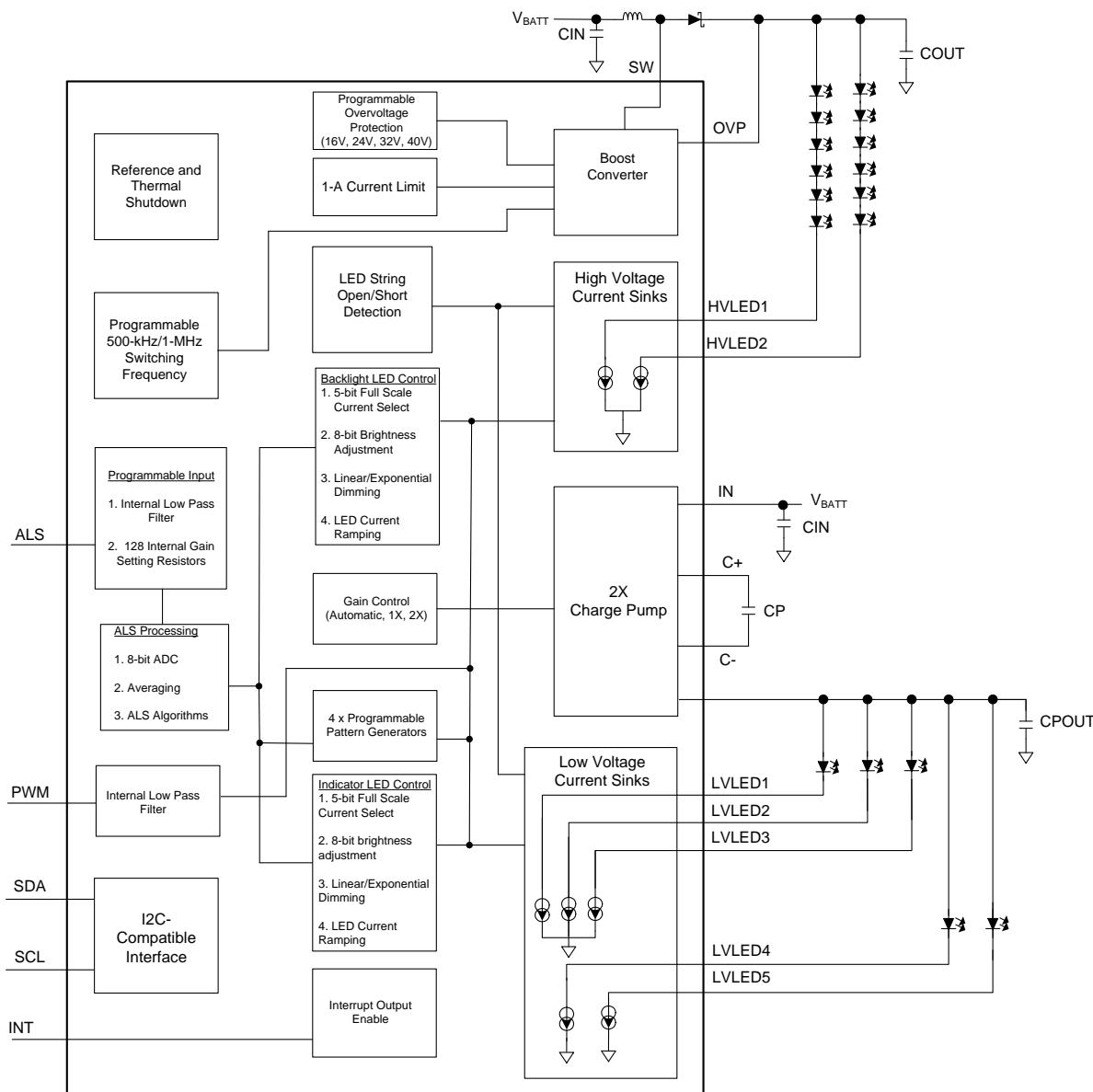

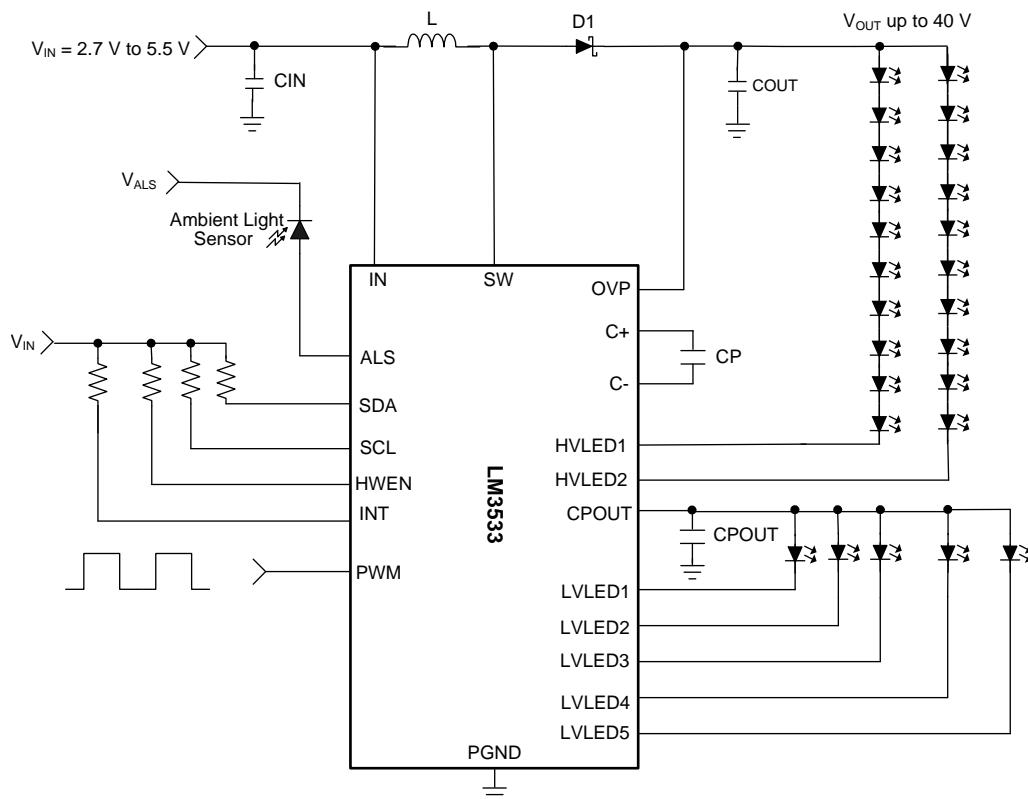

LM3533 是一款用于智能手机内背光、键盘和指示器 LED 的完整电源。高压电感升压转换器为用于显示屏背光和键盘功能的两个串联 LED 灯串供电 (HVLED1 和 HVLED2)。集成电荷泵为五个低电压指示器 LED 电流阱 (LVLED1 至 LVLED5) 提供偏置。所有低压电流阱均具有一种可编程图案生成器，可针对各种闪烁图案对其输出电流进行调制。

附加功能包括用于内容可调背光控制 (CABC) 的脉宽调制 (PWM) 控制输入以及一个带有 8 位内部模数转换器 (ADC) 的环境光传感器 (ALS) 接口，这两种功能可根据环境光照条件自动调节电流。PWM 和 ALS 输入均可用于控制任何高电压或低电压电流阱。

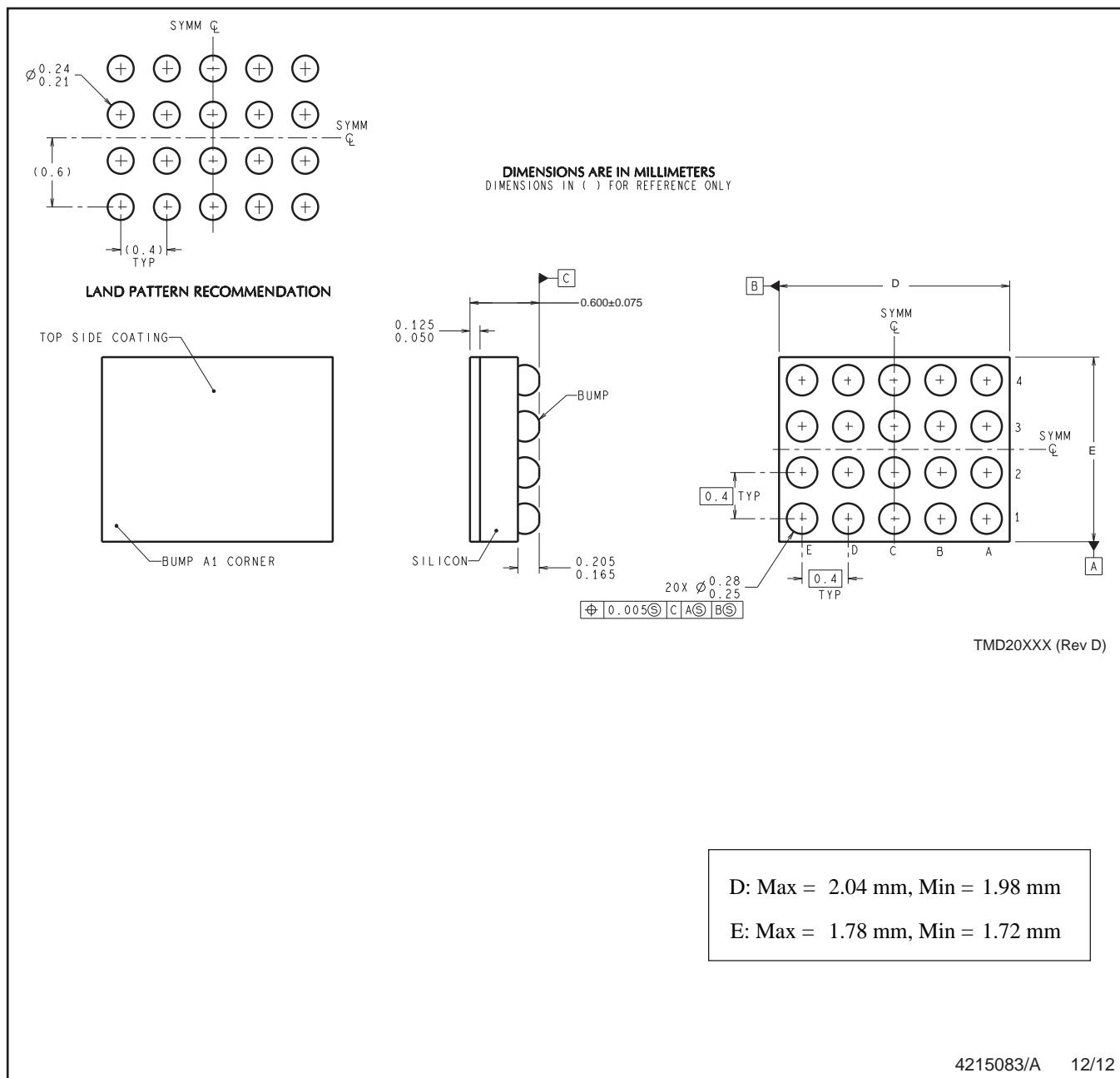

LM3533 完全可由一个 I<sup>2</sup>C 兼容接口进行编程。该器件采用 20 引脚芯片尺寸球状引脚栅格阵列 (DSBGA) 封装，其工作输入电压范围为 2.7V 至 5.5V，工作温度范围为 -40°C 至 +85°C。

### 器件信息<sup>(1)</sup>

| 部件号    | 封装         | 封装尺寸 (最大值)      |

|--------|------------|-----------------|

| LM3533 | DSBGA (20) | 2.04mm x 1.78mm |

(1) 要了解所有可用封装，请见数据表末尾的可订购产品附录。

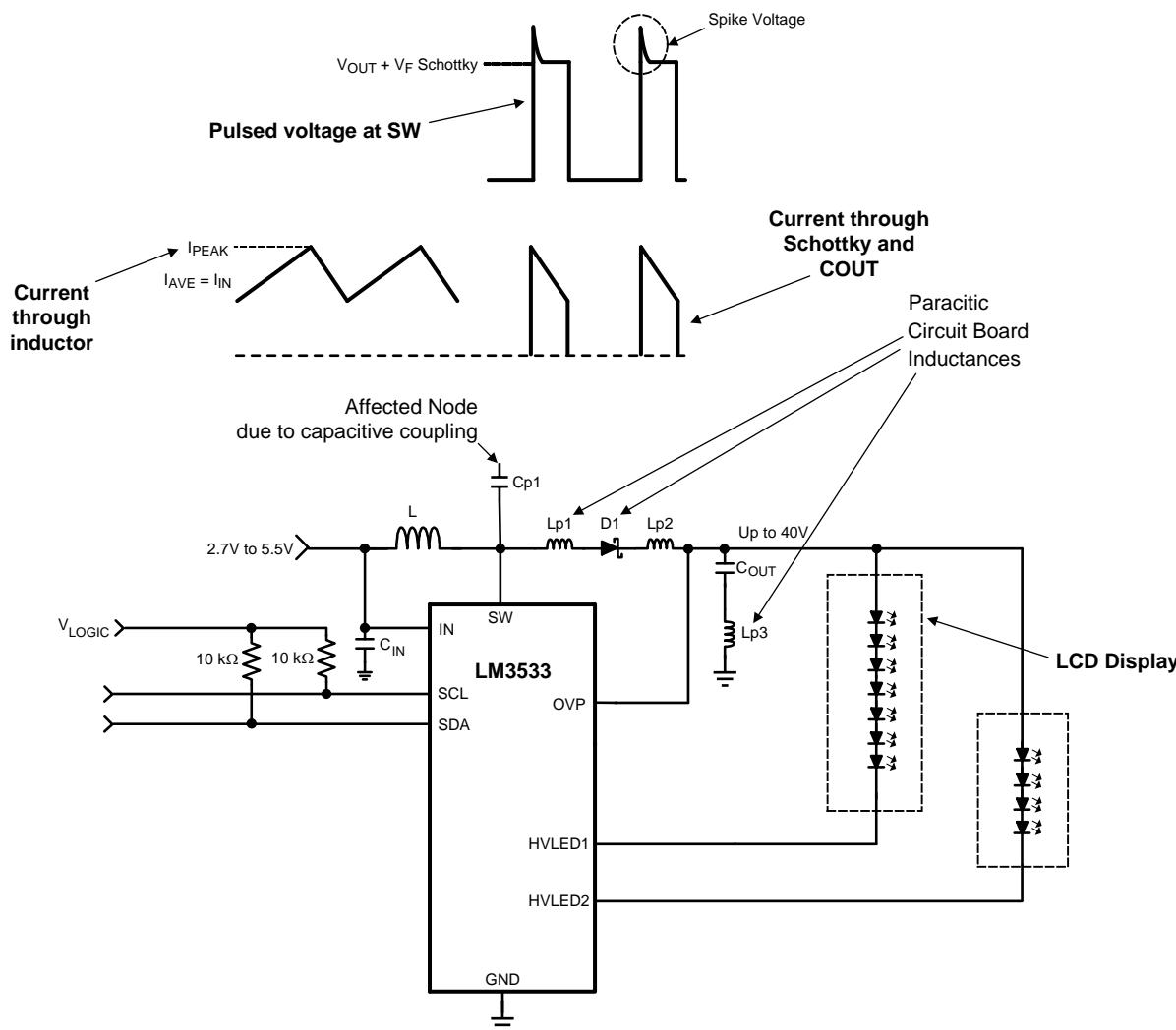

## 典型应用电路

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: [SNOSC68](#)

## 目录

|          |                                              |           |           |                                             |           |

|----------|----------------------------------------------|-----------|-----------|---------------------------------------------|-----------|

| <b>1</b> | <b>特性</b> .....                              | <b>1</b>  | 7.5       | Programming.....                            | 31        |

| <b>2</b> | <b>应用范围</b> .....                            | <b>1</b>  | 7.6       | Register Maps.....                          | 32        |

| <b>3</b> | <b>说明</b> .....                              | <b>1</b>  | <b>8</b>  | <b>Application and Implementation</b> ..... | <b>46</b> |

| <b>4</b> | <b>修订历史记录</b> .....                          | <b>2</b>  | 8.1       | Application Information.....                | 46        |

| <b>5</b> | <b>Pin Configuration and Functions</b> ..... | <b>3</b>  | 8.2       | Typical Application .....                   | 46        |

| <b>6</b> | <b>Specifications</b> .....                  | <b>4</b>  | <b>9</b>  | <b>Power Supply Recommendations</b> .....   | <b>51</b> |

| 6.1      | Absolute Maximum Ratings .....               | 4         | <b>10</b> | <b>Layout</b> .....                         | 52        |

| 6.2      | ESD Ratings.....                             | 4         | 10.1      | Layout Guidelines .....                     | 52        |

| 6.3      | Recommended Operating Conditions .....       | 4         | 10.2      | Layout Example .....                        | 56        |

| 6.4      | Thermal Information .....                    | 4         | <b>11</b> | 器件和文档支持 .....                               | 57        |

| 6.5      | Electrical Characteristics.....              | 5         | 11.1      | 器件支持 .....                                  | 57        |

| 6.6      | I <sup>2</sup> C Timing Requirements.....    | 6         | 11.2      | 相关文档 .....                                  | 57        |

| 6.7      | Typical Characteristics .....                | 7         | 11.3      | 社区资源.....                                   | 57        |

| <b>7</b> | <b>Detailed Description</b> .....            | <b>11</b> | 11.4      | 商标 .....                                    | 57        |

| 7.1      | Overview .....                               | 11        | 11.5      | 静电放电警告.....                                 | 57        |

| 7.2      | Functional Block Diagram .....               | 11        | 11.6      | Glossary .....                              | 57        |

| 7.3      | Feature Description.....                     | 12        | <b>12</b> | 机械、封装和可订购信息 .....                           | 57        |

| 7.4      | Device Functional Modes.....                 | 13        |           |                                             |           |

## 4 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (May 2013) to Revision C                                              | Page |

|-----------------------------------------------------------------------------------------------|------|

| • 已添加 器件信息和引脚配置和功能部分, ESD 额定值表, 特性描述, 器件功能模式, 应用和实施, 电源相关建议, 布局, 器件和文档支持以及机械、封装和可订购信息部分 ..... | 1    |

| Changes from Revision A (May 2013) to Revision B           | Page |

|------------------------------------------------------------|------|

| • Changed layout of National Data Sheet to TI format ..... | 55   |

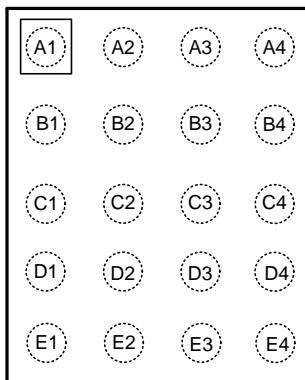

## 5 Pin Configuration and Functions

**YFQ Package

20-Pin DSBGA

Top View**

### Pin Functions

| PIN |        | TYPE | DESCRIPTION                                                                                                                                                                                                                 |

|-----|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   |      |                                                                                                                                                                                                                             |

| A1  | C-     | OUT  | Integrated charge pump flying capacitor negative terminal. Connect a 1- $\mu$ F ceramic capacitor from C+ to C-.                                                                                                            |

| A2  | C+     | OUT  | Integrated charge pump flying capacitor positive terminal. Connect a 1- $\mu$ F ceramic capacitor from C+ to C-.                                                                                                            |

| A3  | CPOUT  | OUT  | Integrated charge pump output terminal. Bypass CPOUT to GND with a 1- $\mu$ F ceramic capacitor.                                                                                                                            |

| A4  | IN     | IN   | Input voltage connection. Bypass IN to GND with a minimum 2.2- $\mu$ F ceramic capacitor.                                                                                                                                   |

| B1  | SCL    | IN   | Serial clock connection for I <sup>2</sup> C-compatible interface.                                                                                                                                                          |

| B2  | SDA    | I/O  | Serial data connection for I <sup>2</sup> C-compatible interface.                                                                                                                                                           |

| B3  | OVP    | IN   | Overvoltage sense Input. Connect OVP to the positive terminal of the inductive boost's output capacitor (COUT).                                                                                                             |

| B4  | GND    | GND  | Ground                                                                                                                                                                                                                      |

| C1  | HVLED1 | IN   | Input pin to high-voltage current sink 1 (40 V maximum). The boost converter regulates the minimum of HVLED1 and HVLED2 to 0.4 V.                                                                                           |

| C2  | INT    | OUT  | ALS interrupt output (INT). When INT mode is enabled this pin becomes an open-drain output that pulls low when the ALS changes zones. On power-up, INT mode is disabled and is high impedance and must be tied high or low. |

| C3  | PWM    | IN   | PWM brightness control input for CABC operation. PWM is a high-impedance input and cannot be left floating.                                                                                                                 |

| C4  | SW     | IN   | Drain connection for the internal NFET. Connect SW to the junction of the inductor and the Schottky diode anode.                                                                                                            |

| D1  | HVLED2 | IN   | Input pin high-voltage current sink 2 (40 V maximum). The boost converter regulates the minimum of HVLED1 and HVLED2 to 0.4 V.                                                                                              |

| D2  | ALS    | IN   | Ambient light sensor input.                                                                                                                                                                                                 |

| D3  | HWEN   | IN   | Hardware enable input. Drive this pin high to enable the device. Drive this pin low to force the device into a low power shutdown. HWEN is a high-impedance input and cannot be left floating.                              |

| D4  | LVLED5 | IN   | Low-voltage current sink 5                                                                                                                                                                                                  |

| E1  | LVLED1 | IN   | Low-voltage current sink 1                                                                                                                                                                                                  |

| E2  | LVLED2 | IN   | Low-voltage current sink 2                                                                                                                                                                                                  |

| E3  | LVLED3 | IN   | Low-voltage current sink 3                                                                                                                                                                                                  |

| E4  | LVLED4 | IN   | Low-voltage current sink 4                                                                                                                                                                                                  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)(3)</sup>

|                                                  | MIN                | MAX | UNIT |

|--------------------------------------------------|--------------------|-----|------|

| $V_{IN}$ to GND                                  | -0.3               | 6   | V    |

| $V_{SW}, V_{OVP}, V_{HVLED1}, V_{HVLED2}$ to GND | -0.3               | 45  | V    |

| $V_{SCL}, V_{SDA}, V_{ALS}, V_{PWM}$ to GND      | -0.3               | 6   | V    |

| $V_{INT}, V_{HWEN}, V_{CPOUT}$ to GND            | -0.3               | 6   | V    |

| $V_{LVLED1}- V_{LVLED5}$ , to GND                | -0.3               | 6   | V    |

| Continuous power dissipation                     | Internally limited |     |      |

| Junction temperature, $T_J$ -MAX                 | 150                |     |      |

| Maximum lead temperature (soldering)             | See <sup>(4)</sup> |     |      |

| Storage temperature, $T_{stg}$                   | -65                | 150 | °C   |

- Stresses beyond those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under *Recommended Operating Conditions*. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltages are with respect to the potential at the GND pin.

- If Military/Aerospace specified devices are required, contact the TI Sales Office/Distributors for availability and specifications.

- For detailed soldering specifications and information, refer to Texas Instruments Application Note 1112: *DSBGA Wafer Level Chip Scale Package (SNVA009)* available at [www.ti.com](http://www.ti.com).

### 6.2 ESD Ratings

|                                     | VALUE                                                             | UNIT  |

|-------------------------------------|-------------------------------------------------------------------|-------|

| $V_{(ESD)}$ Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 |

- JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                                                  | MIN | NOM | MAX | UNIT |

|--------------------------------------------------|-----|-----|-----|------|

| $V_{IN}$ to GND                                  | 2.7 | 5.5 |     | V    |

| $V_{SW}, V_{OVP}, V_{HVLED1}, V_{HVLED2}$ to GND | 0   | 40  |     | V    |

| $V_{LVLED1}- V_{LVLED5}$ to GND                  | 0   | 6   |     | V    |

| Junction temperature ( $T_J$ ) <sup>(2)(3)</sup> | -40 | 125 |     | °C   |

- All voltages are with respect to the potential at the GND pin.

- Internal thermal shutdown circuitry protects the device from permanent damage. Thermal shutdown engages at  $T_J = 140^{\circ}\text{C}$  (typical) and disengages at  $T_J = 125^{\circ}\text{C}$  (typical).

- In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature ( $T_{A-MAX}$ ) is dependent on the maximum operating junction temperature ( $T_{J-MAX-OP} = 125^{\circ}\text{C}$ ), the maximum power dissipation of the device in the application ( $P_{D-MAX}$ ), and the junction-to ambient thermal resistance of the part/package in the application ( $R_{\theta JA}$ ), as given by the equation:  $T_{A-MAX} = T_{J-MAX-OP} - (R_{\theta JA} \times P_{D-MAX})$ .

### 6.4 Thermal Information

| THERMAL METRIC <sup>(1)</sup>                                         | LM3533      | UNIT |

|-----------------------------------------------------------------------|-------------|------|

|                                                                       | YFQ (DSBGA) |      |

|                                                                       | 20 PINS     |      |

| $R_{\theta JA}$ Junction-to-ambient thermal resistance <sup>(2)</sup> | 55.3        | °C/W |

- For more information about traditional and new thermal metrics, see the *Semiconductor and IC Package Thermal Metrics* application report, [SPRA953](#).

- Junction-to-ambient thermal resistance ( $R_{\theta JA}$ ) is taken from a thermal modeling result, performed under the conditions and guidelines set forth in the JEDEC standard JESD51-7. The test board is a 4-layer FR-4 board measuring 102 mm × 76 mm × 1.6 mm with a 2 × 1 array of thermal vias. The ground plane on the board is 50 mm × 50 mm. Thickness of copper layers are 36  $\mu\text{m}$ /18  $\mu\text{m}$ /18  $\mu\text{m}$ /36  $\mu\text{m}$  (1.5 oz/1 oz/1 oz/1.5 oz). Ambient temperature in simulation is 22°C in still air. Power dissipation is 1 W. The value of  $R_{\theta JA}$  of this product in the DSBGA package could fall in a range as wide as 60°C/W to 110°C/W (if not wider), depending on PCB material, layout, and environmental conditions. In applications where high maximum power dissipation exists special care must be paid to thermal dissipation issues.

## 6.5 Electrical Characteristics

Unless otherwise specified  $V_{IN} = 3.6$  V; typical limits are for  $T_A = 25^\circ\text{C}$  and minimum and maximum limits apply over the full operating ambient temperature range ( $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$ ).

| PARAMETER              |                                                               | TEST CONDITIONS                                                                                         |                                                   | MIN  | TYP  | MAX      | UNIT             |

|------------------------|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------|------|------|----------|------------------|

| $I_{SHDN}$             | Shutdown current                                              | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$ , HWEN = GND                                             |                                                   |      | 1    | 5        | $\mu\text{A}$    |

| $I_{LED\_MIN}$         | Minimum LED current                                           | Full-scale current = 20.2 mA<br>Exponential mapping                                                     |                                                   |      | 9.5  |          | $\mu\text{A}$    |

| $T_{SD}$               | Thermal shutdown                                              |                                                                                                         |                                                   |      | 140  |          | $^\circ\text{C}$ |

|                        | Hysteresis                                                    |                                                                                                         |                                                   |      | 15   |          |                  |

| <b>BOOST CONVERTER</b> |                                                               |                                                                                                         |                                                   |      |      |          |                  |

| $I_{HVLED(1/2)}$       | Output current regulation (HVLED1 or HVLED2)                  | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$<br>full-scale current = 20.2mA, brightness code = 0xFF   |                                                   | 17   | 20.2 | 23       | mA               |

| $I_{MATCH\_HV}$        | HVLED1 to HVLED2 matching <sup>(1)</sup>                      | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                          | Both current sinks are assigned to Control Bank A | -2%  | 1%   | 2%       |                  |

| $V_{REG\_CS}$          | Regulated current sink headroom voltage                       |                                                                                                         |                                                   |      | 400  |          | mV               |

| $V_{HR\_HV}$           | Minimum current sink headroom voltage for HVLED current sinks | $I_{LED} = 95\%$ of nominal<br>full-scale current = 20.2 mA                                             |                                                   |      | 190  | 250      | mV               |

| $R_{DSON}$             | NMOS switch on resistance                                     | $I_{SW} = 500 \text{ mA}$                                                                               |                                                   |      | 0.3  |          | $\Omega$         |

| $I_{CL\_BOOST}$        | NMOS switch current limit                                     | $V_{IN} = 3.6 \text{ V}$                                                                                |                                                   | 880  | 1000 | 1120     | mA               |

| $V_{OVP}$              | Output overvoltage protection                                 | ON threshold, $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$<br>OVP select bits = 11                    |                                                   | 39   | 40   | 41       | V                |

|                        |                                                               | Hysteresis                                                                                              |                                                   |      | 1    |          |                  |

| $f_{SW}$               | Switching frequency                                           | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                          | Boost frequency select bit = 0                    | 450  | 500  | 550      | kHz              |

|                        |                                                               |                                                                                                         | Boost frequency select bit = 1                    | 900  | 1000 | 1100     |                  |

| $D_{MAX}$              | Maximum duty cycle                                            |                                                                                                         |                                                   |      | 94%  |          |                  |

| <b>CHARGE PUMP</b>     |                                                               |                                                                                                         |                                                   |      |      |          |                  |

| $I_{LVLED(1/2/3/4/5)}$ | Output current regulation (low-voltage current sinks)         | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$ , full-scale current = 20.2 mA<br>brightness code = 0xFF |                                                   | 17   | 20.2 | 23       | mA               |

| $I_{MATCH\_LV}$        | LVLED current sink matching <sup>(2)</sup>                    | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                          |                                                   | -2%  | 1%   | 2%       |                  |

| $V_{HR\_LV}$           | Minimum current sink headroom voltage for LVLED current sinks | $I_{LED} = 95\%$ of nominal, full-scale current = 20.2 mA                                               |                                                   |      | 80   | 110      | mV               |

| $V_{GTH}$              | Threshold for gain transition                                 | $V_{LVLED}$ falling                                                                                     |                                                   |      | 110  |          | mV               |

| $I_{CL\_PUMP}$         | Charge-pump current limit                                     | $3 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$ ,<br>output referred                                       | 1x gain                                           | 180  | 350  |          | mA               |

|                        |                                                               |                                                                                                         | 2x gain                                           |      | 240  |          |                  |

| $R_{OUT}$              | Charge-pump output resistance                                 | 1x gain                                                                                                 |                                                   |      | 1.1  |          | $\Omega$         |

| <b>HWEN INPUT</b>      |                                                               |                                                                                                         |                                                   |      |      |          |                  |

| $V_{HWEN}$             | Logic thresholds                                              | Logic low                                                                                               |                                                   | 0    | 0.4  |          | V                |

|                        |                                                               | Logic high                                                                                              |                                                   | 1.2  |      | $V_{IN}$ |                  |

| <b>PWM INPUT</b>       |                                                               |                                                                                                         |                                                   |      |      |          |                  |

| $V_{PWM\_L}$           | Input logic low                                               | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                          |                                                   | 0    | 400  |          | mV               |

| $V_{PWM\_H}$           | Input logic high                                              | $2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                          |                                                   | 1.25 |      | $V_{IN}$ | V                |

- LED current sink matching between HVLED1 and HVLED2 is given by taking the difference between either ( $I_{HVLED1}$  or  $I_{HVLED2}$ ) and the average current between the two, and dividing by the average current between the two. This simplifies to  $(I_{HVLED1} \text{ (or } I_{HVLED2}) - I_{HVLED(AVE)}) / (I_{HVLED(AVE)}) \times 100$ . In this test, both HVLED1 and HVLED2 are assigned to Bank A.

- LED current sink matching in the low-voltage current sinks (LVLED1 through LVLED5) is given as the maximum matching value between any two current sinks, where the matching between any two low voltage current sinks (X and Y) is given as  $(I_{LVLEDX} \text{ (or } I_{LVLEDY}) - I_{AVE(X-Y)}) / (I_{AVE(X-Y)}) \times 100$ . In this test all LVLED current sinks are assigned to Bank C.

## Electrical Characteristics (continued)

Unless otherwise specified  $V_{IN} = 3.6$  V; typical limits are for  $T_A = 25^\circ\text{C}$  and minimum and maximum limits apply over the full operating ambient temperature range ( $-40^\circ\text{C} \leq T_A \leq +85^\circ\text{C}$ ).

| PARAMETER                                                          | TEST CONDITIONS                                                                                                                                          | MIN   | TYP   | MAX      | UNIT |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|----------|------|

| <b>INT OUTPUT</b>                                                  |                                                                                                                                                          |       |       |          |      |

| $V_{LOW}$                                                          | Output Logic Low (INT Mode)<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                                            |       |       | 400      | mV   |

| <b>I<sup>2</sup>C-COMPATIBLE VOLTAGE SPECIFICATIONS (SCL, SDA)</b> |                                                                                                                                                          |       |       |          |      |

| $V_{IL}$                                                           | Input logic low<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                                                        | 0     |       | 400      | mV   |

| $V_{IH}$                                                           | Input logic high<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                                                       | 1.25  |       | $V_{IN}$ | V    |

| $V_{OL}$                                                           | Output logic low (SDA)<br>$I_{LOAD} = 3\text{mA}$                                                                                                        |       |       | 400      | mV   |

| <b>AMBIENT LIGHT SENSOR (ALS)</b>                                  |                                                                                                                                                          |       |       |          |      |

| $R_{ALS}$                                                          | ALS internal pulldown resistor in analog sensor input mode<br>$R_{ALS} \text{ Select Register} = 0x0F$<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$ | 12.36 | 13.33 | 13.94    | kΩ   |

| $V_{ALS\_REF}$                                                     | Ambient Light Sensor Reference Voltage<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                                 | 1.9   | 2     | 2.1      | V    |

| $V_{ALS\_MIN}$                                                     | Minimum Threshold for ALS Input Voltage Sensing<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$ , Code 0 to 1 transition point                         | 3     | 10    | 15       | mV   |

| $t_{CONV}$                                                         | Conversion Time                                                                                                                                          |       |       | 140      | μs   |

| LSB                                                                | ADC Resolution<br>$2.7 \text{ V} \leq V_{IN} \leq 5.5 \text{ V}$                                                                                         |       |       | 7.8      | mV   |

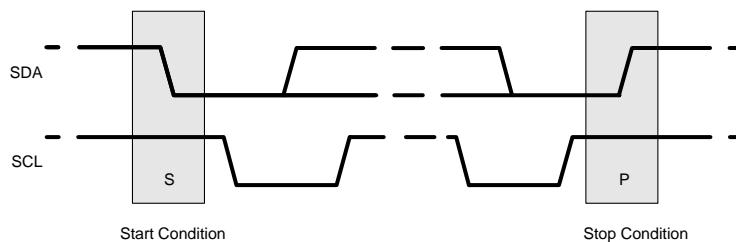

## 6.6 I<sup>2</sup>C Timing Requirements

|       |                                          | MIN | NOM | MAX | UNIT |

|-------|------------------------------------------|-----|-----|-----|------|

| $t_1$ | SCL (Clock Period)                       | 2.5 |     |     | μs   |

| $t_2$ | Data In Setup Time to SCL High           | 100 |     |     | ns   |

| $t_3$ | Data Out Stable After SCL Low            | 0   |     |     | ns   |

| $t_4$ | SDA Low Setup Time to SCL Low (Start)    | 100 |     |     | ns   |

| $t_5$ | SDA High Hold Time After SCL High (Stop) | 100 |     |     | ns   |

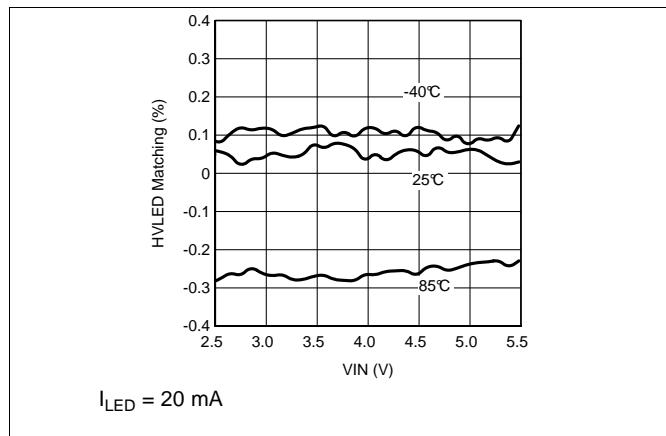

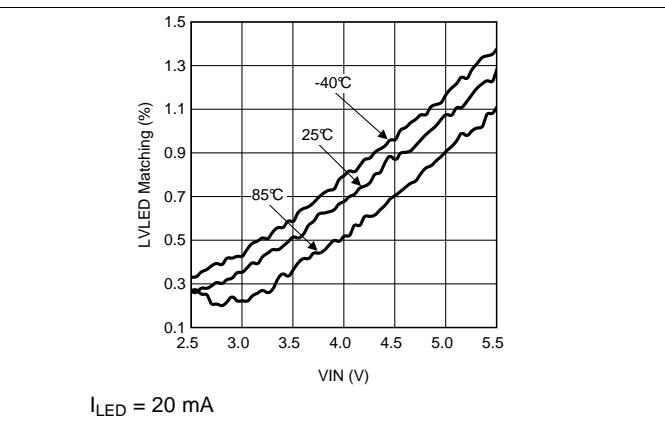

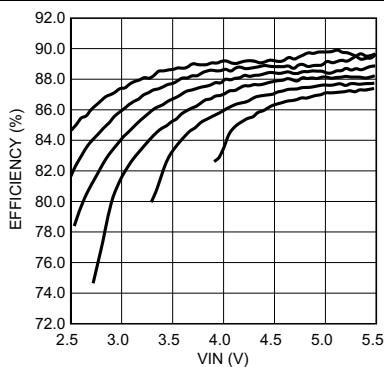

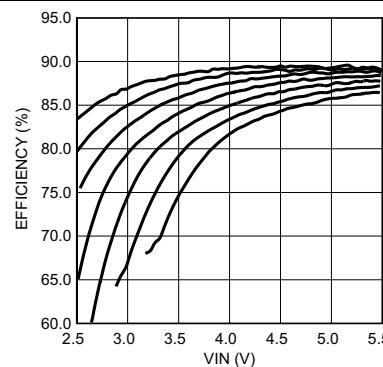

## 6.7 Typical Characteristics

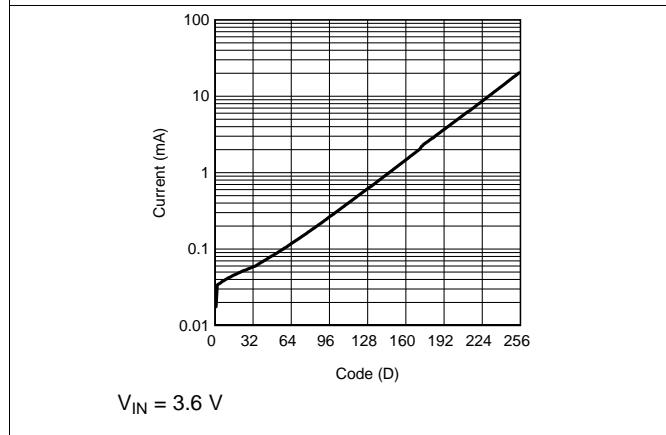

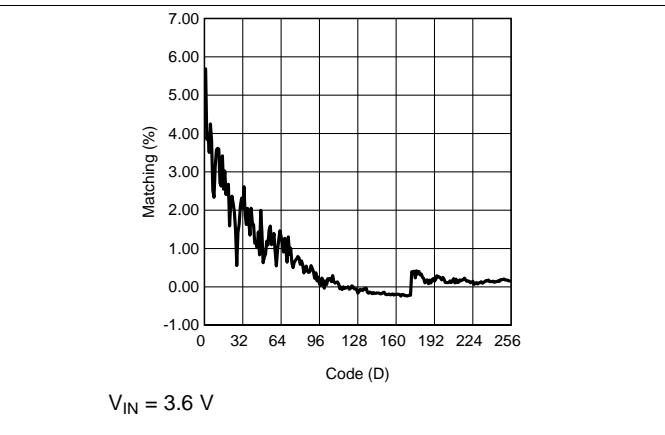

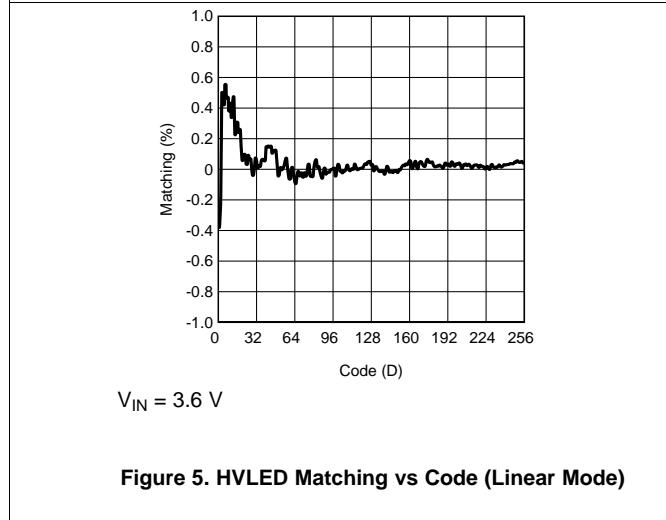

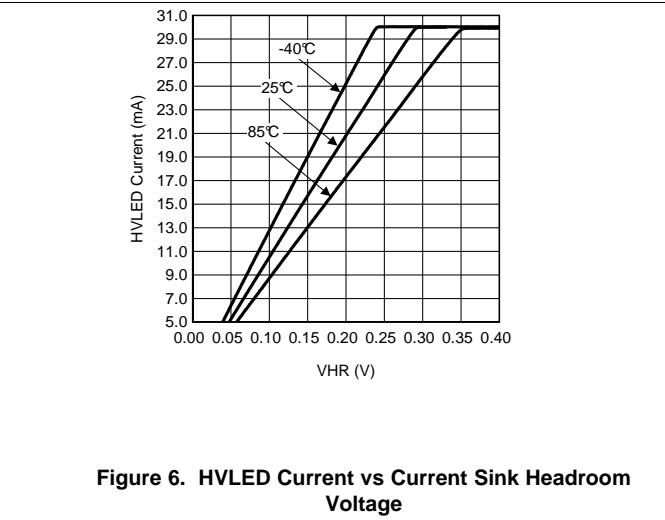

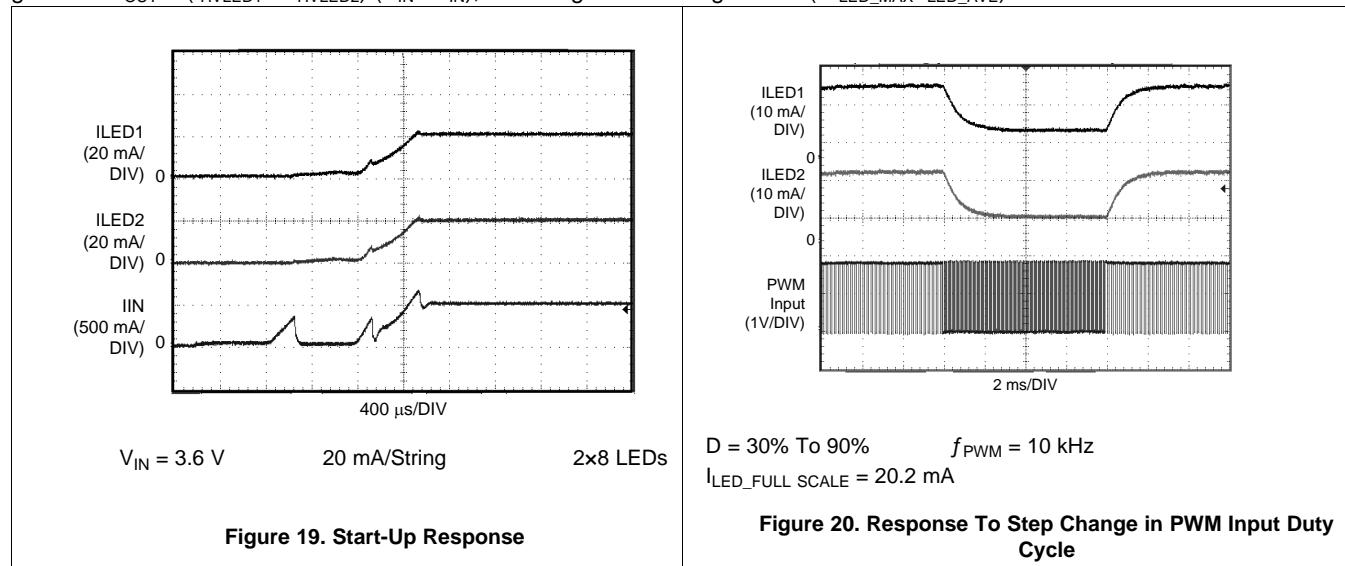

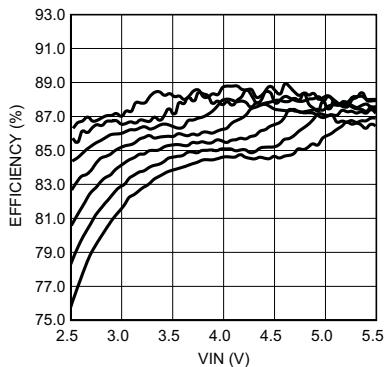

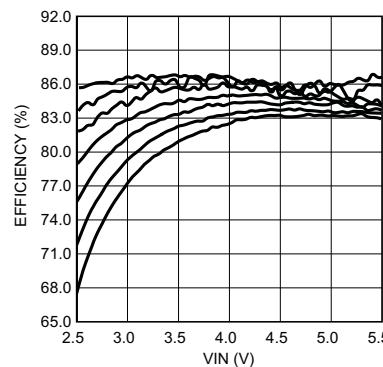

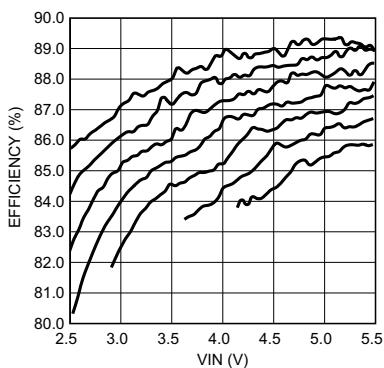

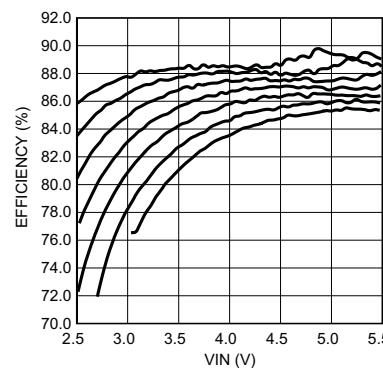

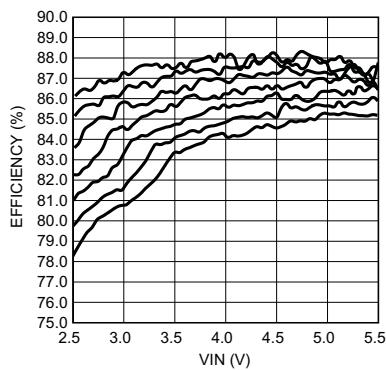

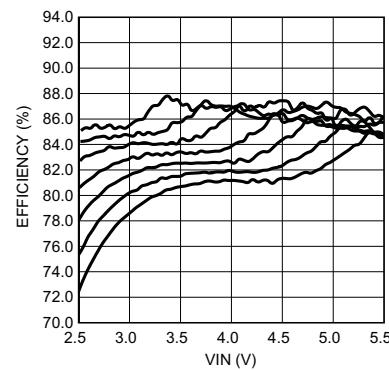

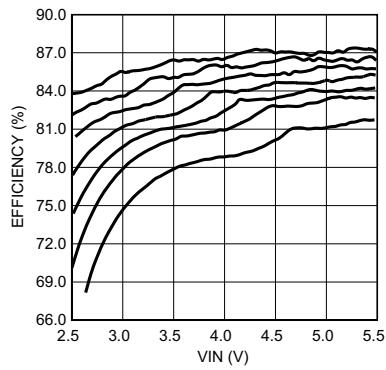

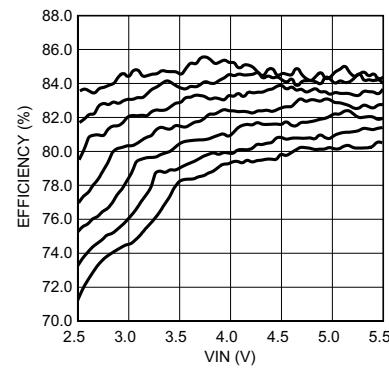

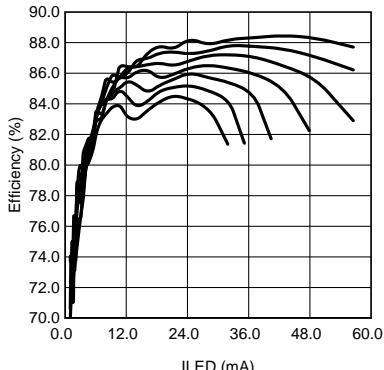

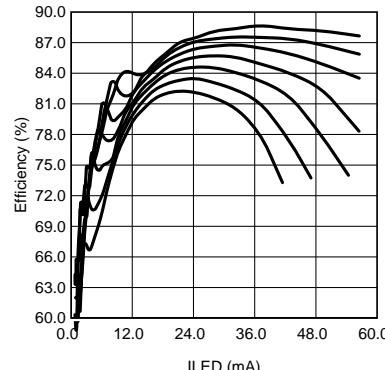

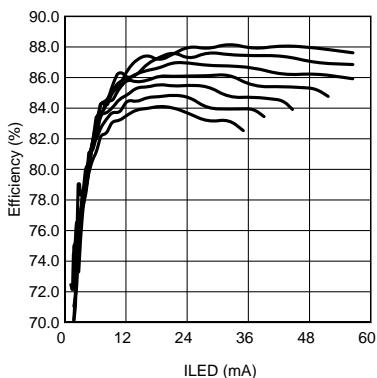

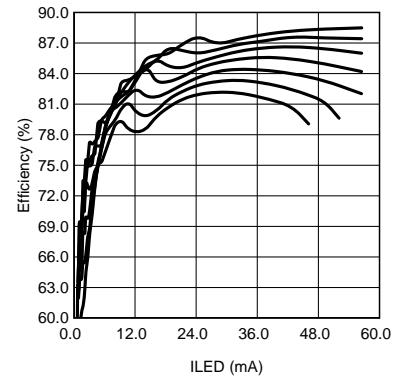

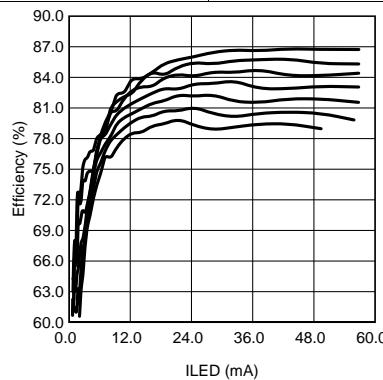

$V_{IN} = 3.6$  V, LEDs are WLEDs part number SML-312WBCW(A), typical application circuit with  $L = TDK$  (VLF302512, 4.7  $\mu$ H, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A = 25^\circ\text{C}$ , unless otherwise specified. Efficiency is given as  $V_{OUT} \times (I_{HVLED1} + I_{HVLED2}) / (V_{IN} \times I_{IN})$ ; matching curves are given as  $(\Delta I_{LED\_MAX} / I_{LED\_AVE})$ .

**Figure 1. HVLED Matching vs  $V_{IN}$ , Temp**

**Figure 2. LVLED Matching vs  $V_{IN}$ , Temp**

**Figure 3. HVLED Current vs Code (Exponential Mode)**

**Figure 4. HVLED Matching vs Code (Exponential Mode)**

**Figure 5. HVLED Matching vs Code (Linear Mode)**

**Figure 6. HVLED Current vs Current Sink Headroom Voltage**

## Typical Characteristics (continued)

$V_{IN} = 3.6$  V, LEDs are WLEDs part number SML-312WBCW(A), typical application circuit with  $L = TDK$  (VLF302512, 4.7  $\mu$ H, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A = 25^\circ\text{C}$ , unless otherwise specified. Efficiency is given as  $V_{OUT} \times (I_{HVLED1} + I_{HVLED2}) / (V_{IN} \times I_{IN})$ ; matching curves are given as  $(\Delta I_{LED\_MAX} / I_{LED\_AVE})$ .

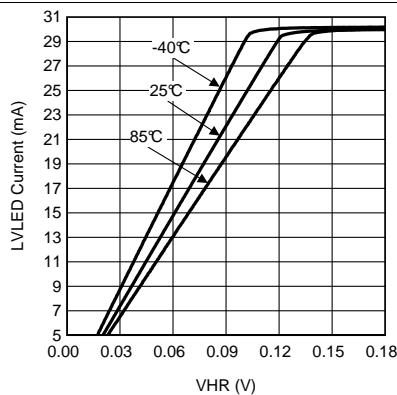

Figure 7. LVLED Current vs Current Sink Headroom Voltage

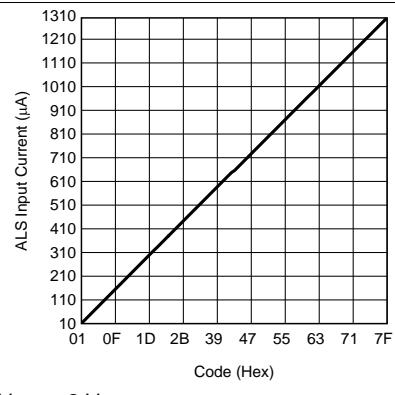

$V_{ALS} = 2$  V

Figure 8. ALS Input Current vs Code

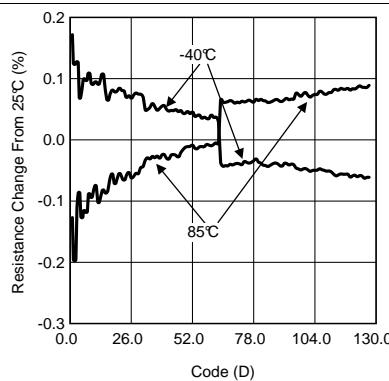

Figure 9. ALS Resistance vs Code (Temp)

(Code 0x50)

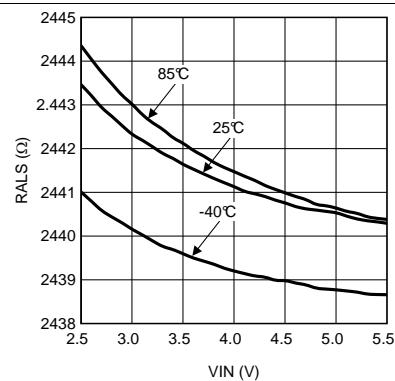

Figure 10. ALS Resistance vs  $V_{IN}$

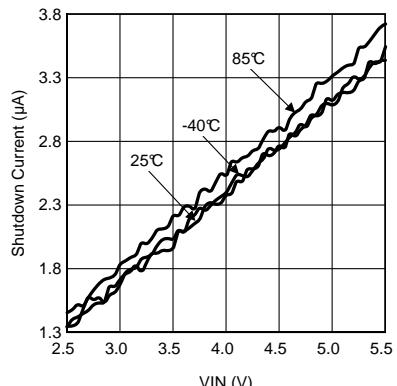

Figure 11. Shutdown Current vs  $V_{IN}$

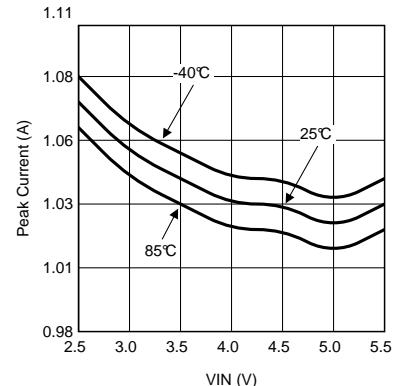

Figure 12. Closed Loop Current Limit vs  $V_{IN}$

## Typical Characteristics (continued)

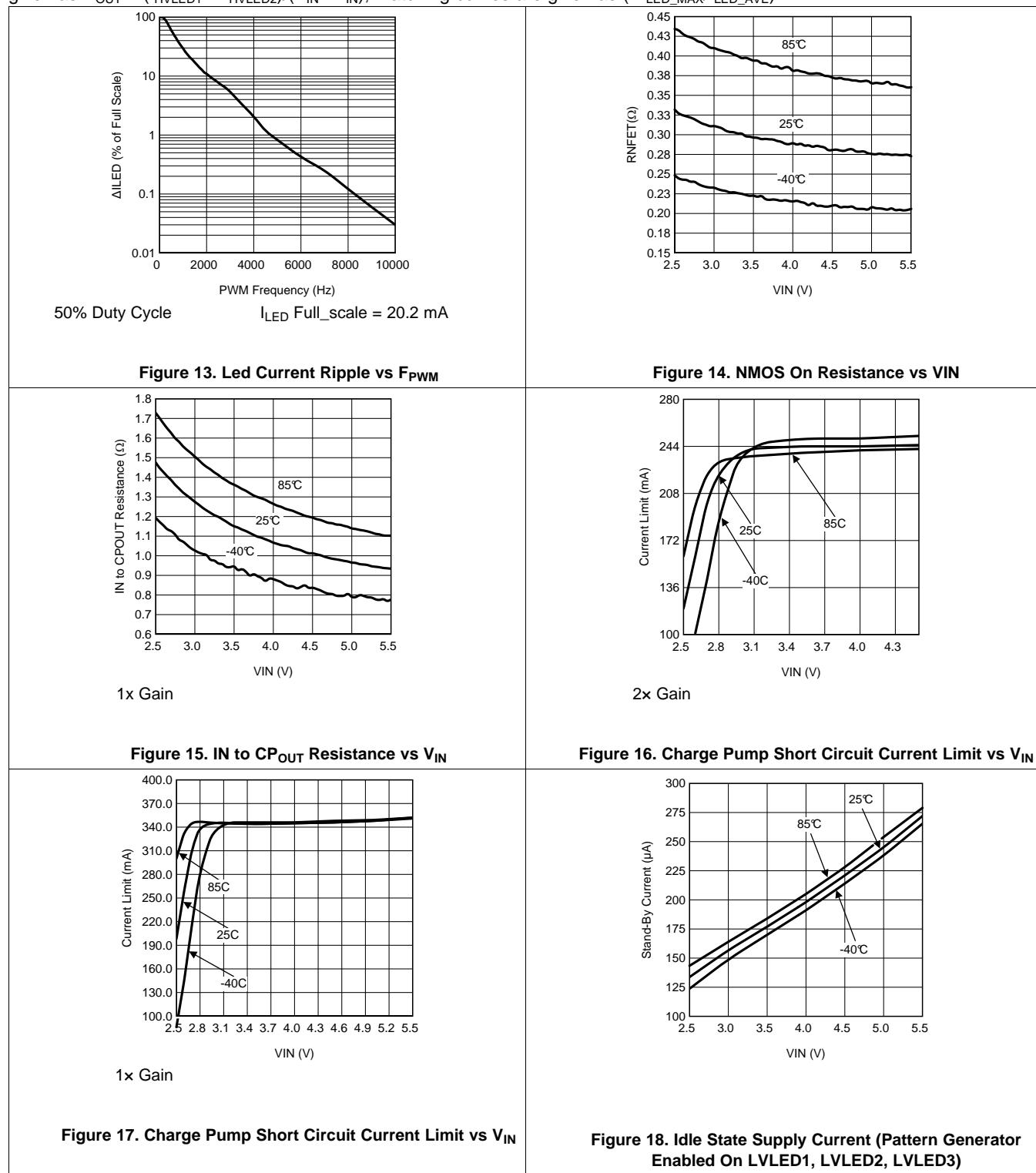

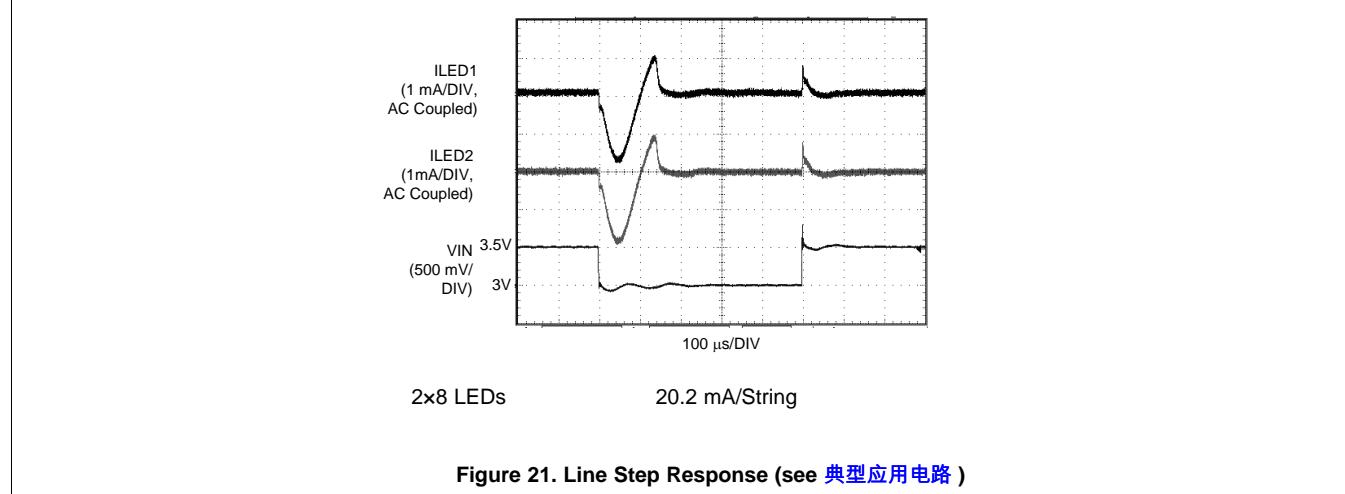

$V_{IN} = 3.6$  V, LEDs are WLEDs part number SML-312WBCW(A), typical application circuit with  $L = TDK$  (VLF302512, 4.7  $\mu$ H, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A = 25^\circ\text{C}$ , unless otherwise specified. Efficiency is given as  $V_{OUT} \times (I_{HVLED1} + I_{HVLED2}) / (V_{IN} \times I_{IN})$ ; matching curves are given as  $(\Delta I_{LED\_MAX} / I_{LED\_AVE})$ .

## Typical Characteristics (continued)

$V_{IN} = 3.6$  V, LEDs are WLEDs part number SML-312WBCW(A), typical application circuit with  $L = TDK$  (VLF302512, 4.7  $\mu$ H, 10  $\mu$ H, 22  $\mu$ H where specified), Schottky = On-Semi (NSR0240V2T1G),  $T_A = 25^\circ\text{C}$ , unless otherwise specified. Efficiency is given as  $V_{OUT} \times (I_{HVLED1} + I_{HVLED2}) / (V_{IN} \times I_{IN})$ ; matching curves are given as  $(\Delta I_{LED\_MAX} / I_{LED\_AVE})$ .

## 7 Detailed Description

### 7.1 Overview

The LM3533 provides the power for two high-voltage LED strings (up to 40 V at 30 mA each) and 5 low-voltage LEDs (up to 6 V at 30 mA each). The two high-voltage LED strings are powered from an integrated boost converter. The five low-voltage LEDs are powered from an integrated 2x charge pump.

The device is programmable over an I<sup>2</sup>C-compatible interface. Additional features include a pulse width modulation (PWM) input for content adjustable brightness control, an ambient light sensor input (ALS) for ambient light current control, and 4 programmable pattern generators for RGB and indicator blinking functions on the low-voltage LEDs.

### 7.2 Functional Block Diagram

## 7.3 Feature Description

### 7.3.1 Control Bank Mapping

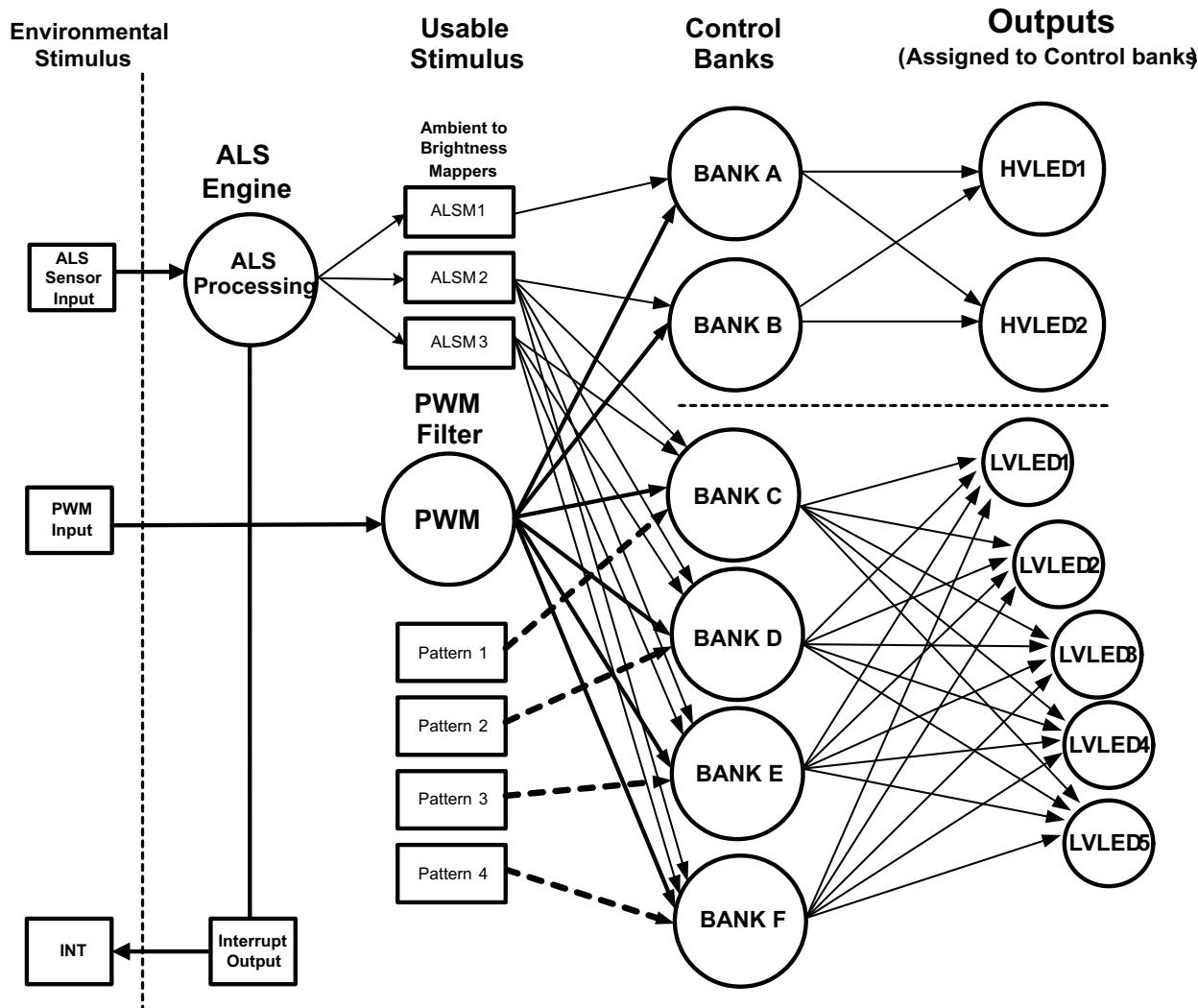

Control of the LM3533's current sinks is not done directly, but through the programming of Control Banks. The current sinks are then assigned to the programmed Control Bank. This allows for a wide variety of current control possibilities where LEDs can be grouped and controlled via specific Control Banks (see [Figure 22](#)).

#### 7.3.1.1 High-Voltage Control Banks (A/B)

There are 2 high-voltage control banks (A and B). Both high-voltage current sinks can be assigned to either Control Bank A or Control Bank B. Assigning both current sinks to the same control bank allows for better LED current matching. Assigning each current sink to different control banks allows for each current sink to be programmed with a different current. The high-voltage control bank mapping is done via bits [1:0] of the Current Sink Output Configuration Register #1 (address 0x10).

#### 7.3.1.2 Low-Voltage Control Banks (C, D, E, And F)

There are 4 low-voltage control banks (C, D, E, and F). Any low-voltage current sink (LVLED1 to LVLED5) can be assigned to any of the low-voltage control banks. Assigning every low-voltage current sink to the same control bank allows for the best matching between LEDs. Assigning each low-voltage current sink to different control banks allows for each current sink to be programmed with different current levels.

### 7.3.2 Pattern Generator

The LM3533 contains 4 independently programmable pattern generators for each Control Bank. Each pattern generator can have its own separate pattern: different rise and fall times, delays from turn-on, high and low-current settings, and pattern high and low times.

### 7.3.3 Ambient Light Sensor Interface

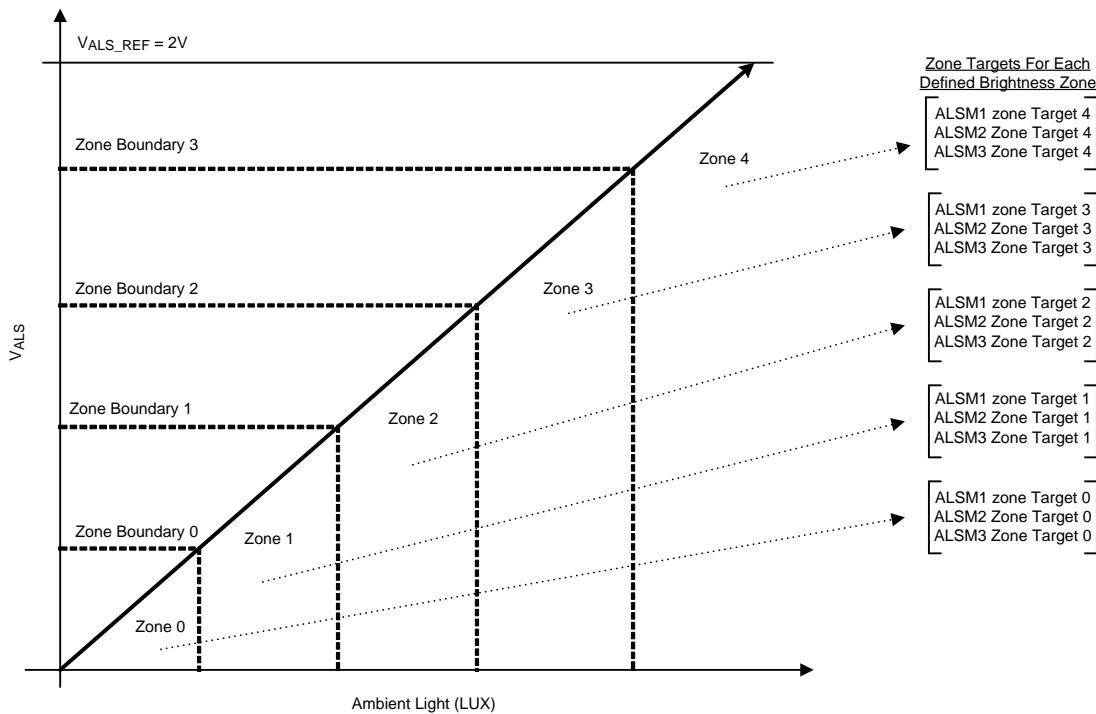

The LM3533 contains an ambient light sensor interface (ALS). The ALS input is designed to connect to the output of either an analog output or PWM output ambient light sensor. The sensor output (or ambient light information) is digitized and processed by the LM3533. The light information is then compared against the LM3533's five user-configurable brightness zones. Each brightness zone points to a brightness zone target current. Each group of target currents forms an ALS mapper. The LM3533 has three groups of ALS Mappers where each mapper can be assigned to any of the high or low-voltage control banks (see [Figure 26](#)).

### 7.3.4 PWM Input

The PWM input which can be assigned to any of the high- or low-voltage control banks. When assigned to a control bank, the programmed current in the control bank also becomes a function of the duty cycle at the PWM input.

### 7.3.5 HWEN Input

HWEN is the global hardware enable to the LM3533. HWEN must be pulled high to enable the device. HWEN is a high-impedance input so it cannot be left floating. When HWEN is pulled low the LM3533 is placed in shutdown, and all the registers are reset to their default state.

### 7.3.6 Thermal Shutdown

The LM3533 contains a thermal shutdown protection. In the event the die temperature reaches 140°C, the boost, charge pump and current sinks shut down until the die temperature drops to typically 125°C.

## Feature Description (continued)

Figure 22. Functional Control Diagram

## 7.4 Device Functional Modes

### 7.4.1 High-Voltage Boost Converter

The high-voltage boost converter provides power for the two high-voltage current sinks (HVLED1 and HVLED2). The boost circuit operates using a 4.7- $\mu$ H to 22- $\mu$ H inductor and a 1- $\mu$ F output capacitor. The selectable 500-kHz or 1-MHz switching frequency allows for the use of small external components and provides for high boost-converter efficiency. Both HVLED1 and HVLED2 feature an adaptive current regulation scheme where the feedback point (HVLED1 or HVLED2) is regulated to a minimum of 400 mV. When there are different voltage requirements in both high-voltage LED strings (string mismatch), the LM3533 regulates the feedback point of the highest voltage string to 400 mV and drop the excess voltage of the lower voltage string across the lower strings current sink.

## Device Functional Modes (continued)

#### 7.4.1.1 High-Voltage Current Sinks (HVLED1 And HVLED2)

HVLED1 and HVLED2 control the current in the high-voltage LED strings. Each current sink has 5-bit full-scale current programmability and 8-bit brightness control. Either current sink can have its current set through a dedicated brightness register or be controlled via the ambient light sensor interface. Configuration of the high-voltage current sinks is done through the Control A/B Brightness Configuration Register (see [Table 8](#)).

#### 7.4.1.2 High-Voltage Current String Biasing

Each high-voltage current string can be powered from the LM3533's boost output (COUT) or from an external source. The Anode Connect Register bits [1:0] determine where the high-voltage current string anodes are connected. When set to 1 (default) the high-voltage current sink inputs are included in the boost feedback loop. This allows the boost converter to adjust its output voltage in order to maintain at least 400 mV at the current sink input.

When powered from alternate sources, bits [1:0] must be set to 0 . This removes the particular current sink from the boost feedback loop. In these configurations the application must ensure that the headroom voltage across the high-voltage current sink is high enough to prevent the current sink from going into dropout (see the [Typical Characteristics](#) for data on the high-voltage LED current vs headroom voltage).

Setting the Anode Connect Register bits also determines how the shorted high-voltage LED String Fault flag is triggered (see [Fault Flags/Protection Features](#)).

#### 7.4.1.3 Boost Switching-Frequency Select

The LM3533's boost converter can have a 1-MHz or 500-kHz switching frequency. For a 500-kHz switching frequency the inductor must be between 10  $\mu$ H and 22  $\mu$ H. For the 1MHz switching frequency the inductor can be between 4.7  $\mu$ H and 22  $\mu$ H. The boost frequency is programmed through bit [1] of the OVP/Boost Frequency/PWM Polarity Select register.

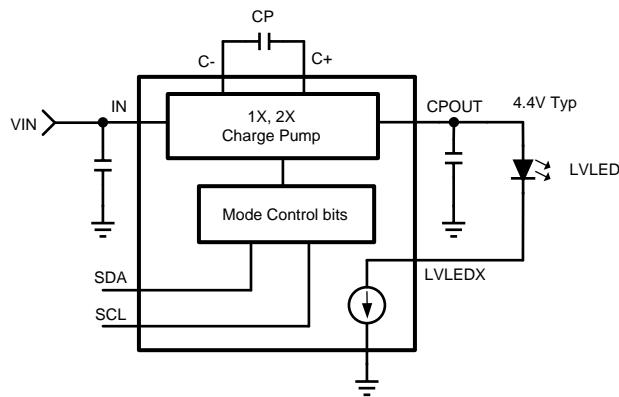

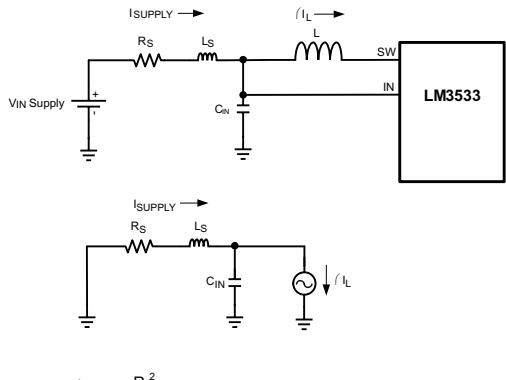

## 7.4.2 Integrated Charge Pump

The LM3533 features an integrated (2x/1x) charge pump capable of supplying up to 150 mA. The fixed 1-MHz switching frequency allows for use of tiny 1- $\mu$ F ceramic flying capacitors (CP) and output capacitor (C<sub>OUT</sub>). The charge pump can supply the power for the low-voltage LEDs connected to LVLED1 to LVLED5 and can operate in 4 different modes: disabled, automatic gain, 1x gain, or 2x gain (see [Figure 23](#)).

**Figure 23. Integrated Charge Pump**

#### 7.4.2.1 Charge Pump Disabled

With the charge pump disabled, the path from IN to CPOUT is high impedance. Additionally, with the charge pump disabled, the low-voltage current sinks can still be active, thus allowing the low-voltage LEDs to be biased from external sources (see [Low-Voltage LED Biasing](#)). Disabling the charge pump also has no influence on the state of the low-voltage current sinks. For instance, if a low-voltage current string is set to have its anode connected to CPOUT, and the charge pump is disabled, the current sink continues to try to sink current.

## Device Functional Modes (continued)

### 7.4.2.2 Automatic Gain

In Automatic Gain Mode the charge pump gain transition is actively selected to maintain LED current regulation in the CPOUT-connected, low-voltage current sinks. At higher input voltages the charge pump operates in Pass Mode ( $1\times$  gain) allowing the voltage at CPOUT to track the input voltage. As  $V_{IN}$  drops, the voltage on the low-voltage current sink(s) also drops. Once any of the active, CPOUT-connected, low-voltage current sink input voltages reach typically 100 mV, the charge pump automatically switches to a gain of  $2\times$  thus preventing dropout (see [2x Gain](#)). Once the charge pump switches over to  $2\times$  gain it remains in  $2\times$  gain, even if the current sink input voltage goes above the switch over threshold.

### 7.4.2.3 Automatic Gain (Flying Capacitor Detection)

In Automatic Gain Mode the LM3533 starts up and automatically detect if there is a flying capacitor (CP) connected from C+ to C-. If there is, Automatic Gain Mode operates normally. If the detection circuitry detects that there is no flying capacitor connected, the LM3533 automatically switches to  $1\times$  Gain mode.

### 7.4.2.4 1x Gain

In  $1\times$  Gain Mode the charge pump passes  $V_{IN}$  directly through to CPOUT. There is a resistive drop between IN and CPOUT in this mode ( $1.1\ \Omega$ ) which must be accounted for when determining the headroom requirement for the low-voltage current sinks. In forced  $1\times$  Gain Mode the charge pump does not switch; thus, the flying capacitor (CP) and output capacitor (CPOUT) can be omitted from the circuit.

### 7.4.2.5 2x Gain

In  $2\times$  Gain Mode the internal charge pump doubles  $V_{IN}$  and post-regulate CPOUT to typically 4.4 V. This allows for biasing LEDs whose forward voltages are greater than the input supply ( $V_{IN}$ ).

### 7.4.2.6 Low-Voltage Current Sinks (LVLED1 to LVLED5)

Current sinks LVLED1 to LVLED5 each provide the current for a single LED. These low-voltage sinks are configurable with different blinking patterns via the 4 internal pattern generators. Each low-voltage current sink has 8-bit brightness control and 5-bit full-scale current programmability. Additionally, each low-voltage current sink can have its current set through a dedicated brightness register, the PWM input, the ambient light sensor interface, or a combination of these. Configuration of the low-voltage current sinks is done through the low-voltage Control Banks (C, D, E, or F). Any low-voltage current sink can be mapped to any of the low-voltage control banks.

### 7.4.2.7 Low-Voltage LED Biasing

Each low-voltage LED can be powered from the LM3533's charge pump output (CPOUT) or from an external source. When powered from CPOUT the anode connect bit (Anode Connect Register bits [6:2]) for that particular low-voltage current sink must be set to '1' (default). This allows for the specific low-voltage current sink to have control over the charge pumps gain control (see [Automatic Gain](#) section).

When powered from alternate sources (such as VIN) the anode connect bit for the particular low-voltage current sink must be set to '0'. This removes the particular current sink from the charge pump feedback loop. In these configurations the application must ensure that the headroom voltage across the low-voltage current sink is high enough to prevent the low-voltage current sinks from going into dropout (see [Typical Characteristics](#) for data on the low-voltage LED current vs headroom voltage).

The LVLEDx Anode Connect bits also determine how the Shorted low-voltage LED String fault flag is triggered (see [Fault Flags/Protection Features](#)).

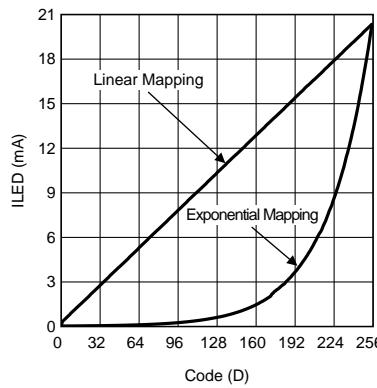

## 7.4.3 LED Current Mapping Modes

All control banks can be programmed for either exponential or linear mapping modes (see [Figure 24](#)). These modes determine the transfer characteristic of backlight code to LED current.

## Device Functional Modes (continued)

### 7.4.3.1 Exponential Mapping

In Exponential Mapping mode the brightness code to backlight current transfer function is given by [Equation 1](#):

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.862 \times \left[ \frac{46.6 - \left( \frac{Code+1}{5.5} \right)}{5.5} \right] \times D_{PWM}$$

where

- $I_{LED\_FULLSCALE}$  is the full-scale LED current setting (see [Table 11](#))

- Code is the backlight code in the Brightness register

- $D_{PWM}$  is the PWM input duty cycle.

(1)

In Exponential Mapping mode the current ramp (either up or down) appears to the human eye as a more uniform transition than the linear ramp. This is due to the logarithmic response of the eye.

### 7.4.3.2 Linear Mapping

In Linear Mapping Mode the brightness code to backlight current has a linear relationship and follows [Equation 2](#):

$$I_{LED} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times Code \times D_{PWM}$$

where

- $I_{LED\_FULLSCALE}$  is the full-scale LED current setting

- Code is the backlight code in the Brightness register

- $D_{PWM}$  is the PWM input duty cycle.

(2)

Figure 24. LED Current Mapping Modes

## 7.4.4 LED Current Ramping

### 7.4.4.1 Start-Up/Shutdown Ramp

The startup and shutdown ramp times are independently programmable in the Start-Up/Shutdown Transition Time Register (see [Table 4](#)). There are 8 different start-up and 8 different shutdown times. The start-up times can be programmed independently from the shutdown times, but each Control bank is not independently programmable. For example, programming a start-up or shutdown time does not affect the already pre-programmed ramp time for each Control Bank.

The start-up ramp time is from when the Control Bank is enabled to when the LED current reaches its initial set point. The shutdown ramp time is from when the Control Bank is disabled to when the LED current reaches 0.

## Device Functional Modes (continued)

### 7.4.4.2 Run-Time Ramp

Current ramping from one brightness level to the next is programmed via the Run-Time Transition Time Register (see [Table 5](#)). There are 8 different ramp-up times and 8 different ramp-down times. The ramp-up time can be programmed independently from the ramp-down time, but each Control Bank cannot be independently programmed. For example, programming a ramp-up or ramp-down time is a global setting for all Control Banks.

### 7.4.5 Brightness Register Current Control

For simple user-adjustable current control, the LM3533 features Brightness Register Current Control. This mode is selected via the Control Bank Brightness Configuration Registers (see [Table 8](#) and [Table 10](#)). Once set for Brightness Register Current Control, the LED current is set by writing directly to the appropriate Control Bank Brightness Registers (see [Table 28](#)). In this mode the current for a particular Control Bank becomes a function of the full-scale LED current, the 8-bit code in the respective brightness register, and the PWM input duty cycle (if PWM is enabled). The Control Bank Brightness Register contains an 8-bit code which represents the percentage of the full-scale LED current. This percentage of full-scale current is different depending on the selected mapping mode (see [LED Current Mapping Modes](#)).

### 7.4.6 PWM Control

The LM3533 device's PWM input can be enabled for any of the Control Banks (see [Table 7](#)). Once enabled, the LED current becomes a function of the code in the Control Bank Brightness Configuration Register and the PWM input-duty cycle.

The PWM input accepts a logic level voltage and internally filters it to an analog control voltage. This results in a linear response of duty cycle to current, where 100% duty cycle corresponds to the programmed brightness code multiplied by the Full-Scale Current setting.

#### 7.4.6.1 PWM Input Frequency Range

The usable input frequency range for the PWM input is governed on the low end by the cutoff frequency of the internal low-pass filter (540 Hz,  $Q = 0.33$ ) and on the high end by the propagation delays through the internal logic. For frequencies below 2 kHz the current ripple begins to become a larger portion of the DC LED current. Additionally, at lower PWM frequencies the boost output voltage ripple increases, causing a non-linear response from the PWM duty cycle to the average LED current due to the response time of the boost. For the best response of current vs. duty cycle, the PWM input frequency must be kept between 2 kHz and 100 kHz.

#### 7.4.6.2 PWM Input Polarity

The PWM Input can be set for active low polarity, where the LED current is a function of the negative duty cycle. This is set via the OVP/Boost Frequency/PWM Polarity Register (see [Table 20](#)).

### 7.4.7 ALS Current Control

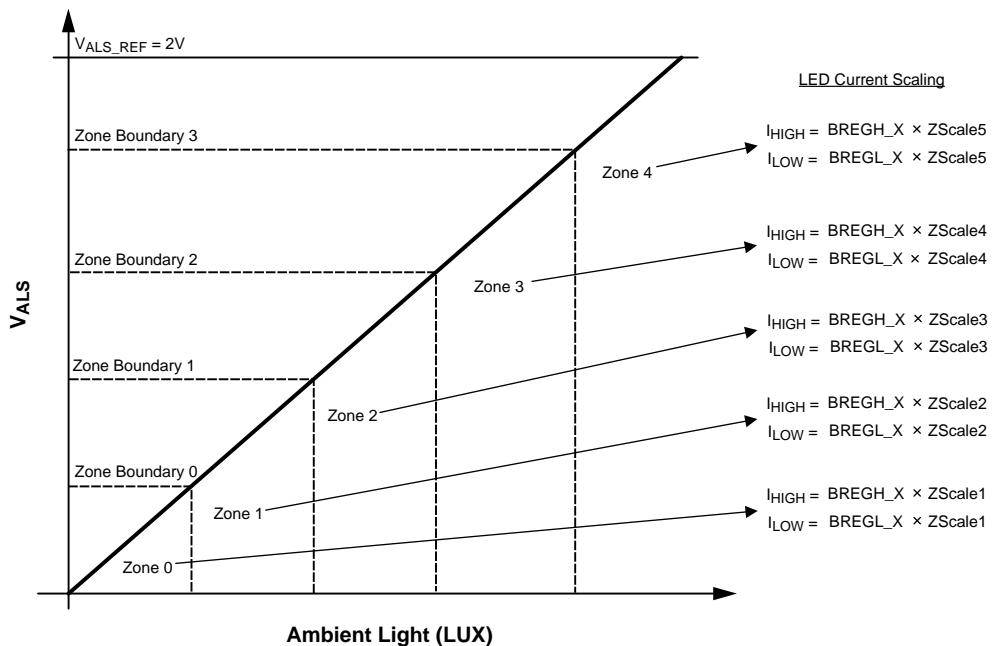

The LM3533 features Ambient Light Sensor (ALS) current control which allows the LED current to be automatically set based upon the received ambient light. To implement ambient light current control the LM3533 uses a 5 brightness zone implementation with 3 sets of Zone Targets.

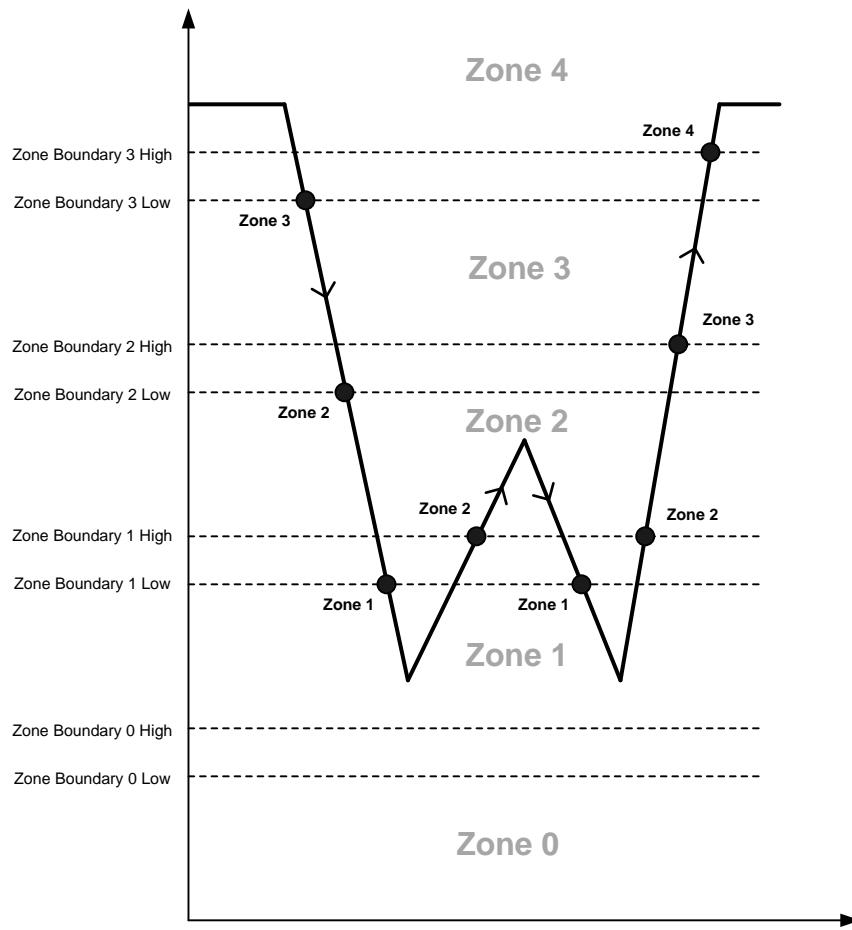

#### 7.4.7.1 ALS Brightness Zones (Zone Boundaries)

The LM3533 provides for a 5 brightness zone ambient light sensor interface. This allows for the LED current in any current sink to change based upon which zone the received ambient light falls into. The brightness zones are configured via 4 ALS Zone Boundary High and 4 ALS Zone Boundary Low Registers. Each Zone Boundary register is 8 bits with a full-scale voltage of 2 V. This gives a  $2\text{ V}/255 = 7.843\text{ mV}$  per bit. [Figure 26](#) shows the mapping from the ALS Brightness Zone to the target backlight current.

## Device Functional Modes (continued)

### 7.4.7.2 Zone Boundary Hysteresis

For each Zone Boundary there are two Zone Boundary Registers: a Zone Boundary High Register and a Zone Boundary Low Register (see [Table 30](#)). The difference between the Zone Boundary High and Zone Boundary Low Registers (for a specific zone) creates the hysteresis that is required to transition between zones. This hysteresis prevents the backlight current from oscillating between zones when the ALS voltage is close to a Zone Boundary Threshold. For Zone-to-Zone transitions the increasing ALS voltage must cross the Zone Boundary High Threshold in order to get into the next higher zone. Conversely, the ALS decreasing voltage must cross below the Zone Boundary Low Threshold in order to get into the next lower zone. [Figure 25](#) describes this Zone Boundary Hysteresis.

Figure 25. ALS Zone Boundary + Hysteresis <sup>(1)</sup>

### 7.4.7.3 Zone Target Registers (ALSM1, ALSM2, ALSM3)

For each brightness zone there is a programmable brightness target which is set via the ALS Zone Target Registers (see [Table 31](#), [Table 32](#), and [Table 33](#)). There are 3 sets of ALS Zone Target Registers (ALSM1, ALSM2, and ALSM3). The ALSM1 Zone Target Registers are dedicated to only Control Bank 1. ALSM2 and ALSM3 registers can be assigned to any of the Control Banks (B – F) (see [Table 8](#) and [Table 10](#)). Each of the Zone Target Registers consists of an 8-bit code which is a percentage of the programmed full-scale current. This percentage of full-scale current is dependent on the selected mapping mode. [Figure 26](#) details the mapping of the ALS Brightness Zone to the ALSM\_Zone Target Registers.

(1) The arrows indicate the direction of the ALS voltage.

## Device Functional Modes (continued)

**Figure 26. ALS Brightness Zone To Backlight Current Mapping**

### 7.4.7.4 PWM Input in ALS Mode

The PWM input can be enabled for any of the 5 Brightness Zones (see [Table 7](#)). This makes the brightness target for the PWM enabled zone have its current a function of the PWM input duty cycle, the full-scale current setting for that particular bank, and the brightness target for that particular zone.

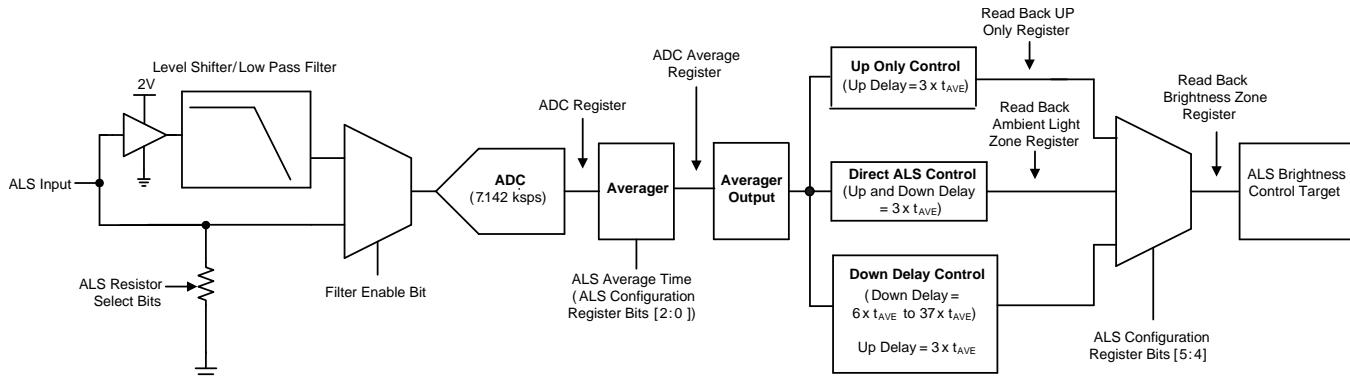

### 7.4.8 ALS Functional Blocks

[Figure 27](#) shows the functional block diagram of the LM3533 device ALS interface.

**Figure 27. ALS Block Diagram**

## Device Functional Modes (continued)

### 7.4.8.1 ALS Input

The ALS input is designed to connect to an analog or PWM output ambient light sensor. The ALS Configuration Register Bit [1] selects which type of sensor interface is used at the ALS input (see [Table 22](#)).

### 7.4.8.2 Analog Output Ambient Light Sensors (ALS Gain Setting Resistors)

With ALS Configuration Register bit [1] = 0, the ALS input is set for Analog Sensor mode. In this mode the LM3533 offers 128 programmable internal resistors at the ALS input (including a high-impedance option); see [Table 21](#). These resistors are designed to take the output of an analog ambient light sensor and convert it into a voltage. The value of the resistor selected is typically chosen such that the ALS input voltage is 2 V at the maximum ambient light (LUX) value. The sensed voltage at the ALS input is digitized by the LM3533's internal 8-bit ADC with a full-scale value (0xFF) corresponding to 2 V.

### 7.4.8.3 PWM Output Ambient Light Sensors (Internal Filtering)

With the ALS Configuration Register bit [1] = 1, the ALS input is set for PWM-Sensor mode. In this mode the LM3533 offers an internal level shifter and low-pass filter (ALS PWM Input mode). With this mode enabled the ALS input accepts logic level PWM signals and converts them into a 0-to-2-V analog voltage which is then filtered. This 0-to-2-V analog representation of the PWM signal is then applied to the internal 8-bit ADC, where 2 V is the full scale (code 0xFF). The internal filter has a corner frequency of 540 Hz and provides 51 dB of attenuation (355x) at a 10-kHz input frequency.

Because the internal ADC for the ambient light sensor utilizes an 8-bit ADC, the attenuation of the ALS input signal needs to be greater than 1/255 (1 LSB = 7.843 mV) in order to realize the full 8-bit range. This forces the frequency for the PWM signal at the ALS input to be around 6 kHz or greater. For slower moving signals an external RC filter may need to be combined with the Analog Sensor Mode (see [Application and Implementation](#)).

When the ALS input is set for ALS PWM Input Mode the internal ALS resistor setting is automatically set for high impedance, no matter what the setting in the ALS Select Register.

### 7.4.8.4 Internal 8-Bit ADC

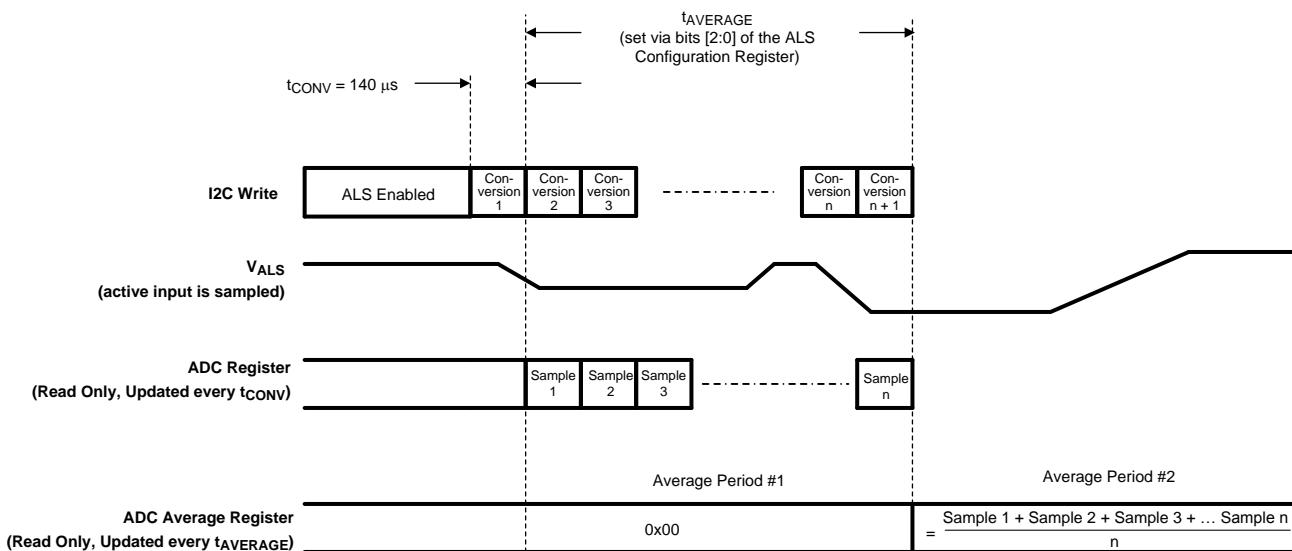

The LM3533 digitizes the ALS voltage using an internal 8-bit ADC. The ADC is active as long as the ALS enable bit is set. Once set, the ADC begins sampling and converting the voltage at the ALS input at 7.142 ksp. The ADC output can be read back via the ADC register (address 0x37). With the ALS enable bit set, the ADC register is updated every 140  $\mu$ s. [Figure 28](#) details the timing of the ADC.

Figure 28. ADC Timing

## Device Functional Modes (continued)

### 7.4.8.5 ALS Averager

Once digitized the output of the ADC is sent into the ALS averager. The averager computes the average of the number of samples taken over the programmed average period. The ALS average times are set via bits [5:3] in the ALS Configuration Register. The output of the ALS average can be read back via the ADC Average register (address 0x38). With the ALS Enable bit set, the ADC Average register is updated after each average period (see [Figure 28](#)). After every average period the Averager Output stores the information for which brightness zone the ALS input voltage resides in (see [Figure 27](#)).

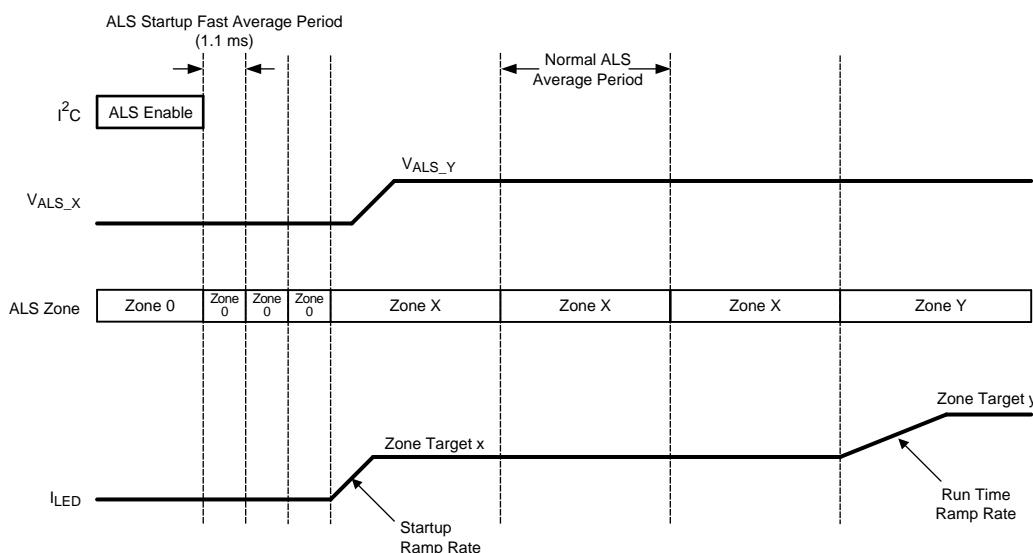

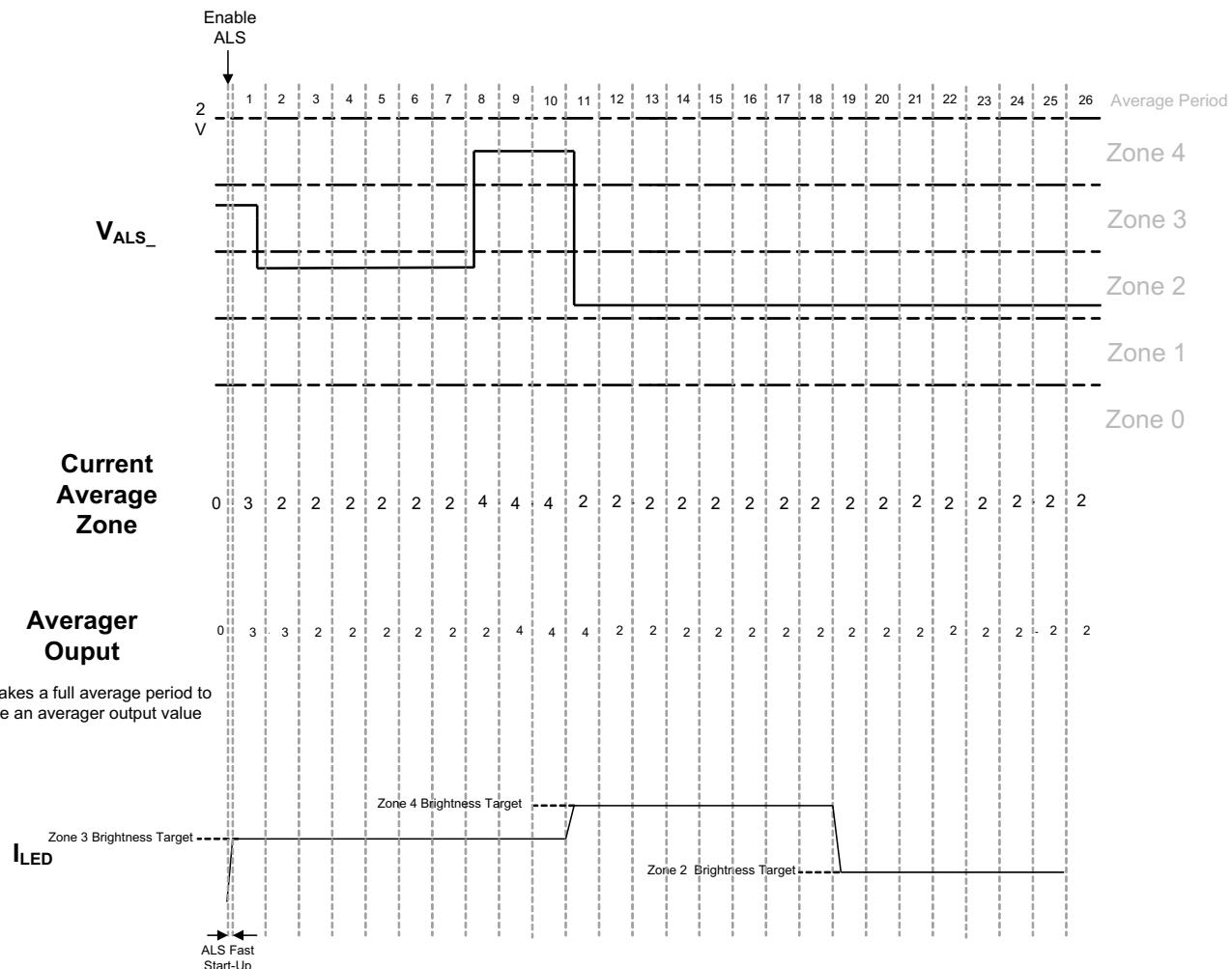

### 7.4.8.6 Initializing the ALS

On initial start-up of the ALS Interface, the Ambient Light Zone defaults to Zone 0. This allows the ALS to start off in a predictable state. The drawback is that Zone 0 is often not representative of the true ALS Brightness Zone, as the ALS input can get to its ambient light representative voltage much faster than the LED current is allowed to change. In order to avoid a multiple average time wait for the backlight current to get to its correct state, the LM3533 switches over to a fast average period (1.1 ms) during the ALS start-up. This quickly brings the ALS Brightness Zone (and the backlight current) to its correct setting (see [Figure 29](#)).

**Figure 29. ALS Start-up Sequence**

### 7.4.8.7 ALS Algorithms

There are three ALS algorithms that can be selected independently by each ALS Mapper (ALSM1, ALSM2, and ALSM3) (see [Table 23](#)). The ALS algorithms are: direct, up only, and down delay.

### 7.4.8.8 ALS Rules

For each algorithm, the ALS follows these basic rules:

1. For the ALS Interface to force a change in the backlight current (to a higher zone target), the averager output must have shown an increase for 3 consecutive average periods, or an increase and a remain at the new zone for 3 consecutive average periods.

2. For the ALS Interface to force a change in the backlight current (to a lower zone target), the averager output must have shown a decrease for 3 consecutive average periods, or a decrease and remain at the new zone for 3 consecutive average periods.

3. If condition 1 or 2 above is satisfied, and during the next average period the averager output changes again in the same direction as the last change, the LED current immediately changes at the beginning of the next average period.

## Device Functional Modes (continued)

4. If condition 1 or 2 above is satisfied, and the next average period shows no change in the average zone, or shows a change in the opposite direction, then the criteria in condition 1 or 2 must be satisfied again before the ALS interface can force a change in the backlight current.

5. The Averager Output (see [Figure 27](#)) contains the zone that is determined from the most recent full average period.

6. The ALS Interface only forces a change in the backlight current at the beginning of an average period.

7. When the ALS forces a change in the backlight current the change is to the brightness target pointed to by the zone in the Averager Output.

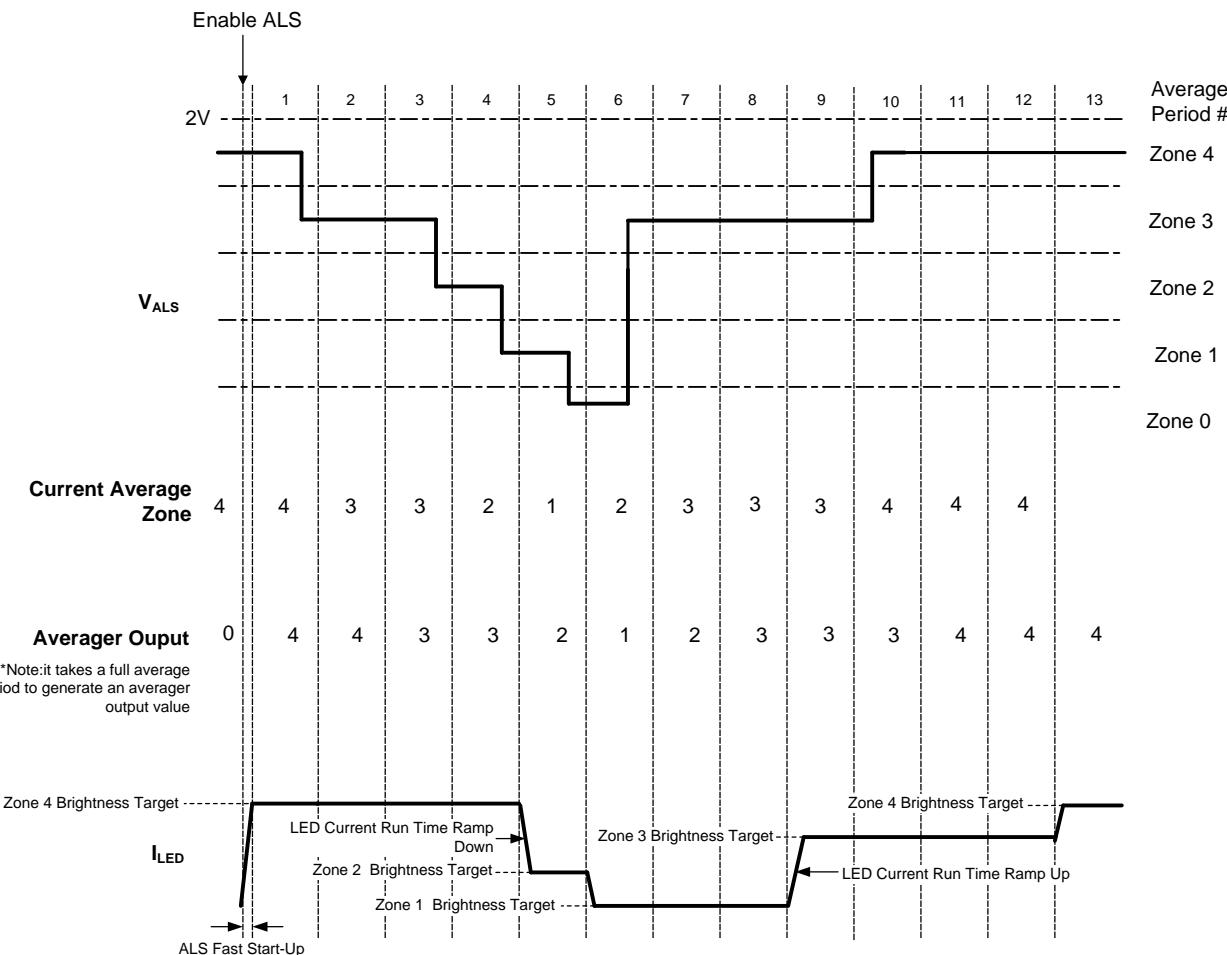

### 7.4.8.9 Direct ALS Control

In direct ALS control the LM3533 ALS Interface can force the backlight current to either a higher zone target or a lower zone target using the rules described in [ALS Rules](#). In the example of [Figure 30](#), the plot shows the ALS voltage, the current average zone which is the zone determined by averaging the ALS voltage in the current average period, the Averager Output which is the zone determined from the previous full average period, and the target backlight current that is controlled by the ALS Interface. The following steps detail the Direct ALS algorithm:

1. When the ALS is enabled the ALS fast start-up (1.1-ms average period) quickly brings the Averager Output to the correct zone. This takes 3 fast average periods or approximately 3.3ms.

2. The 1st average period the ALS voltage averages to Zone 4.

3. The 2nd average period the ALS voltage averages to Zone 3.

4. The 3rd average period the ALS voltage averages to Zone 0 and the Averager Output shows a change from Zone 4 to Zone 3.

5. The 4th average period the ALS voltage averages to Zone 2 and the Averager Output remains at its changed state of Zone 3.

6. The 5th average period the ALS voltage averages to Zone 1. The Averager Output shows a change from Zone 3 to Zone 2. Because this is the 3rd average period that the Averager Output has shown a change in the decreasing direction from the initial Zone 4, the backlight current is forced to change to the current Averager Output (Zone 2's) target current.

7. The 6th average period the ALS voltage averages to Zone 2. The Averager Output changes from Zone 2 to Zone 1. Because this is in the same direction as the previous change, the backlight current is forced to change to the current Averager Output (Zone 1's) target current.

8. The 7th average period the ALS voltage averages to Zone 3. The Averager Output changes from Zone 1 to Zone 2. Because this change is in the opposite direction from the previous change, the backlight current remains at Zone 1's target.

9. The 8th average period the ALS voltage averages to Zone 3. The Averager Output changes from Zone 2 to Zone 3.

10. The 9th average period the ALS voltage averages to Zone 3. The Averager Output remains at Zone 3. Because this is the 3rd average period that the Averager Output has shown a change in the increasing direction from the initial Zone 1, the backlight current is forced to change to the current Averager Output (Zone 3's) target current.

11. The 10th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 3.

12. The 11th average period the ALS voltage averages to Zone 4. The Averager Output changes to Zone 4.

13. The 12th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 4.

14. The 13th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 4. Because this is the 3rd average period that the Averager Output has shown a change in the increasing direction from the initial Zone 3, the backlight current is forced to change to the current Averager Output (Zone 4's) target current.

## Device Functional Modes (continued)

**Figure 30. Direct ALS Control**

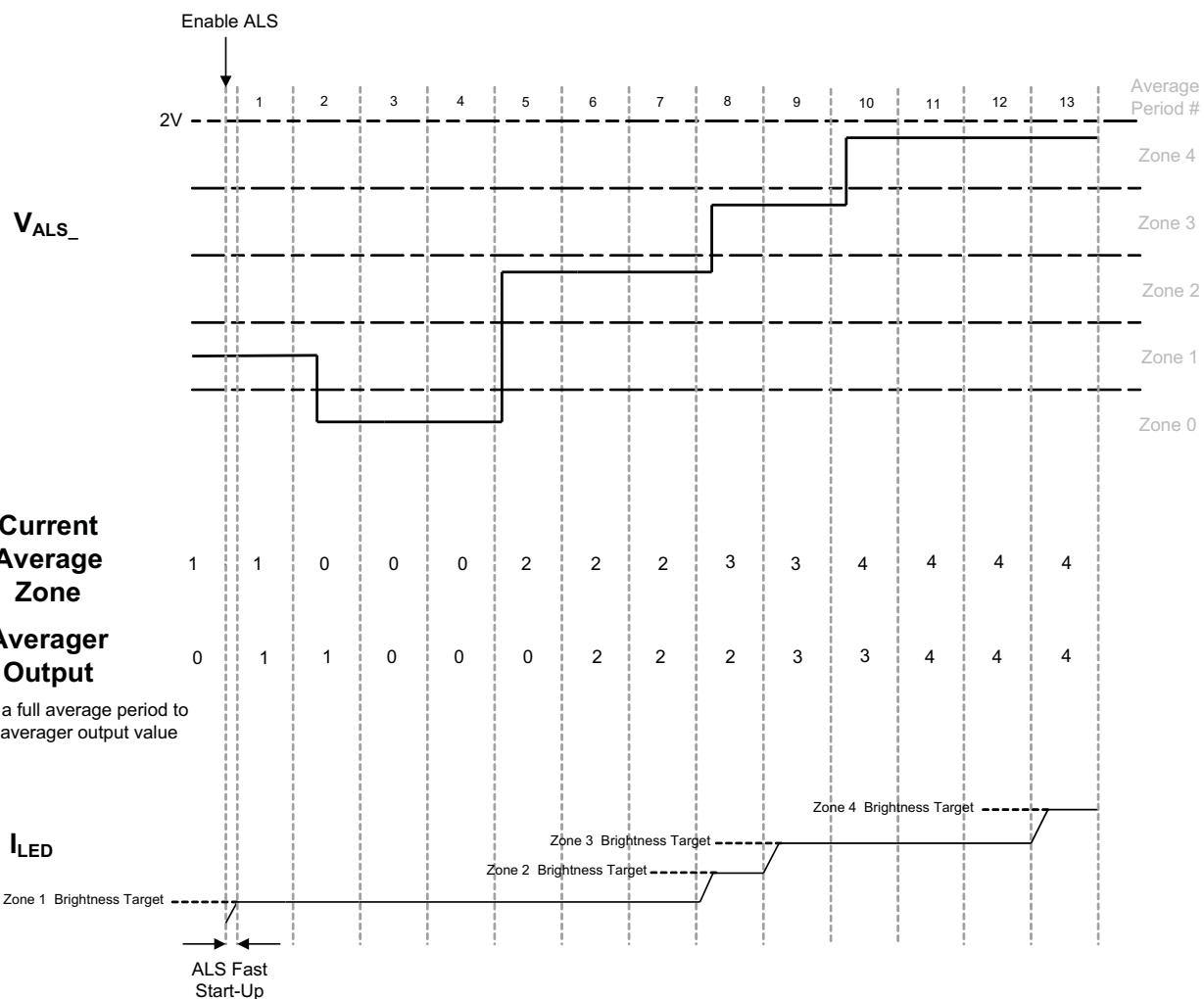

### 7.4.8.10 Up-Only Control

The ALS Up-Only Control algorithm is similar to Direct ALS Control except the ALS Interface can only program the backlight current to a higher zone target. Referring to [Figure 31](#):

1. When the ALS is enabled the ALS fast startup (1.1ms average period) quickly brings the Averager Output to the correct zone. This takes 3 fast average periods or approximately 3.3 ms.

2. The 1st average period the ALS voltage averages to Zone 1.

3. The 2nd average period the ALS voltage averages to Zone 0.

4. The 3rd average period the ALS voltage averages to Zone 0, and the Averager Output shows a change from Zone 1 to Zone 0.

5. The 4th average period the ALS voltage averages to Zone 2, and the Averager Output remains at its changed state of Zone 0.

6. The 5th average period the ALS voltage averages to Zone 2. The Averager Output remains at Zone 0. Because the Up Only algorithm is chosen the backlight current remains at the Zone 1 target even though this is the 3rd consecutive average period that the Averager Output has shown a change since the initial Zone 1.

7. The 6th average period the ALS voltage averages to Zone 2. The Averager Output changes from Zone 0 to Zone 2.

8. The 7th average period the ALS voltage averages to Zone 3. The Averager Output remains at Zone 2.

9. The 8th average period the ALS voltage averages to Zone 3. The Averager Output remains at Zone 2.

## Device Functional Modes (continued)

Because this is the 3rd average period that the Averager Output has shown a change in the up direction, the backlight current is forced to change to the current Averager Output (Zone 2's) target current.

10. The 9th average period the ALS voltage averages to Zone 3. The Averager Output changes from Zone 2 to Zone 3. Because this is a change in the increasing Zone direction, and is a consecutive change following a new backlight target current transition, the backlight current is again forced to change to the current Averager Output (Zone 3's) target current.

11. The 10th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 3.

12. The 11th average period the ALS voltage averages to Zone 4. The Averager Output changes to Zone 4.

13. The 12th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 4.

14. The 13th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 4. Because this is the 3rd average period that the Averager Output has shown a change in the increasing direction from the initial Zone 3, the backlight current is forced to change to the current Averager Output (Zone 4's) target current.

**Figure 31. ALS Up-Only Control**

## Device Functional Modes (continued)

### 7.4.8.11 Down-Delay Control

The Down-Delay algorithm uses all the same rules from [ALS Rules](#), except it provides for adding additional average period delays required for decreasing transitions of the Averager Output, before the LED current is programmed to a lower zone target current. The additional average period delays are programmed via the ALS Down Delay register. The register provides 32 settings for increasing the down delay from 3 extra (code 00000) up to 34 extra (code 11111). For example, if the down delay algorithm is enabled, and the ALS Down Delay register was programmed with 0x00 (3 extra delays), then the Averager Output would need to see 6 consecutive changes in decreasing Zones (or 6 consecutive average periods that changed and remained lower), before the backlight current was programmed to the lower zones target current. Referring to [Figure 32](#), assume that Down Delay is enabled, and the ALS Down Delay register is programmed with 0x02 (5 extra delays, or 8 average period total delays for downward changes in the backlight target current):

1. When the ALS is enabled the ALS fast startup (1.1ms average period) quickly brings the Averager Output to the correct zone. This takes 3 fast average periods or approximately 3.3 ms.

2. The first average period the ALS voltage averages to Zone 3.

3. The second average period the ALS voltage averages to Zone 2. The Averager Output remains at Zone 3.

4. The 3rd through 7th average period the ALS voltage averages to Zone 2, and the Averager Output stays at Zone 2.

5. The 8th average period the ALS voltage averages to Zone 4. The Averager Output remains at Zone 2.

6. The 9th and 10th average periods the ALS voltage averages to Zone 4. The Averager Output is at Zone 4. Because the Averager Output increased from Zone 2 to Zone 4 and the required Down Delay time was not met (8 average periods), the backlight current was never changed to the Zone 2's target current.

7. The 11th average period the ALS voltage averages to Zone 2. The Averager Output remains at Zone 4. Because this is the 3rd consecutive average period where the Averager Output has shown a change (increasing direction) since the change from Zone 2, the backlight current transitions to Zone 4's target current.

8. The 12th through 26th average periods the ALS voltage averages to Zone 2. The Averager Output remains at Zone 2. At the start of average period #19 the Averager Output has shown the required 8 average period delay from the initial change from Zone 4 to Zone 2. As a result the backlight current is programmed to Zone 2's target current.

## Device Functional Modes (continued)

**Figure 32. ALS Down-Delay Control**

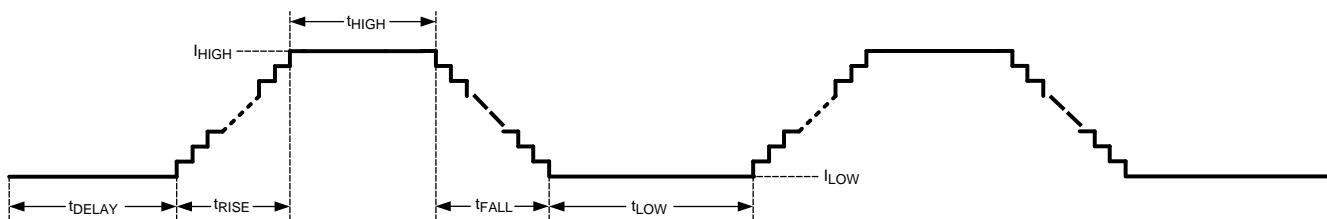

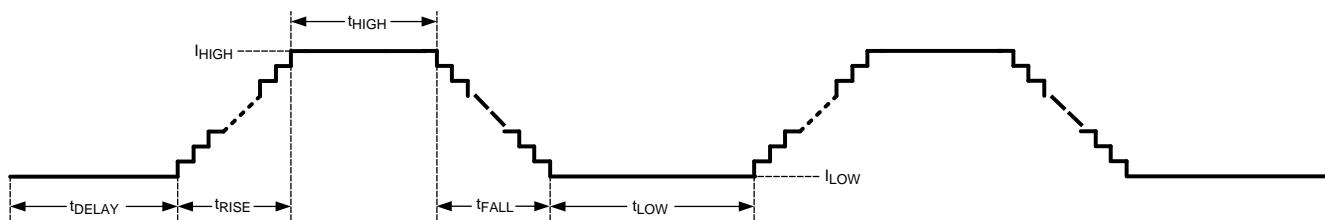

### 7.4.9 Pattern Generator

The LM3533 contains 4 programmable pattern generators (one for each low-voltage control bank). Each pattern generator has the ability to drive a unique programmable pattern. Each pattern generator has its own set of registers available for pattern programming. The programmable patterns are : delay time, rise time, fall time, high period, low period, high current and low current (see [Figure 33](#)).

**Figure 33. Pattern Generator Timing**

## Device Functional Modes (continued)

### 7.4.9.1 Delay Time

The Delay time ( $t_{DELAY}$ ) is the delay from when the pattern is enabled to when the LED current begins ramping up in the control bank's assigned current source(s). The pattern starts when bit [3] of the respective Control Bank Brightness Configuration Register is written high. There is one  $t_{DELAY}$  register for each pattern generator (4 total). The selectable times are programmed with the lower 6 bits of the  $t_{DELAY}$  registers. The times are split into 2 groups where codes 0x00 to 0x3C are short durations from 16.384 ms (code 0x00) up to 999.424 ms (code 0x3C) or 16.384 ms/bit. The higher codes (0x3D to 0x7F) select  $t_{DELAY}$  from 1130.496 ms up to 9781.248 ms, or 131.072 ms/bit (see [Table 35](#)).

### 7.4.9.2 Rise Time

The LED current rise time ( $t_{RISE}$ ) is the time the LED current takes to move from the low-current brightness level ( $I_{LOW}$ ) to the high-current brightness level ( $I_{HIGH}$ ). The rise time of the LED current ( $t_{RISE}$ ) is set via the Pattern Generator Rise Time Registers. Each Pattern Generator has its own rise-time register. There are 8 available rise-time settings (see [Table 42](#)).

### 7.4.9.3 Fall Time

The LED current fall time ( $t_{FALL}$ ) is the time the LED current takes to move from the high-current brightness level ( $I_{HIGH}$ ) to the low-current brightness level ( $I_{LOW}$ ). The fall time of the LED current ( $t_{FALL}$ ) is set via the Pattern Generator Fall Time Registers. Each Pattern Generator has its own fall-time register. There are 8 available fall-time settings (see [Table 43](#)).

### 7.4.9.4 High Period

The LED current high period ( $t_{HIGH}$ ) is the duration that the LED pattern spends at the high LED current set point ( $I_{HIGH}$ ). The  $t_{HIGH}$  times are programmed via the Pattern Generator  $t_{HIGH}$  Registers. The programmable times are broken into 2 groups. The first set (from code 0x00 to 0x3C) increases the  $t_{HIGH}$  time in steps of 16.384 ms. The second set (from code 0x3D to 0x7F) increases the  $t_{HIGH}$  time in steps of 131.072 ms (see [Table 39](#)).

### 7.4.9.5 Low Period

The LED current low period ( $t_{LOW}$ ) is the duration that the LED current spends at the low LED current set point ( $I_{LOW}$ ). The  $t_{LOW}$  times are programmed via one of the Pattern Generator  $t_{LOW}$  Registers. There are 256  $t_{LOW}$  settings and are broken into 3 groups of linearly increasing times. The first set (from code 0x00 to 0x3C) increases the  $t_{LOW}$  time in steps of 16.384ms. The second set (from code 0x3D to 0x7F) increases the  $t_{LOW}$  time in steps of 131.072 ms. The third set (from code 0x80 to 0xFF) increases the  $t_{LOW}$  time in steps of 524.288 ms (see [Table 37](#)).

### 7.4.9.6 Low-Level Brightness

The LED current low brightness level ( $I_{LOW}$ ) is the LED current set point that the pattern rests at during the  $t_{LOW}$  period. This level is set via the Pattern Generator Low Level Brightness Register(s). The brightness level has 8 bits of programmability.  $I_{LOW}$  is a function of the Control Banks full-scale Current setting, the code in the Pattern Generator Low-Level Brightness Register, the Mapping Mode selected, and the PWM input duty cycle (if PWM is enabled).

For exponential mapping  $I_{LOW}$  is:

$$I_{LOW} = I_{LED\_FULLSCALE} \times 0.85^{\left[ \frac{40 - (BREGL\_X+1)}{6.4} \right]} \times D_{PWM} \quad (3)$$

For linear mapping  $I_{LOW}$  is:

$$I_{LOW} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times BREGL\_X \times D_{PWM} \quad (4)$$

$BREGL\_X$  is the Pattern Generator Low-Level Brightness Register setting for the specific Control Bank (see [Table 40](#)).

## Device Functional Modes (continued)

### 7.4.9.7 High-Level Brightness

The LED current high brightness level ( $I_{HIGH}$ ) is the LED current set point that the pattern rests at during the  $t_{HIGH}$  period. This high-current level is set via the Control Banks Brightness Register (BREGCH to BREGFH). The brightness level has 8 bits of programmability.  $I_{HIGH}$  is a function of the Control Banks Full-Scale Current setting, the code in the Control Banks Brightness Register, the Mapping Mode selected, and the PWM input duty cycle (if PWM is enabled).

For exponential mapping  $I_{HIGH}$  is:

$$I_{LED} = I_{LED\_FULLSCALE} \times 0.862^{\left[ \frac{46.6 - \frac{(\text{Code}+1)}{5.5}}{255} \right]} \times D_{PWM} \quad (5)$$

For linear mapping  $I_{HIGH}$  is:

$$I_{HIGH} = I_{LED\_FULLSCALE} \times \frac{1}{255} \times BREGH\_X \times D_{PWM} \quad (6)$$

$BREGH\_X$  is the Control Banks Brightness Register setting for the specific Control Bank (see [Table 28](#)).

### 7.4.9.8 ALS Controlled Pattern Current

The current levels ( $I_{HIGH}$  and  $I_{LOW}$ ) of the programmable pattern can also be influenced by the ALS input. All the same ALS algorithms apply to the pattern generator current levels (Direct, Up Only, and Down Delay). The difference, however, for the ALS Controlled Pattern Current is that the pattern current is not changed to zone-defined brightness targets, but is changed by a scaled factor of the existing  $I_{HIGH}$  and  $I_{LOW}$  levels. These scaled factors are programmable in the ALS Pattern Scaler Registers (see [Table 17](#), [Table 18](#), and [Table 19](#)). Each defined brightness zone has a 4-bit (16-level) scale factor, which takes the programmed pattern current code and multiplies it by the programmed scale factor. This produce a new  $I_{HIGH}$  and  $I_{LOW}$  current level ranging from  $1/16 \times BREGH$  and  $1/16 \times BREGL$  up to  $16/16 \times BREGH$  and  $16/16 \times BREGL$  for each ALS zone (see [Figure 34](#)). There is only one set of scale factors for all the pattern generators.

Figure 34. ALS Controlled Pattern Current Scaling

## Device Functional Modes (continued)

For low-voltage control banks that do not have their pattern generator enabled, ALS current control is done via the ALS Mappers. Once a pattern generator is enabled, that particular Control Bank then uses the pattern scalers for ALS Current Control.

### 7.4.9.9 Interrupt Output Mode

When INT Mode is enabled (ALS Zone Information Register Bit [0] = 1), INT pin is configured as an interrupt output. INT is an open-drain output with an active pulldown of typically  $66\ \Omega$ . In INT Mode the INT output pulls low if the ALS interface is enabled, and the ALS input has changed zones. Reading back the ALS Zone Information while in this mode clears the INT output and reset it to its open-drain state.

## 7.4.10 Fault Flags/Protection Features

The LM3533 contains both an LED open and LED short fault detection. These fault detections are designed to be used in production level testing and not normal operation. For the fault flags to operate, they must be enabled via the LED Fault Enable Register (see [Table 47](#)).

### 7.4.10.1 Open LED String (HVLED)

An open LED string is detected when the voltage at the input to any active high-voltage current sink has fallen below 200 mV, and the boost output voltage has hit the OVP threshold. This test assumes that the HVLED string that is being detected for an open is connected to the LM3533 boost output (COUT+) (see [Table 13](#)). For an HVLED string not connected to the LM3533 boost output voltage, but connected to another voltage source, the boost output will not trigger the OVP flag. In this case an open LED string is not detected.

The procedure for detecting an open fault in the HVLED current sinks (provided they are connected to the boost output voltage) is:

- Apply power to the LM3533

- Enable Open Fault (Register 0xB2, bit [0] = 1)

- Configure HVLED1 and HVLED2 for LED string anode connected to COUT (Register 0x25, bits[1:0] = (1,1))

- Set Bank A full-scale current to 20.2 mA (Register 0x1F = 0x13)

- Set Bank A brightness to max (Register 0x40 = 0xFF)

- Set the startup ramp times to the fastest setting (Register 0x12 = 0x00)

- Assign HVLED1 and HVLED2 to Bank A (Register 0x10, Bits [1:0] = (0, 0))

- Enable Bank A (Register 0x27 Bit[0] = 1)

- Wait 4ms

- Read back bits[1:0] of register 0xB0. Bit [0] = 1 (HVLED1 open). Bit [1] = 1 (HVLED2 open)

- Disable all banks (Register 0x27 = 0x00)

### 7.4.10.2 Shorted LED String (HVLED)

The LM3533 features an LED short fault flag indicating one or more of the HVLED strings have experienced a short. The method for detecting a shorted HVLED strings is if the current sink is enabled and the string voltage ( $V_{OUT} - V_{HVLED1/2}$ ) falls to below ( $V_{IN} - 1\ V$ ). This test must be performed on one HVLED string at a time. Performing the test with both current sinks enabled can result in a faulty reading if one of the strings is shorted and the other is not.

The procedure for detecting a short in an HVLED string is:

- Apply power to the LM3533

- Enable Short Fault (Register 0xB2, bit [1] = 1)

- Enable Feedback on the HVLED Current Sinks (Register 0x25 = 0xFF)

- Set Bank A full-scale current to 20.2 mA (Register 0x1F = 0x13)

- Set Bank A brightness to max (Register 0x40 = 0xFF)

- Set the startup ramp times to the fastest setting (Register 0x12 = 0x00)

- Assign HVLED1 to Bank A (Register 0x10, Bits [1:0] = (1, 0))